Intel: Tri-Gate-Transistor macht alles besser

Intels Forschungsabteilung gelang eine bedeutende Weiterentwicklung bei neuartigen Transistoren. Diese so genannten Tri-Gate-Transistoren sollen sowohl die Leistungsfähigkeit als auch die Energieeffizienz von zukünftigen Mikroprozessoren steigern.

Planare - also flache, eindimensionale - Transistoren wurden in den 1950er Jahren entwickelt. Seitdem bilden sie den wichtigsten Baustein für Chips. Heute übliche Transistoren verfügen über lediglich eine flache Sperrschicht, das so genannte Gate, das quasi als Schalter zwischen den seitlichen Kontakten Source und Drain dient. Der Strom zwischen Source und Drain hängt dabei – unter Annahme einfacher Gleichungen – quadratisch von der am Gate anliegenden Steuerspannung ab. Durch die Steuerspannung am Gate entsteht ein elektrisches Feld im Isolator zwischen Gate und Transistor-Kanal. In Folge dessen sammeln sich Ladungsträger unter dem Gate, die einen leitenden Kanal zwischen Source und Drain ausbilden. (Stichworte: Gatekapazität, Ladungsträgerinversion, Inversionskapazität im Kanal)

Die Halbleiter-Technologie stößt jedoch immer weiter in den Bereich der Nanotechnologie vor - also in Strukturdimensionen kleiner als 100 Nanometer. Jenseits dieser Schwelle können einige Transistoren-Elemente aus dünnen Schichten von nur noch wenigen Atomlagen bestehen. Dadurch ergeben sich parasitäre Kurzkanaleffekte, in Folge deren auch bei ausgeschaltetem Transistor – also im Unterschwellenbereich der Gate-Spannung bevor sich ein leitender Kanal bilden sollte – ein Strom zwischen Drain und Source (Subthreshold-Leakage) fließt. Ehemals „flache“ Transistoren lassen sich nun dreidimensional aufbauen, um höhere Performance bei geringerem Stromverbrauch zu erreichen.

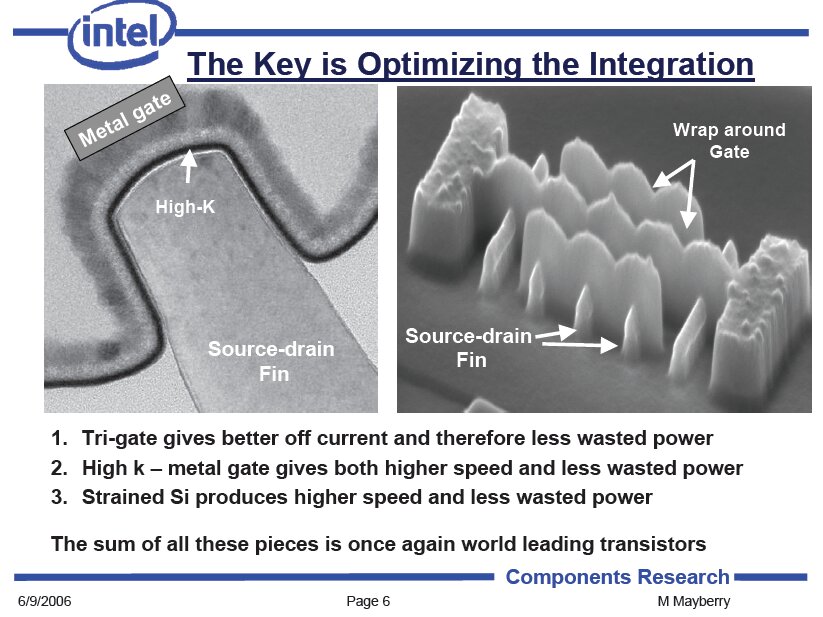

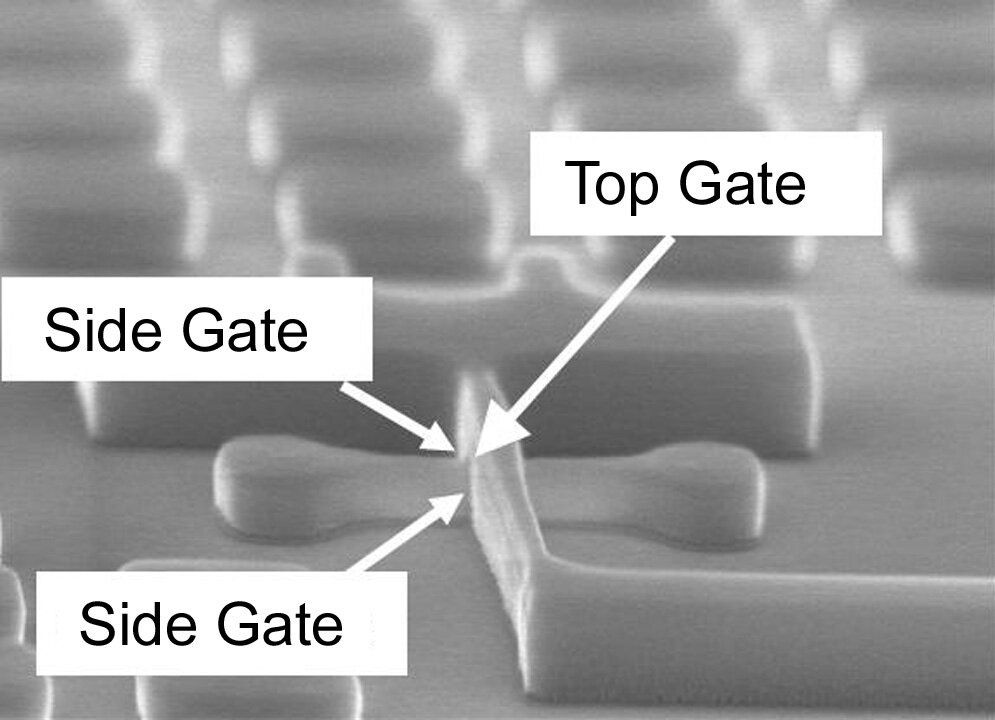

Intels Tri-Gate-Transistor nutzt eine solche dreidimensionale Struktur und verfügt über drei Gates. Die Struktur gleicht einem Plateau mit einer flachen Ebene oben und zwei vertikalen, steil abfallenden Flächen an den Seiten. Die elektrischen Signale fließen nicht nur entlang der Ebene, wie bei einem planaren Transistor, sondern auch entlang der beiden Seiten. Erste Tri-Gate-Transitoren stellte Intel schon 2002 im Forschungslabor her. Intel hat nun einen Weg gefunden, diese dreidimensionalen Transistoren gemeinsam mit anderen wichtigen Halbleiter-Technologien einzusetzen.

Intel führte erfolgreich drei wichtige Elemente zusammen: Die Tri-Gate-Geometrie für Transistoren, High-k-Gate-Dielektrika und die Technologie für gestrecktes Silizium. Damit haben wir wieder einmal bahnbrechende Transistor-Eigenschaften ermöglicht und unterstreichen Intels Führungsrolle, als Pionier neue Entwicklungen voran zu treiben.

Mike Mayberry, Vice President und Direktor der Komponentenentwicklung bei Intel

Tri-Gate-Transistoren spielen eine entscheidende Rolle in den Zukunftsplanungen von Intel, insbesondere bei der Steigerung der Energie-Effizienz. Sie produzieren deutlich geringere Leckströme: Im Ruhezustand fließen weniger unerwünschte Ströme durch den Transistor. Das reduziert die Wärmeentwicklung und den Stromverbrauch von Prozessoren. Im Vergleich zu heutigen Transistoren mit 65nm-Strukturen weisen die weiterentwickelten, integrierten Tri-Gate-Transistoren mit High-k-Gate-Dielektrika und Strained Silizium folgende Eigenschaften auf: Die um 35 Prozent geringere Schaltleistung (Switching Power) erlaubt einen 45 Prozent höheren Steuerstrom (Drive Current/Switching Speed) für einen schnelleren Einschaltvorgang und damit höhere Taktfrequenzen oder um den Faktor 50 geringere Ströme im ausgeschalteten Zustand (Off-Current) für niedrigen Stromverbrauch.

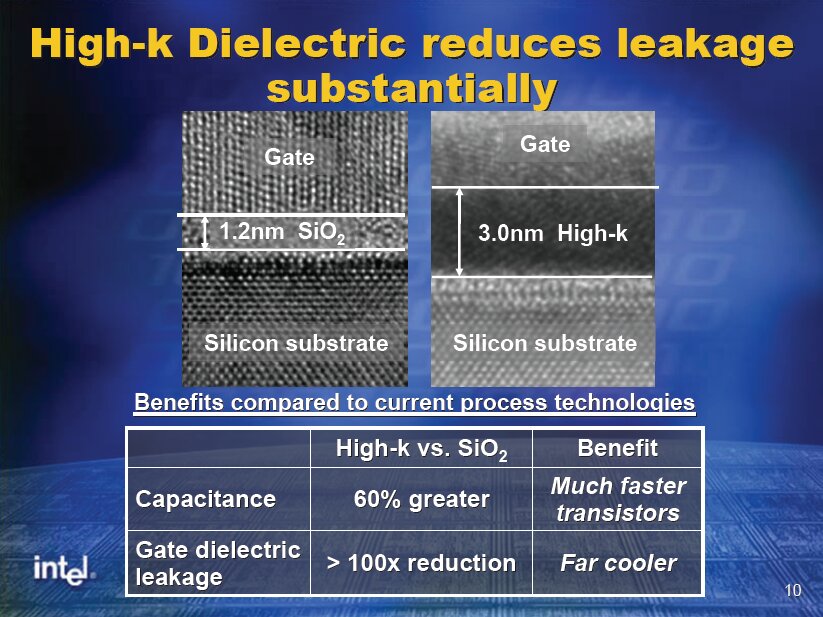

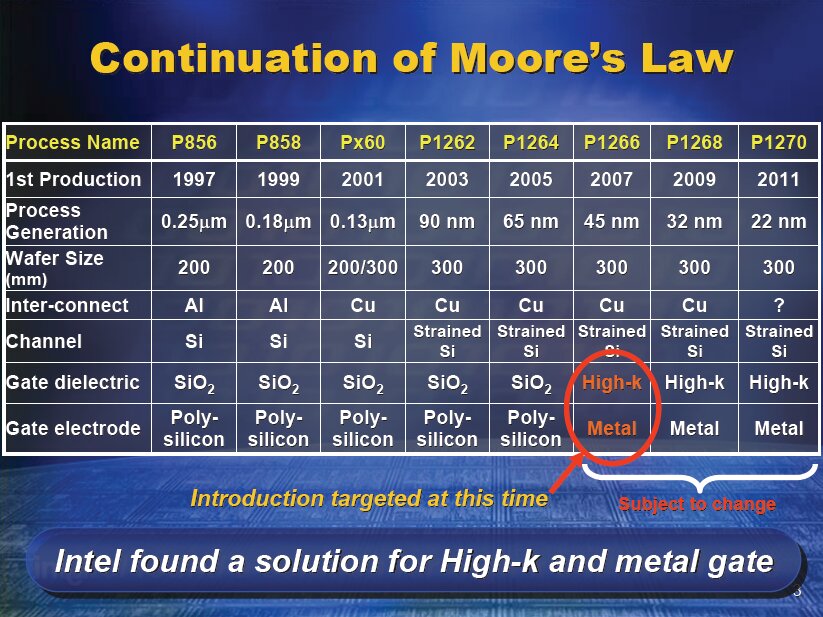

Die High-k-Gate-Dielektrika werden zusammen mit dem 45 nm-Prozess in der zweiten Jahreshälfte 2007 Einzug halten, die bei TSMC bereits jetzt zur Fertigung von Grafikchips von ATi und nVidia genutzt werden. Das High-k-Gate-Dielektrikum dient dabei als Isolator zwischen dem Gate-Kontakt und dem Kanal zwischen Source und Drain. Derzeit – d.h. auch beim 65 nm-Prozess – kommt als Isolator simples Siliziumoxid (SiO2) zum Einsatz, das bei 1,2 nm Oxid-Dicke aufgrund von Tunneleffekten zunehmend seine isolierenden Eigenschaften verliert. Mit seiner Dielektrizitätskonstante k (im deutschen eigentlich Epsilon) muss die Oxid-Dicke zu Gunsten schneller Transistoren jedoch kleiner werden. Denn je dünner, desto größer die Oxidkapazität und damit auch die gegenüberliegende Inversionskapazität im Kanal zwischen Source und Drain. Je größer diese Kapazität, desto größer ist der Strom, der durch den Transistor fließen kann und desto schneller kann er (an ihn angeschlossene Gates) schalten.

Die Gatekapazität lässt sich auch vergrößern, indem Isolationsmaterial mit einer höheren Dielektrizität genutzt wird. Bei Material mit entsprechenden hohen Konstanten kann darüber hinaus die Dicke des Oxids vergrößert werden, um die – insbesondere beim 90 nm Prozess (und darunter) – überaus störende Gate-Leakage deutlich zu reduzieren

Als technische Option waren Tri-Gate-Transistoren bei Intel ursprünglich im Zuge des kommenden 45 nm-Prozesses im Gespräch. Hierzu Christian Anderka, Pressesprecher bei Intel Deutschland:

Wir sind bemüht solche Techniken so spät wie möglich einzuführen, sofern andere kostengünstigere Optimierungen die gewünschten Eigenschaften bringen. Insofern ist es als Erfolg zu werten, wenn wir Tri-Gate nicht so schnell brauchen.

Christian Anderka, Pressesprecher bei Intel Deutschland

In der Tat scheint der in der zweiten Hälfte 2007 kommende Wechsel auf 45 nm-Strukturen auch ohne Tri-Gate gut auskommen zu können. So hat Mark Bohr im Rahmen der Ankündigung dieser Fertigungstechnologie bekannt gegeben, dass hier die Schaltleistung (Switching Power) im Vergleich zu 65 nm um über 30 Prozent gesenkt, der Steuerstrom (Drive Current/Switching Speed) um 20 Prozent gesteigert und die Leakage-Power um den Faktor 5 reduziert werden konnten. Diese Werte sind vor allem auf den Einsatz von High-k zurückzuführen.

Intel wird heute, am 13. Juni 2006 auf dem VLSI Technology Symposium in Honolulu, Hawaii, ein Whitepaper zu seinen Forschungen zum Tri-Gate-Transitor vorstellen. Man geht davon aus, Tri-Gate-Transistoren mit dem Prozesswechsel auf 32 nm (P1268) im Jahr 2009, oder 2011 mit 22 nm (P1270) einsetzen zu können, sofern sich keine günstigeren Alternativen ergeben.

Ach Übrigens: Auch aus 65 nm ist die Luft noch nicht raus. Im Rahmen des Intel Developer Forum Fall 2005 hat der Halbleiterriese einen Low-Power-Prozess (P1265) angekündigt, der die Leckströme im Vergleich zum derzeit eingesetzten P1265 – so die genaue Bezeichnung des Prozesses – um den Faktor 1000 senkt. Erste Produkte dieses Fertigungsprozesses dürfen mit Spannung erwartet werden.