AMD mit Stacked Memory und PIM bei Zukunfts-APUs

Bekanntlich plant AMD schon länger Prozessoren und vor allem APUs mit sogenanntem High Bandwidth Memory (HBM) zu kombinieren, um einen höheren Speicherdurchsatz zu erzielen. Ein Dokument zu AMDs „Fastforward Project“ gibt weitere Details zu diesem Vorhaben preis.

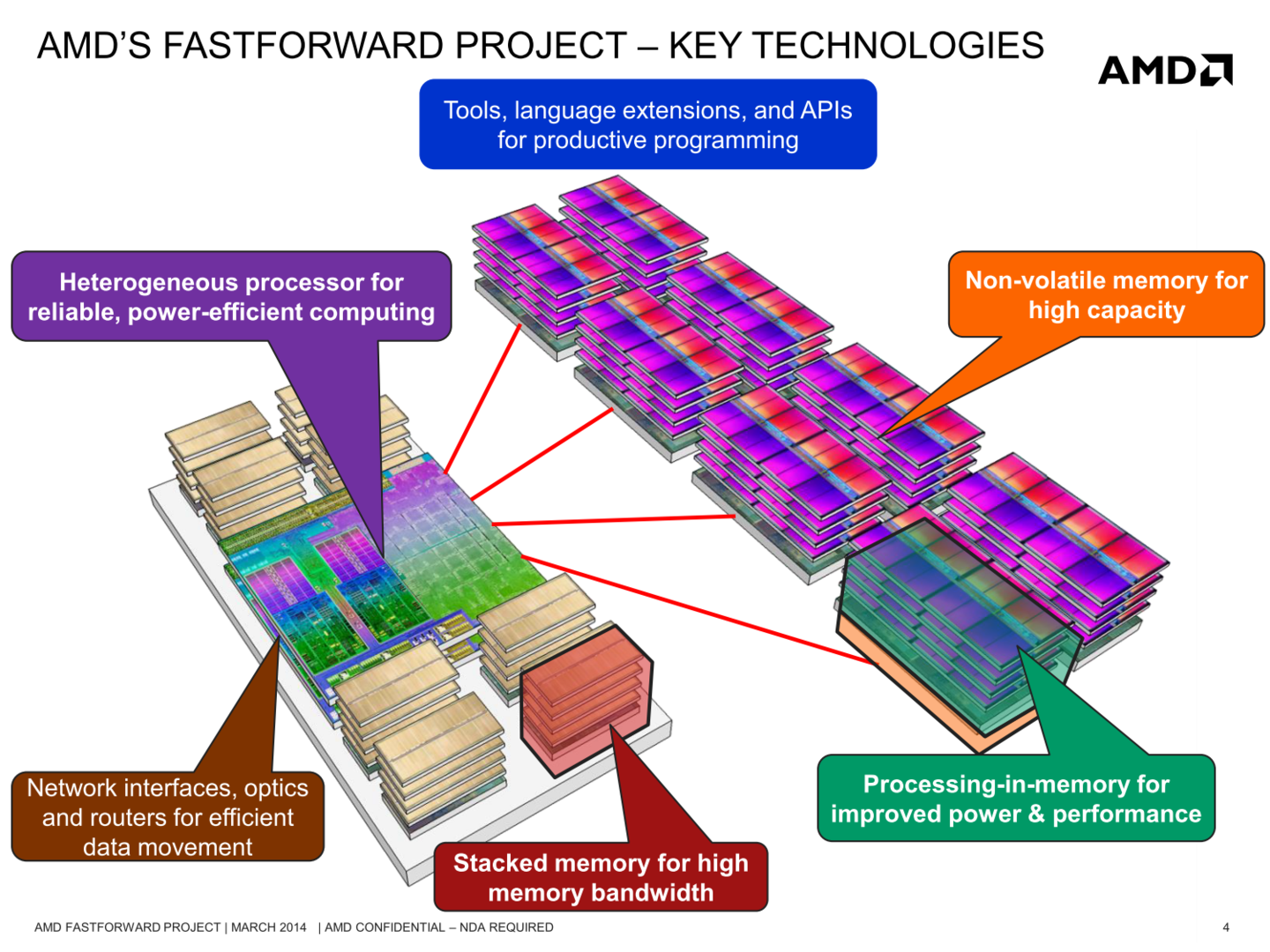

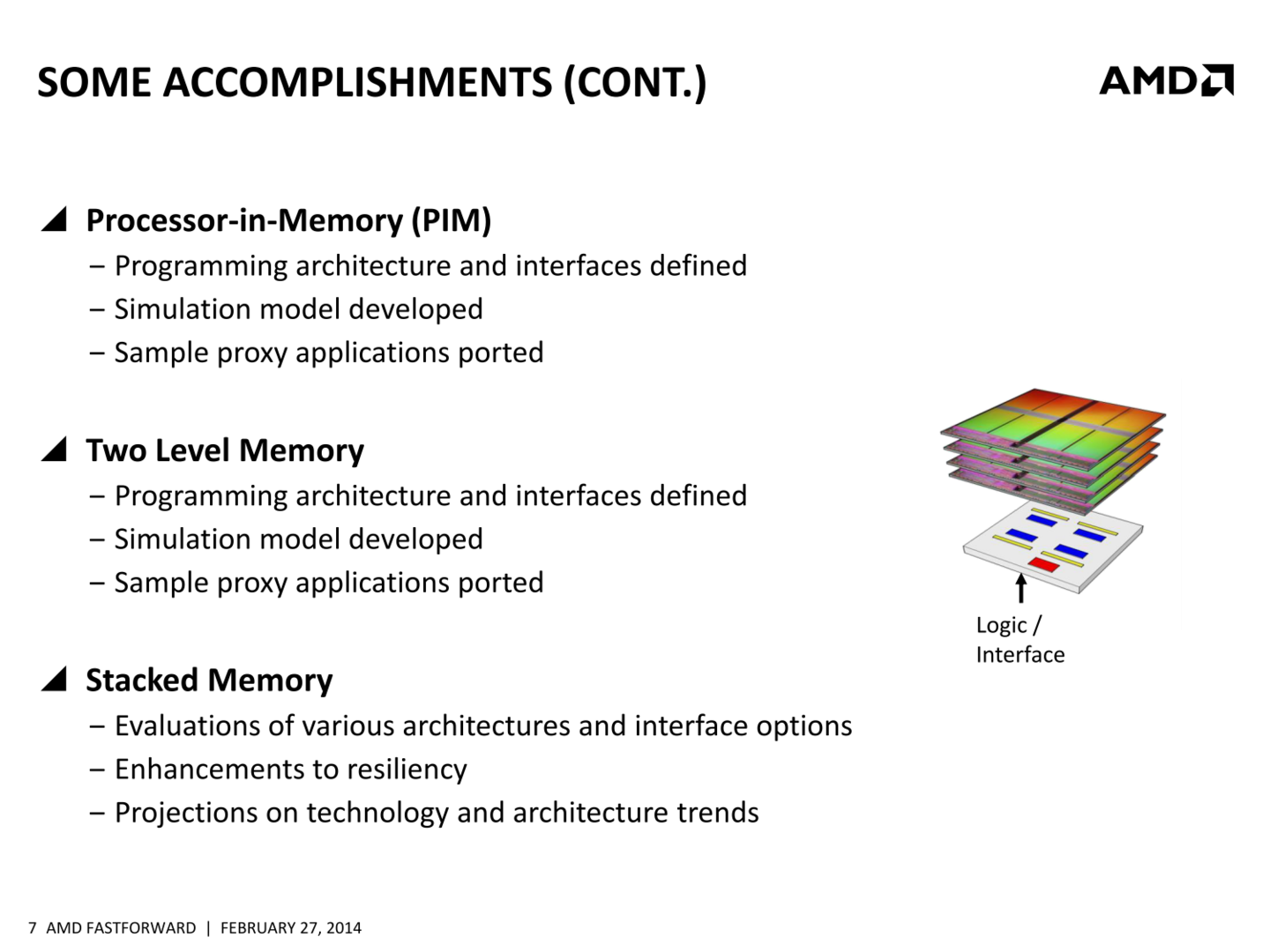

Das Dokument (PDF) stammt bereits aus dem Februar 2014, ist jedoch erst jetzt in den Fokus der Medien geraten. Die Präsentation beschreibt AMDs Ansätze zur Entwicklung neuer Techniken für künftige Exascale-Systeme. Neben der Heterogeneous System Architecture (HSA), die ein effizienteres Zusammenspiel von CPU und GPU ermöglichen soll, steht der Einsatz neuer Speichertechniken im Fokus.

Eine Folie zeigt unter anderem den „Stapelspeicher“ (stacked memory), der direkt auf dem APU-Package, aber neben dem Die des Prozessors unterkommen soll. Vor einigen Wochen waren Gerüchte aufgetaucht, dass bereits die für 2015 erwartete „Carrizo“-APU über Stacked DRAM respektive HBM-Speicher verfügen wird. Wenig später tauchten jedoch weitere Details zu „Carrizo“ auf, bei denen vom neuen Speicher keine Rede war. Es bleibt also abzuwarten, wann die ersten AMD-APUs mit HBM-Speicher auf den Markt kommen werden.

Außerdem steht die Technik Processor-in-Memory (PIM) im Fokus der AMD-Forscher. Das technisch aufwendigere Konzept dahinter sieht die Unterbringung von (DRAM-)Speicher direkt im Prozessor-Die vor, was durch kürzere Wege Latenzen verringern und die Speicherbandbreite anheben soll. Diesen Ansatz verfolgte zum Beispiel bereits das Berkeley IRAM project.

Hinter Fastforward verbirgt sich ein US-Förderprogramm mit dem Ziel, die Entwicklung von Hard- und Software-Technologien für künftige Exascale-Supercomputer voranzutreiben. Schon 2012 erhielten unter anderem AMD, IBM, Intel und Nvidia Forschungsgelder in zweistelliger Millionenhöhe im Rahmen der Initiative. Die Themen Speicherdurchsatz und Parallelisierung stehen auch bei Intels Forschungen auf dem Weg zu effizienteren Supercomputern hoch im Kurs.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!