3D-NAND: Micron erhöht auf 232 Layer und QLC-Kapazität mit TLC

Im Layer-Rennen hat Micron die Nase vorn: Schon Ende des Jahres will der Speicherhersteller die Produktion des neuen 232-Layer-3D-NAND beginnen, der jetzt erstmals vorgestellt wurde. Als TLC-Variante wird 1 Terabit (128 GB) pro Die geboten; doppelt so viel wie beim 176-Layer-Vorgänger und genauso viel wie bei aktuellem QLC-NAND.

Die Anzahl der Layer, also der mit Speicherzellen bestückten Ebenen von 3D-NAND-Flashspeicher, sagt allein noch nicht, wie hoch die Flächendichte ausfällt und auch nicht wie gut der NAND bei Kosten, Leistung oder Haltbarkeit dasteht. So viel sei vorweg gesagt.

Micron stapelt hoch

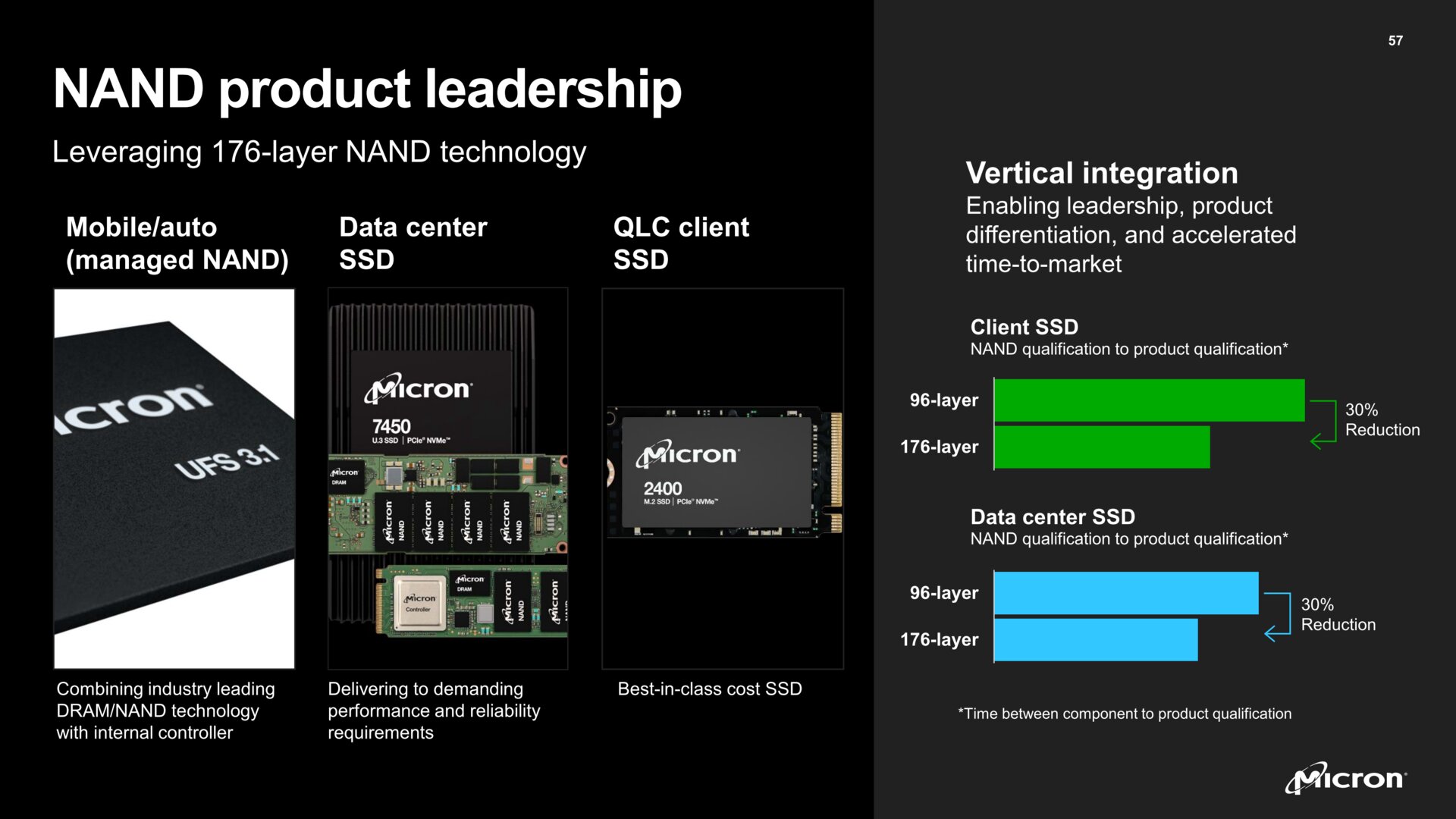

Dennoch hat Micron beim Stapeln der Layer derzeit die Nase vorn und hatte bereits im November 2020 den ersten 176-Layer-NAND der Branche präsentiert, der auf Microns eigener Replacement-Gate-Architektur basiert. Micron warb seinerzeit mit einem 30 Prozent kleineren Die als bei der Konkurrenz und versprach ordentliche Leistungssteigerungen. In der Tat konnte Microns 176-Layer-TLC-NAND die bereits schnellen SSDs mit Phison-E18-Controller noch einmal beschleunigen – die Kombination ist auf Produkten wie Seagate 530 SSD (Test) oder Corsair MP600 Pro XT (Test) in Benchmarks nur selten zu schlagen.

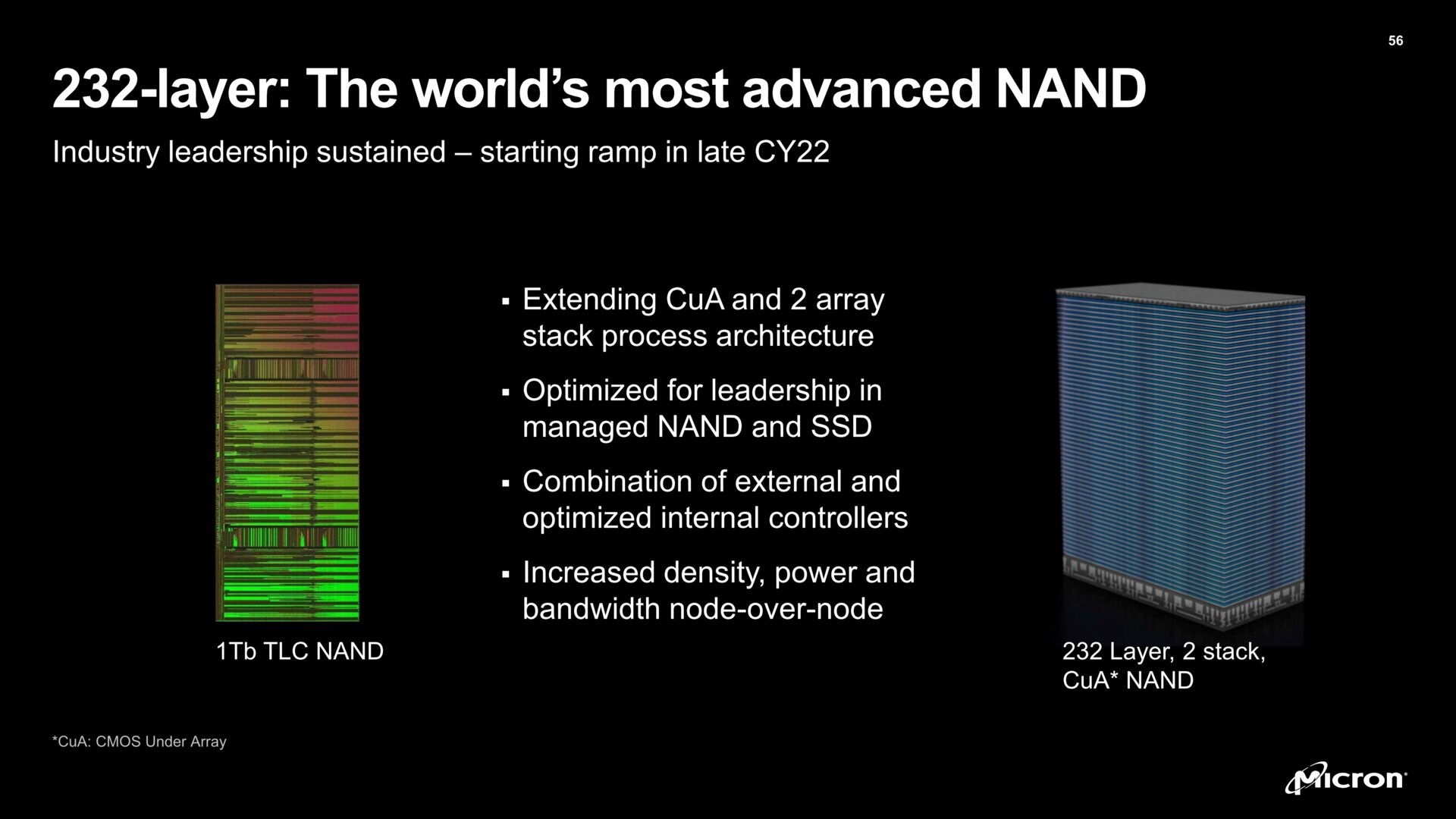

Jetzt nutzte Micron den Investor Day, um die nächste Generation vorzustellen. Diese verfügt über 232 Layer und soll schon ab Ende 2022 gefertigt werden. Hohe Stückzahlen sind aber wohl erst für das kommende Jahr zu erwarten.

Erneut setzt Micron auf zwei übereinander gesetzte Layer-Türme (Array oder String Stacking), womit einer davon aus 116 Layern bestehen muss. Beim 176-Layer-NAND kommen entsprechend zwei 88-Layer-Türme zum Einsatz. Ob Micron die Dicke der Layer nochmals reduzieren konnte, ist nicht bekannt. Dass die Logikschaltkreise in eigener Ebene unter den Speicherschichten sitzen (CMOS under Array, CuA), um Fläche zu sparen, ist längst gängige Praxis.

Wie groß oder wie hoch der 232-Layer-NAND ausfällt, hat Micron nicht verraten. Allerdings bietet ein TLC-Chip mit 3 Bit pro Speicherzelle eine hohe Speicherkapazität von 1 Tbit oder umgerechnet 128 GByte. Dies war zuvor nur mit QLC-NAND mit 4 Bit pro Speicherzelle erreicht worden, der langsamer und weniger haltbar ist.

Es bleibt abzuwarten, ob Micron wie schon bei der 176-Layer-Generation später eine QLC-Variante des 232-Layer-NAND folgen lässt, die entweder noch mehr Speicherplatz pro Die bietet oder aber deutlich kleiner ausfällt. In jedem Fall würde die Speicherdichte nochmals steigen. Konkrete Zahlen zu dieser nennt Micron aber bei der TLC-Version vorerst nicht. Und so bleibt unklar, wie hoch die genannten Verbesserungen bei Dichte, Energiebedarf und Durchsatz letztlich ausfallen.

SSDs mit eigenen und externen Controllern

Die ersten SSDs mit 232-Layer-NAND sind im kommenden Jahr zu erwarten. Dabei wird Micron erneut eigene Lösungen mit eigenen Controllern und Lösungen von Partnern mit Controllern anderer Hersteller ermöglichen. Im Consumer-Bereich bietet Micron SSDs unter der Markentochter Crucial an. Jüngstes Beispiel ist die Crucial P5 Plus (Test) mit Micron-Controller und Micron-176L-TLC-NAND. Mit dieser gelang dem Hersteller wieder der Anschluss an die SSD-Spitze. Allerdings erweisen sich, wie oben schon angesprochen, die Lösungen mit Phison-E18-Controller und gleichem NAND als noch schneller.

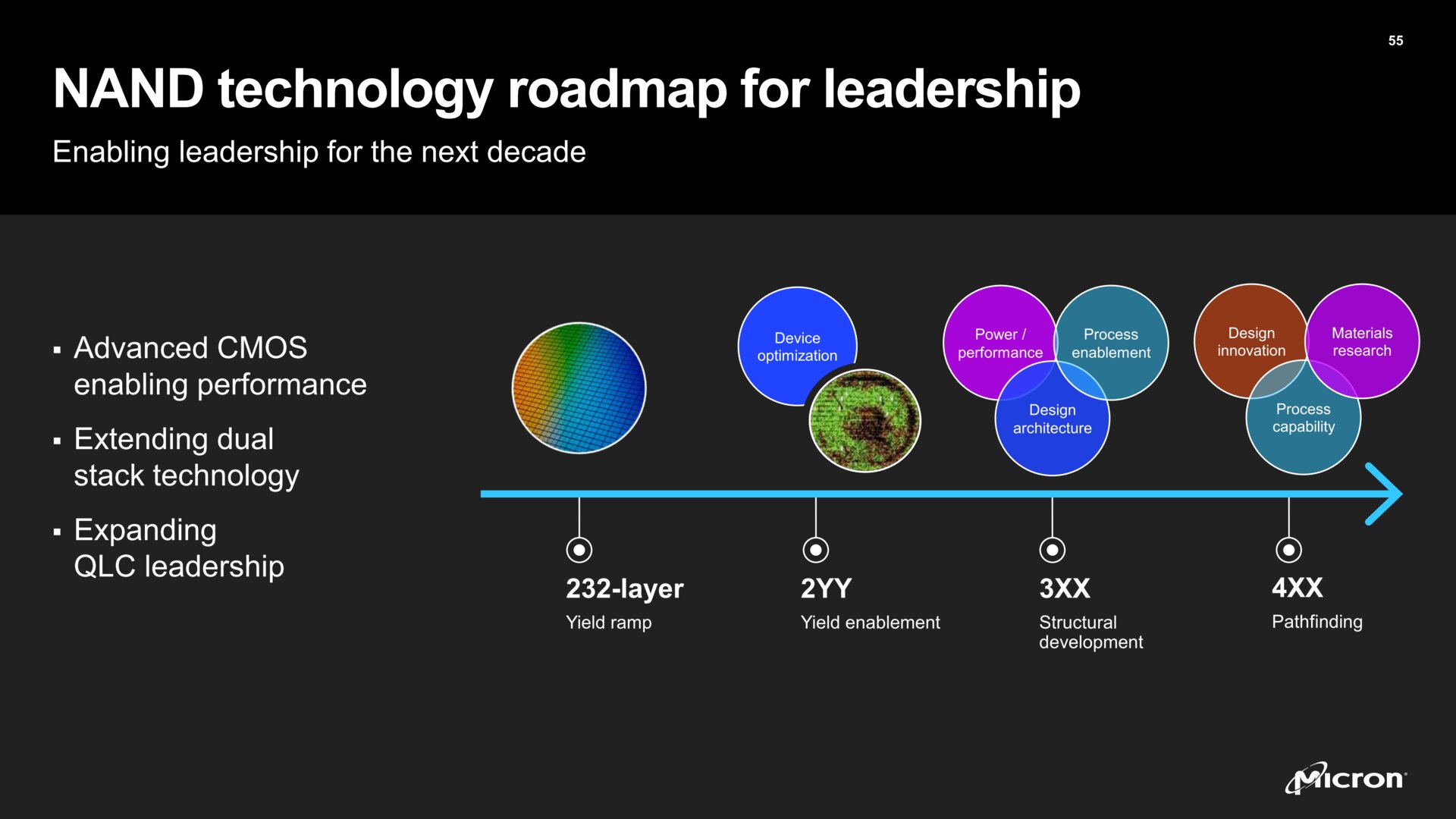

Microns ambitionierte Roadmap für die nächste Dekade sieht erst für spätere Generationen mit mehr als 300 oder 400 Layern wieder größere Änderungen an Architektur und Design vor. Demnach ist die bisherige Architektur gut skalierbar für noch mehr Zellschichten.