Intel 4 mit PowerVia: Testchip mit Meteor-Lake-E-Kernen und neuer Stromversorgung

Blue Sky Creek heißt Intels Testchip auf Basis von Meteor-Lake-E-Cores in Next-Gen-Fertigung „Intel 4“ mit neuartiger Stromversorgung PowerVia. Intel will auf dieser Basis im Idealfall zwei Jahre vor der Konkurrenz erste Produkte liefern – mit Arrow Lake als erstem Serienprodukt. Die ersten Details klingen vielversprechend.

BSPD und GAA gehören die Zukunft

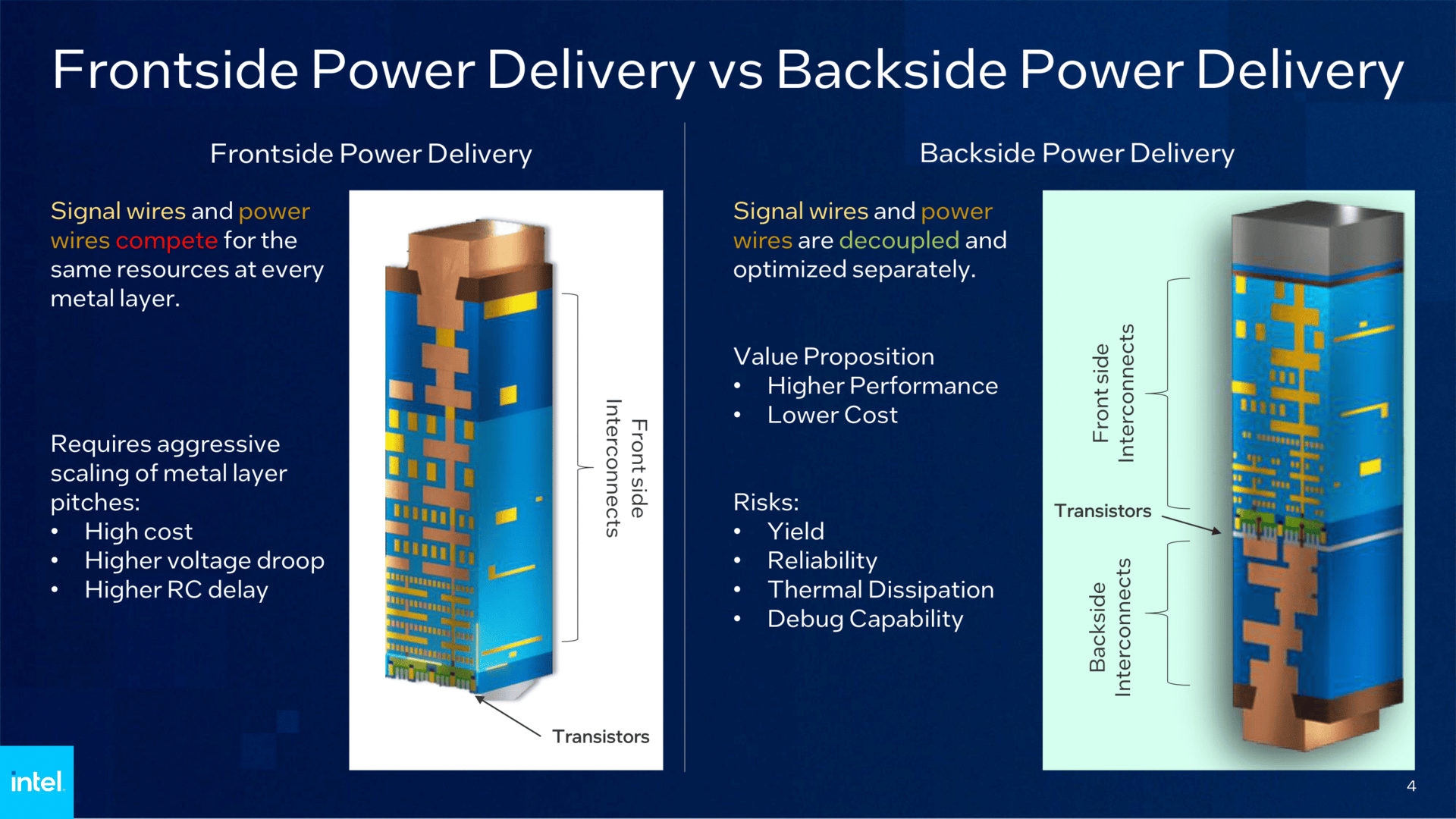

Backside Power Delivery (BSPD) heißt bei Intel PowerVia. Intels eigene Umsetzung der Technologie soll sich dabei etwas vom Original unterscheiden, nicht nur der Name sei ein anderer. Die grundlegende Technik der rückseitigen Stromversorgung von Transistoren ist wiederum keine exklusive Entwicklung, sie steht bei jeder Firma auf der Roadmap. Intel scheint hier jedoch am weitesten fortgeschritten oder spricht am offensivsten darüber.

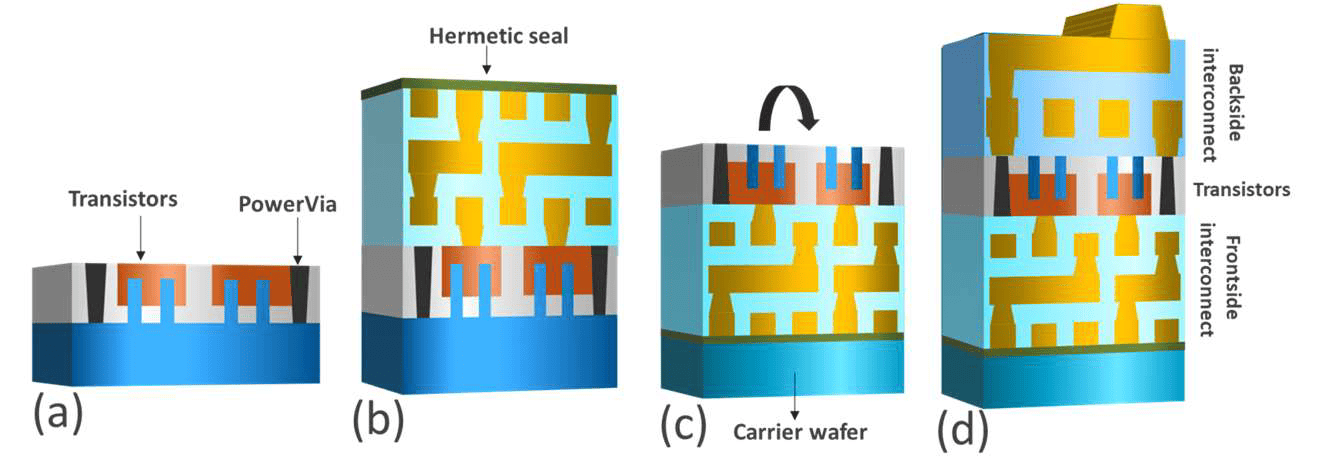

Zum VLSI-Symposium hat Intel erste Details zu aktuellen Testchips preisgegeben, die zeigen, wie quasi alle stromführenden Verbindungen von der Front- auf die Rückseite gelegt werden – kombiniert mit zusätzlichen Kniffen. Denn die „Stromleitungen“ streiten sich aktuell mit den Signalleitungen um den Platz in den Metal-Layern zwischen den Transistoren. Entkoppelt man beides, ergeben sich diverse Vorteile, aber auch Herausforderungen.

Grundlage ist Intel 4 mit hohem EUV-Anteil

Die Grundlage für die Entzweiung ist die exzessive Nutzung von EUV-Lithografie, die Intel bekanntlich erst mit Intel 4, der eigenen 7-nm-Fertigung, großflächig einführen wird. Mittels PowerVia soll mehr Strom von der Rückseite für die auch in Zukunft weiter schrumpfenden Transistoren bereitgestellt werden. Unterm Strich bringt das mehr Leistung, vor allem im High-Performance-Bereich, erklärte Intel in einem Pressegespräch vorab.

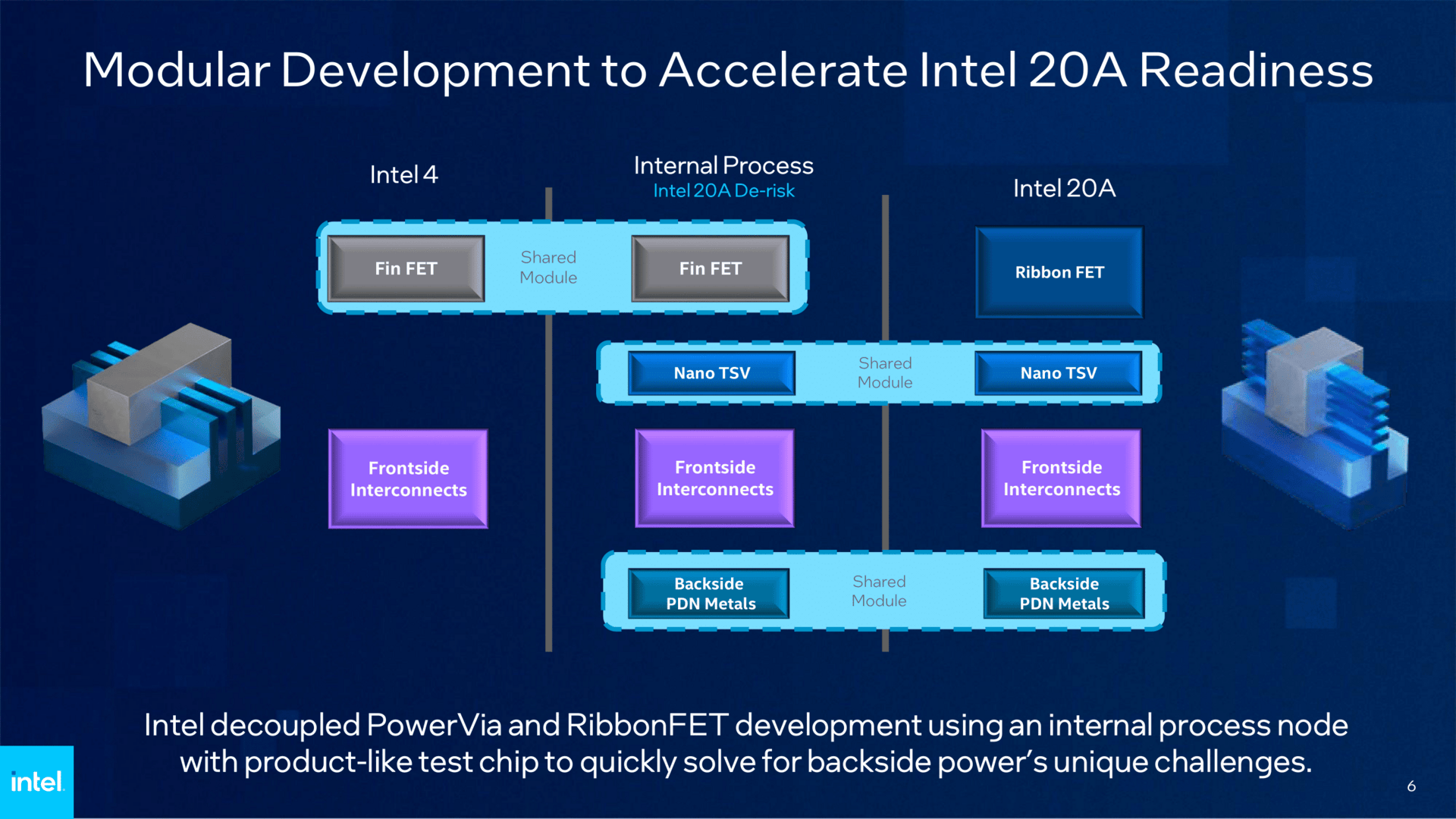

Der funktionsfähige Testchip wurde auf Basis von Intel 4 aufgelegt, also jenem Prozess, der mit Intel Meteor Lake eingeführt werden wird. Intern wurde dieser für den Testchip allerdings modifiziert und mit PowerVia kombiniert, der Weg zu Intel 20A so geebnet. Bei Intel gibt es dafür mehrere Arbeitsgruppen, PowerVia ist die eine, RibbonFET, wie Intel die Next-Gen-Fertigung rund um Gate all around (GAA) nennt, ist eine andere.

Beide Technologien werden parallel entwickelt und erst am Ende kombiniert genutzt. Hier hat Intel aus dem Desaster in der 10-nm-Fertigung gelernt, als der Hersteller viel zu viele Neuerungen auf einmal wollte und in der Konsequenz über Jahre keinen funktionsfähigen Prozess vorweisen konnte.

Vom Siliziumwafer bleibt am Ende kaum etwas übrig

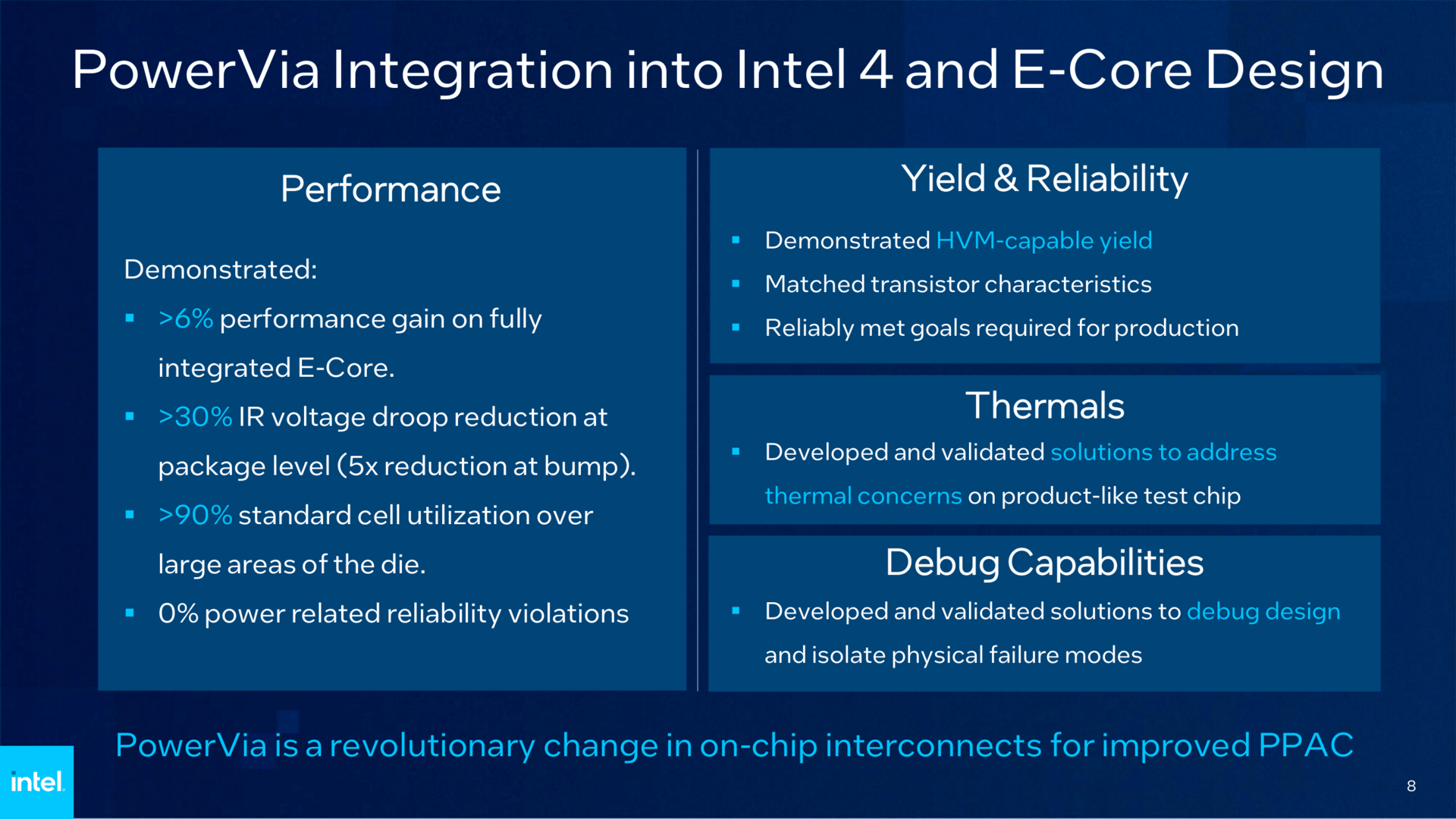

Die Produktion der Testchips beginnt wie die normaler Chips, allerdings mit einigen Nano-Through-Silicon-Vias (Nano-TSV) für die spätere Durchkontaktierung und der Stromzufuhr über die Rückseite, die so direkt an den Transistoren ankommt und nicht einmal die Metal-0-Lage erreichen muss. Die Metal-0-Lage kann dadurch am Ende sogar wieder etwas größer werden (von 30 auf 36 nm). Das wird sich in Zukunft als Kostenersparnis nicht nur für den ersten Prozess, sondern auch die darauffolgenden auswirken und soll so die Auftaktkosten für PowerVia mehr als ausgleichen, betont Intel.

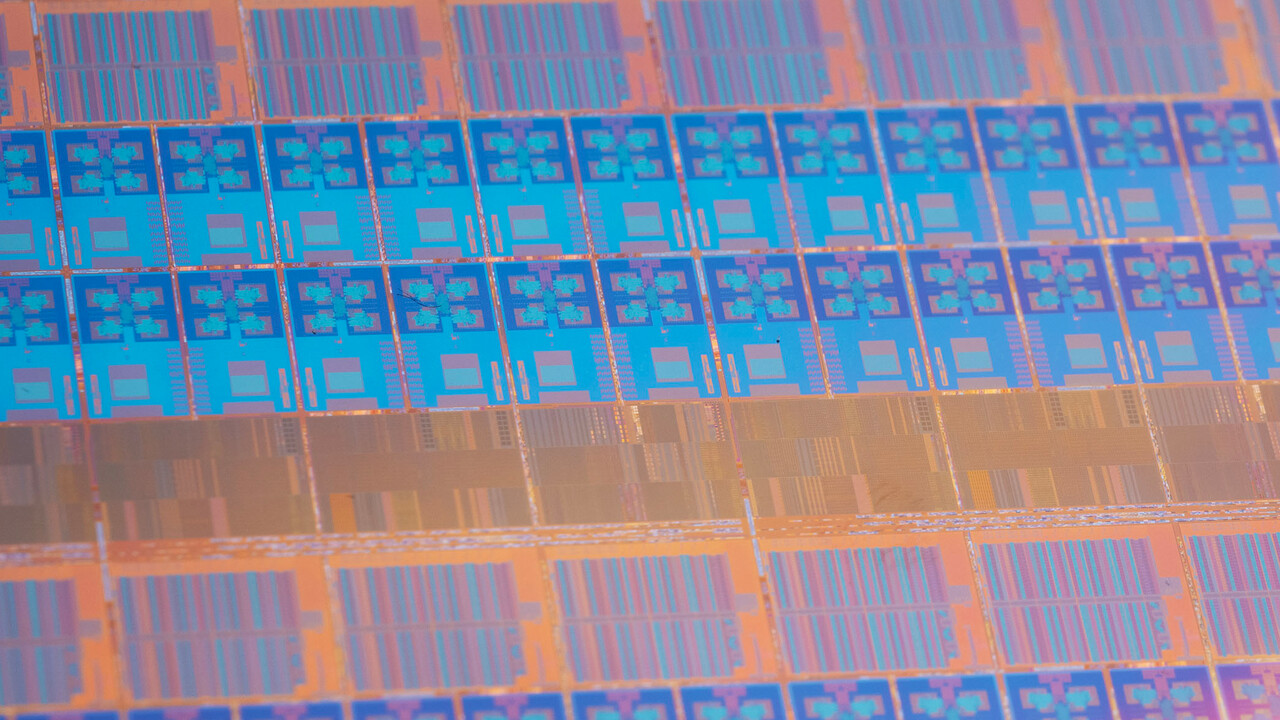

Ist die reguläre Oberseite dann im normalen Produktionsprozess fertig, wird obenauf ein Carrier-Wafer gesetzt und der (im Bild in Blau dargestellte) Wafer auf der Rückseite extrem weit herunter geschliffen, sodass quasi nur Transistoren auf einer sehr dünnen Schicht übrig bleiben. Er ist jetzt jedoch so dünn, dass der Carrier-Wafer die Aufgabe der Stabilisierung übernehmen muss. Dann wird der Wafer für den nächsten Schritt gedreht, im Anschluss erfolgt die Fertigstellung der Unterseite.

We call it silicon technology, but the amount of silicon that’s left on these wafers is really tiny.

Ben Sell, Intel

Die Yield, also die Ausbeute an funktionsfähigen Chips, sieht dabei bisher extrem gut aus, betont Intel auf Nachfrage. Die Yield-Kurve, also die Entwicklung der Ausbeute über die Zeit, liege nur rund ein halbes Jahr hinter Intel 4 zurück, das allerdings ein Jahr früher erscheinen werde. Auch bei den Temperaturen wurden quasi keine Unterschiede zur regulären Intel-4-Fertigung festgestellt. Beim Testchips wurde dabei in die Extreme gegangen – sowohl im Minimum als auch im Maximum.

Intel Arrow Lake wird die erste Produktfamilie, die PowerVia aus der Serienproduktion mit Intel 20A ab 2024 nutzen wird. Das aus den Fortschritten resultierende Produkt soll am Ende so effizient werden wie nie zuvor, erklärt Intel abschließend. Es bleibt abzuwarten, ob das im nächsten Jahr dann auch so kommt.

ComputerBase hat Informationen zu diesem Artikel von Intel unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.