CPU-Gerüchte: Angaben zu Zen 5 und Zen 6 angeblich von AMD

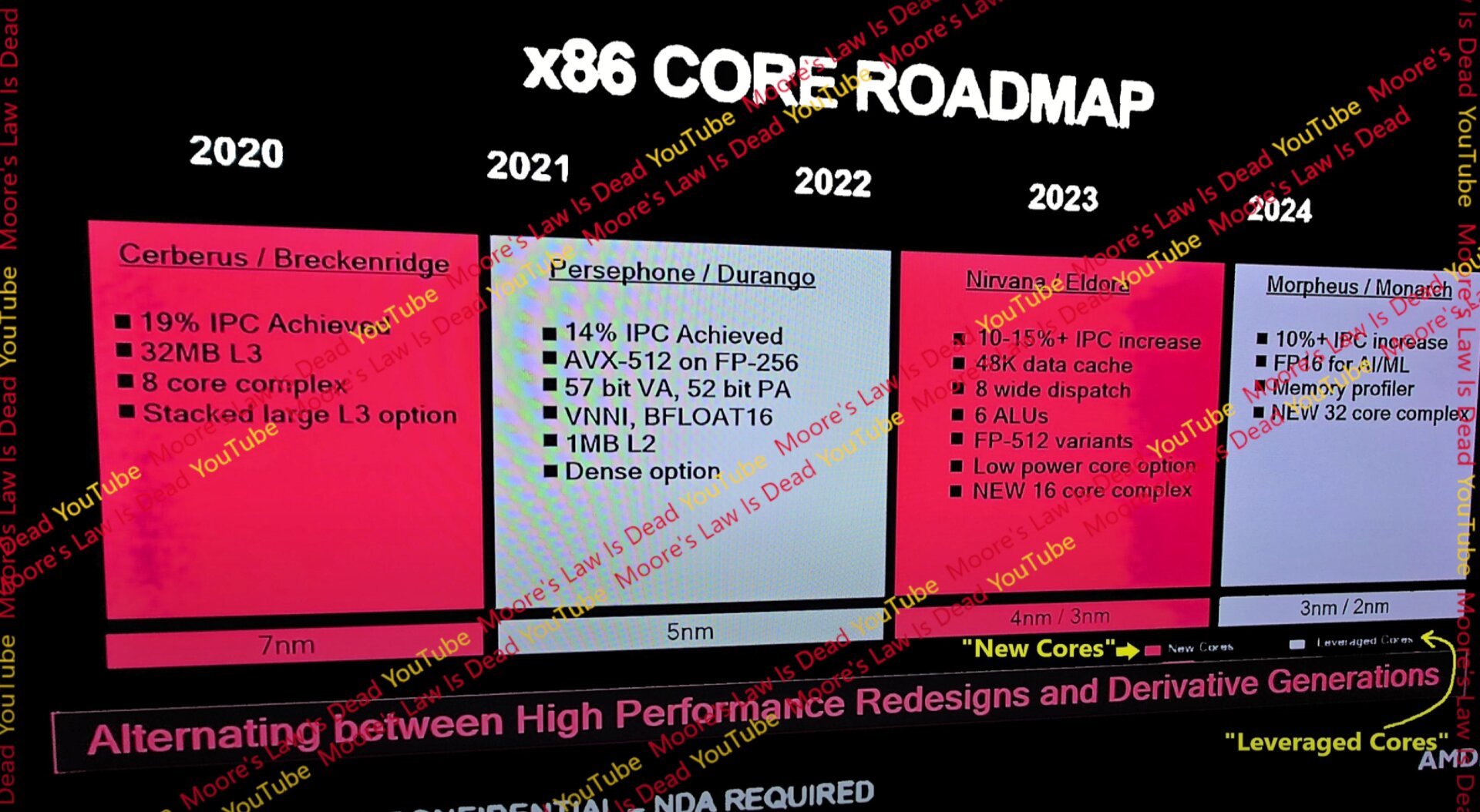

Aus einer internen AMD-Präsentation, genauer einem „design status update for EPYC“, soll eine Roadmap stammen, die Angaben zu den kommenden Architekturen Zen 5 und Zen 6 macht. Hinzu kommt ein Diagramm zur Nirvana-Architektur (Zen 5).

Weder die Echtheit noch das Alter der Präsentationsfolien lässt sich feststellen, die der YouTube-Kanal Moore's Law is Dead veröffentlicht und nach eigenen Angaben zum Schutz der Quelle optisch verändert hat. Die Informationen sind also mit Vorsicht zu genießen.

Spätestens seit dem Blick in das LinkedIn-Profil eines AMD-Mitarbeiters ist bekannt, dass die Mikroarchitektur von Zen 5 den Codenamen Nirvana trägt, während dessen Nachfolger Morpheus (Zen 6) lautet.

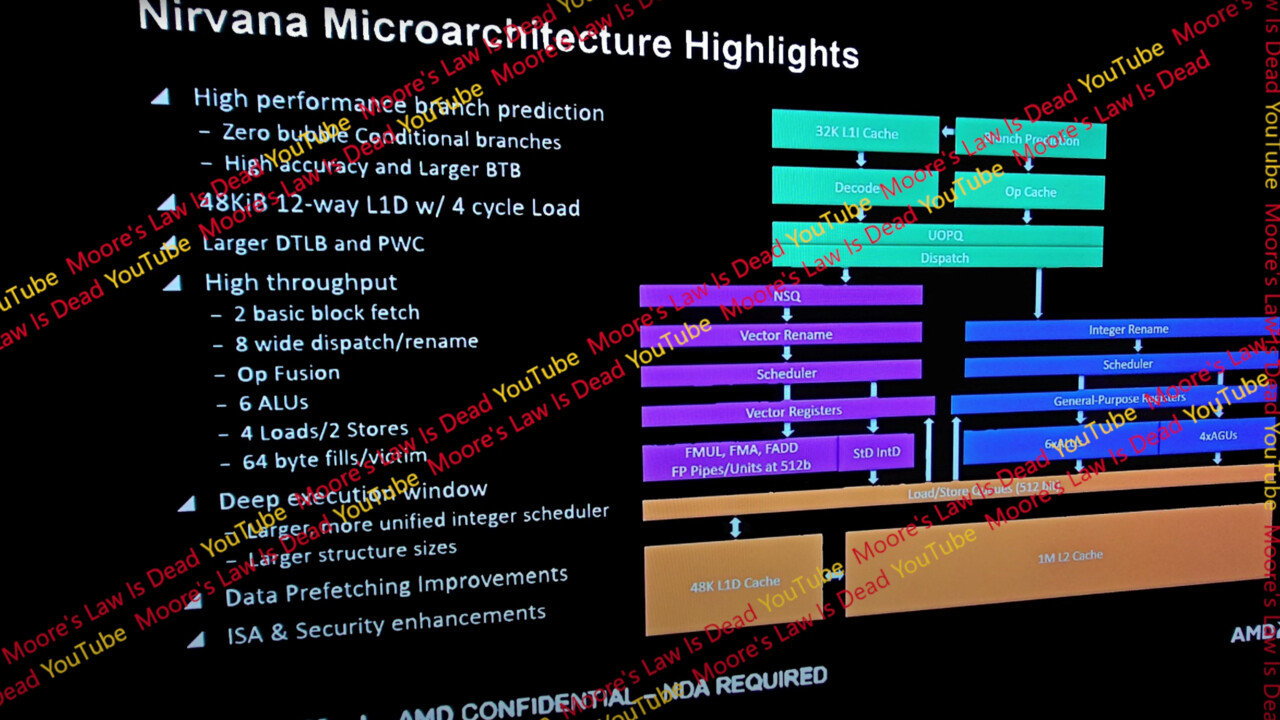

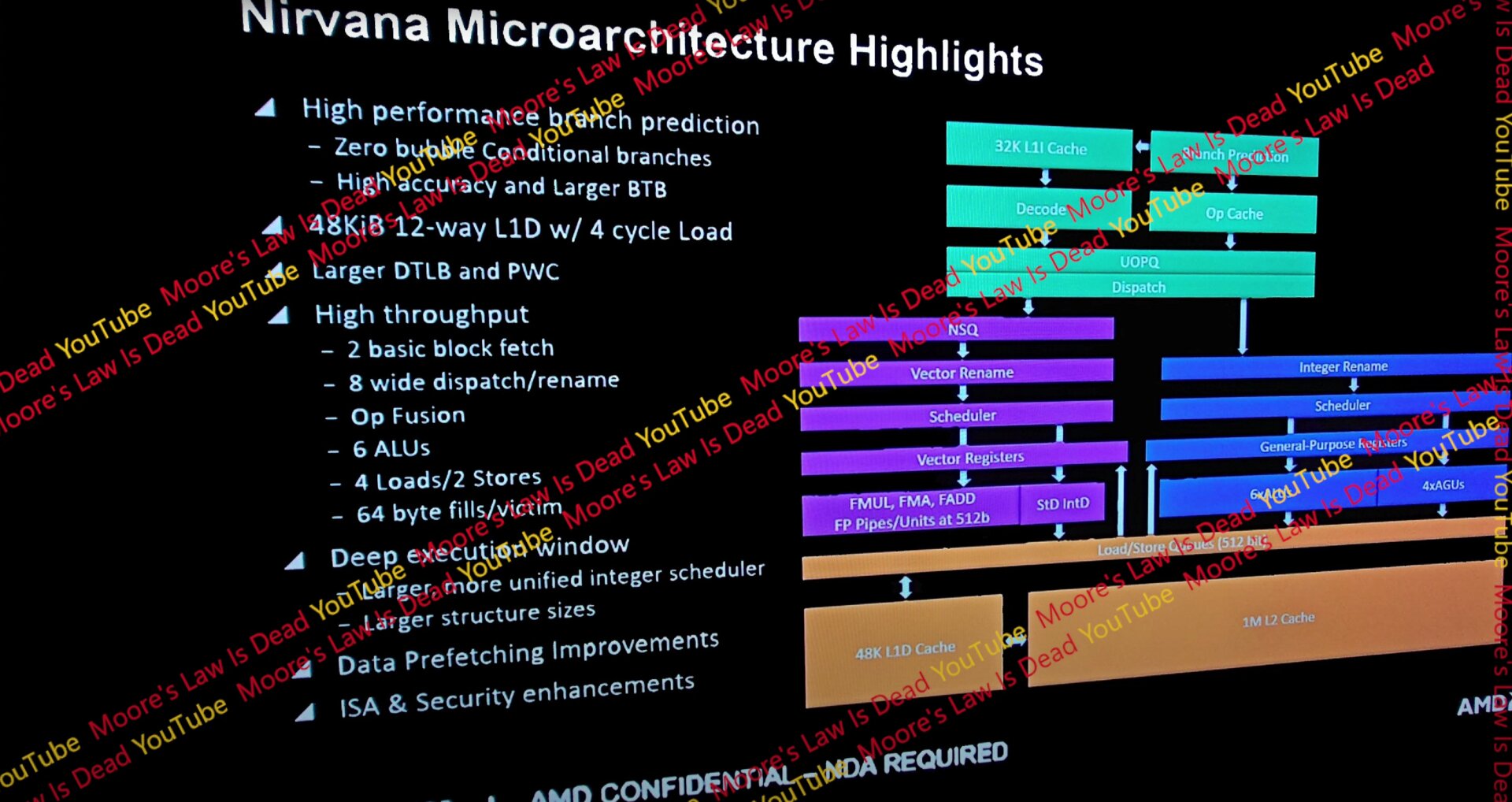

Angaben zur Zen-5-Architektur (Nirvana)

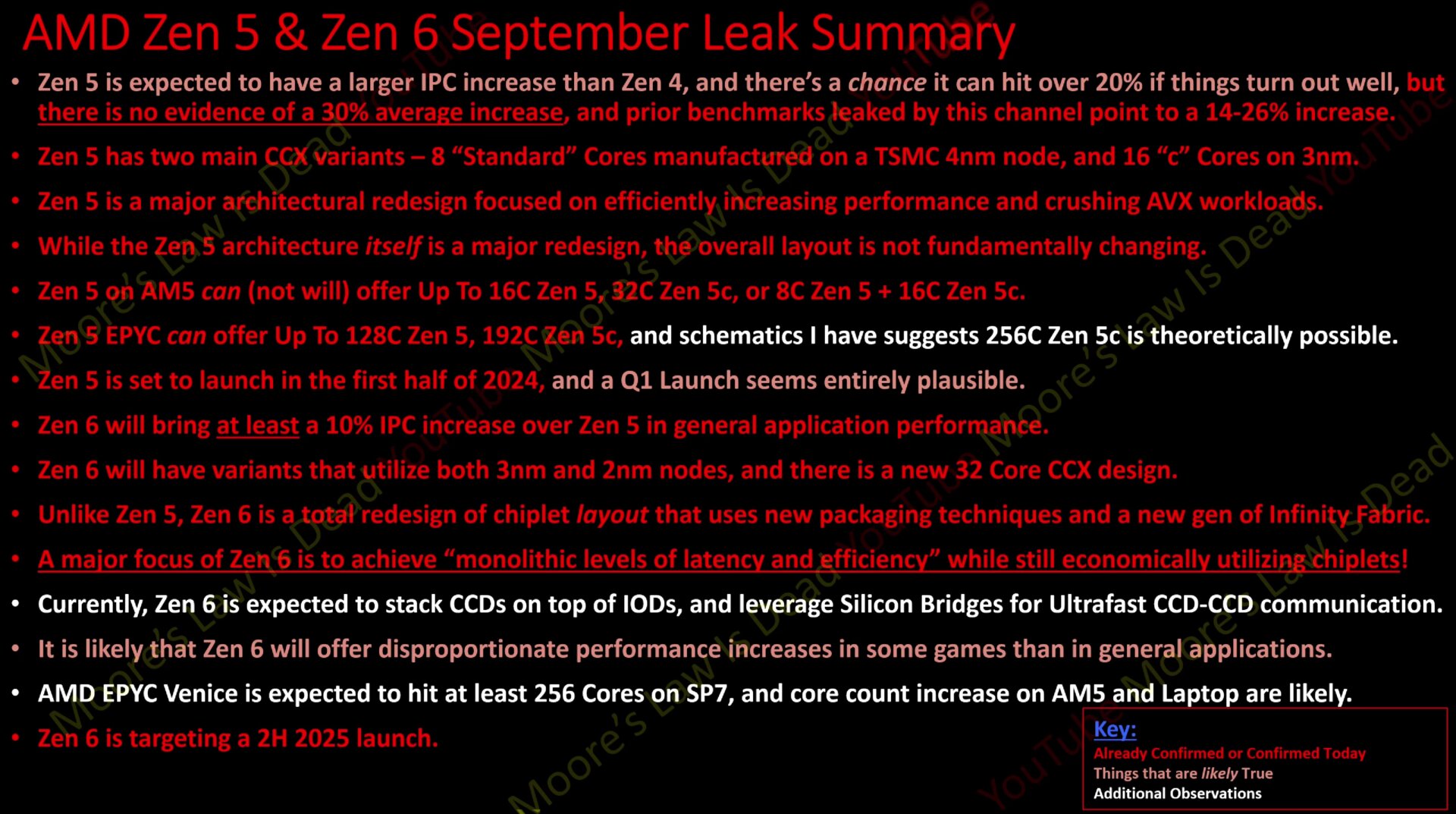

Laut der Roadmap wird für Nirvana eine Steigerung der Instruktionen pro Taktzyklus (IPC) in einem Bereich von 10 bis 15 Prozent anvisiert. Anhand eines früheren, allerdings ebenso unbestätigten Cinebench-Benchmarks geht der Kanal von einer größeren Steigerung aus. Zumindest soll die IPC in höherem Maße zunehmen als es beim Wechsel von Zen 3 zu Zen 4 mit 14 Prozent (laut Roadmap) der Fall war. IPC-Angaben sind aber generell schwierig, denn letztlich kommt es immer auf den Betrachtungswinkel respektive den Anwendungsfall an.

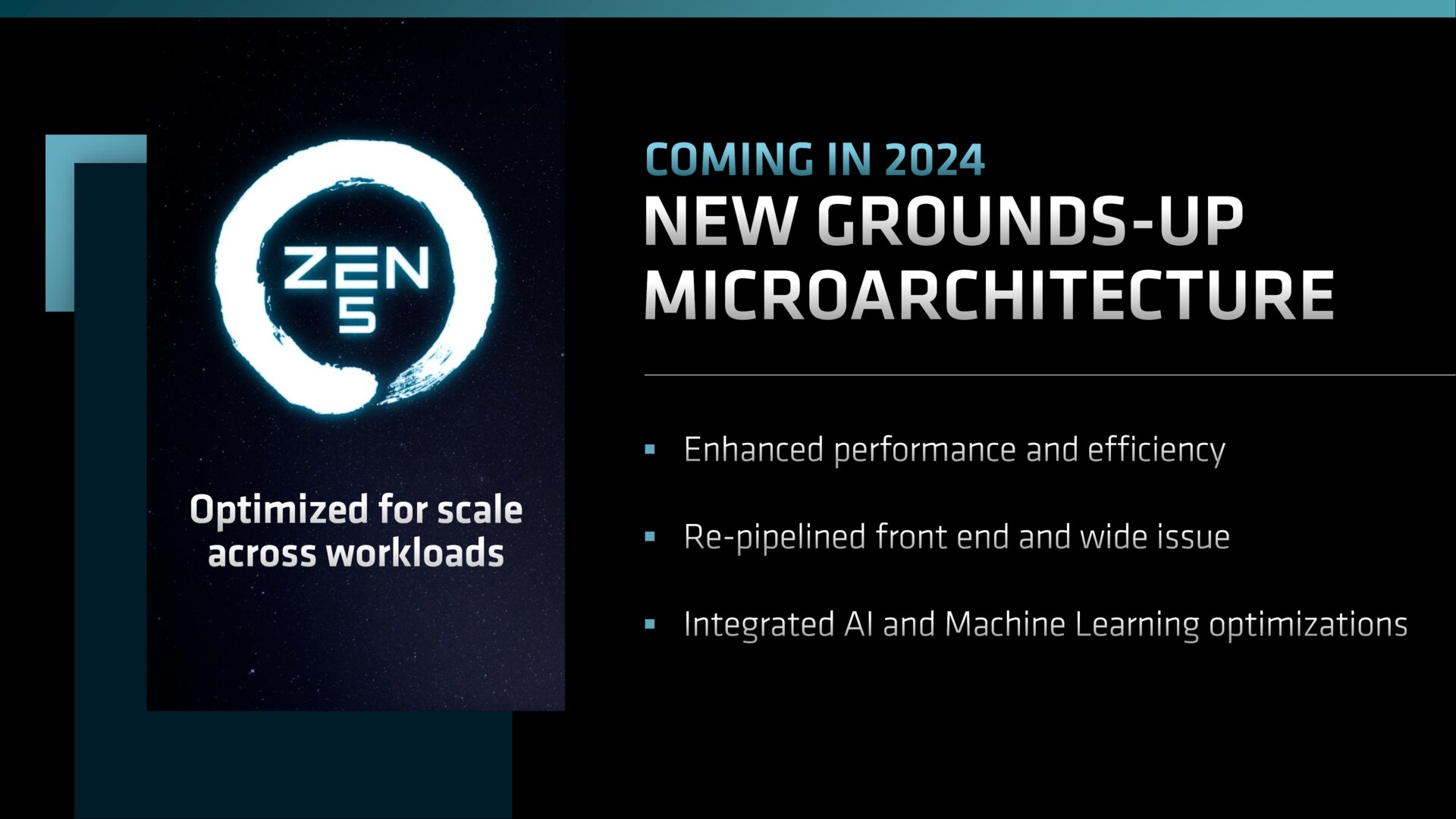

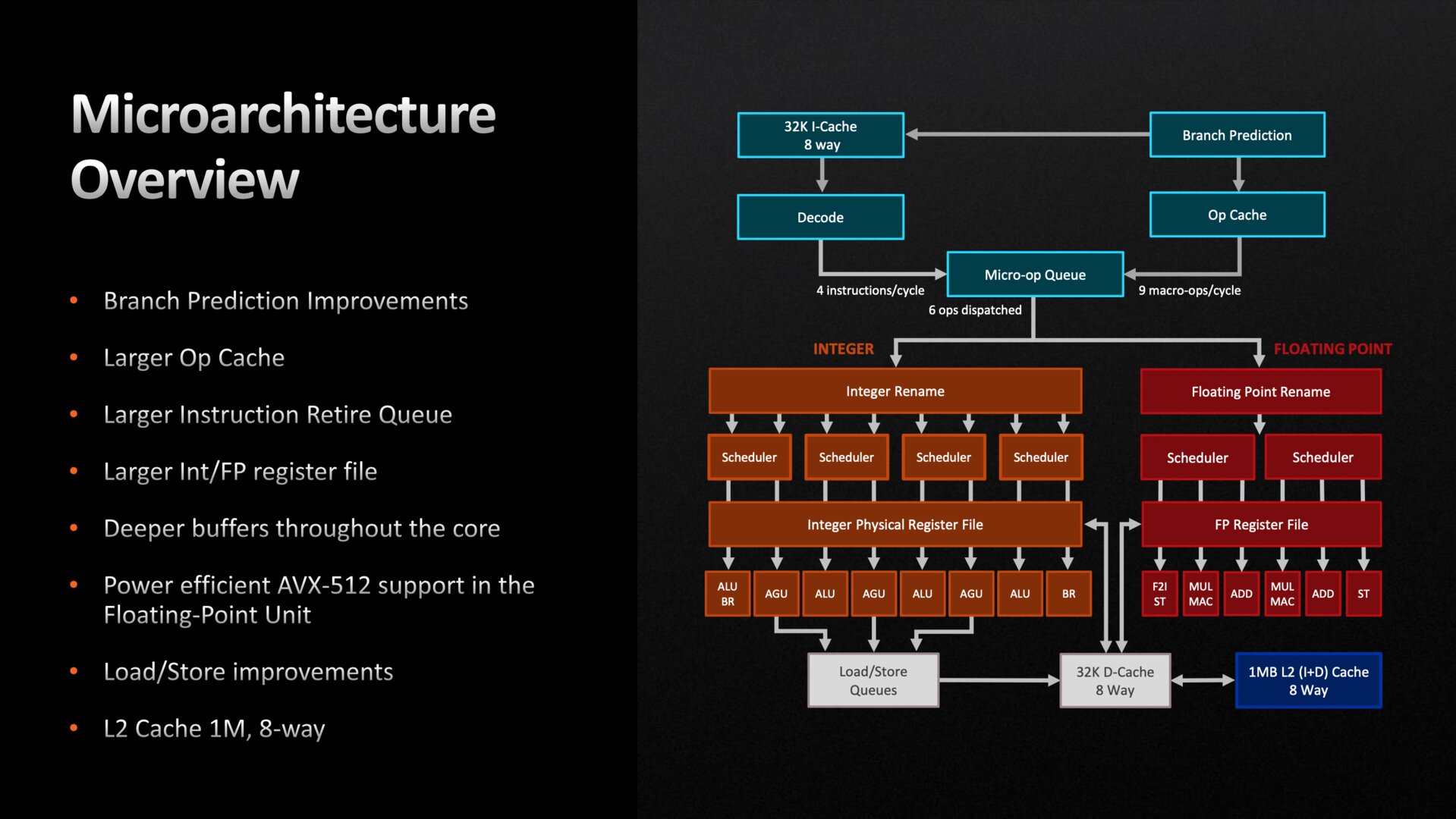

Während Zen 4 nur ein Update von Zen 3 mit vergleichsweise kleinen Änderungen gewesen ist, soll Zen 5 eine von Grund auf neue Mikroarchitektur sein, wie es AMD selbst formuliert hat.

Sofern die Angaben in der Roadmap stimmen, ändert sich so einiges. So soll der L1-Daten-Cache von 32 KB auf 48 KB vergrößert werden und die Zahl der ALUs soll von 4 auf 6 und somit ebenfalls um 50 Prozent steigen. Der L2-Cache bleibe aber unverändert bei 1 MB pro Kern.

| Zen 4 | Zen 5 | |

|---|---|---|

| Fertigung | 5 nm | 4 nm / 3 nm |

| Max Kerne pro CCX | 8 (16 bei Zen 4c) | 16 (bei Zen 5c?) |

| L1D-Cache | 32 KB | 48 KB |

| ALUs | 4 | 6 |

| L2-Cache | 1 MB | |

Ferner ist von FP-512-Varianten und einer „Low Power Core option“ die Rede. Pro Core Complex (CCX) soll Zen 5 nun bis zu 16 aktive Kerne aufweisen, womit sich die Zahl gegenüber Zen 4 verdoppelt. Dass hier die kleineren „c“-Kerne gemeint sind, wie sie bei Zen 4c (Bergamo, Siena) vorliegen, ist in diesem Kontext unwahrscheinlich, denn diese Option gibt es eben bereits beim Vorgänger und wäre somit nicht „neu“.

Allerdings kann die Roadmap in diesem Punkt auch nicht aktuell sein, daher Zen 4c unterschlagen und der 16-Kern-CCX eben doch Zen 5c bedeuten. Bei den kommenden APUs der Serie Strix Point wird AMD voraussichtlich vollwertige Zen-5-Kerne mit kleineren Zen-5c-Kernen kombinieren.

Moore's Law is Dead (MLID) geht auch davon aus, dass es wie beim Vorgänger einen CCX mit 8 großen Kernen und einen CCX mit 16 kleinen „c“-Kernen geben wird.

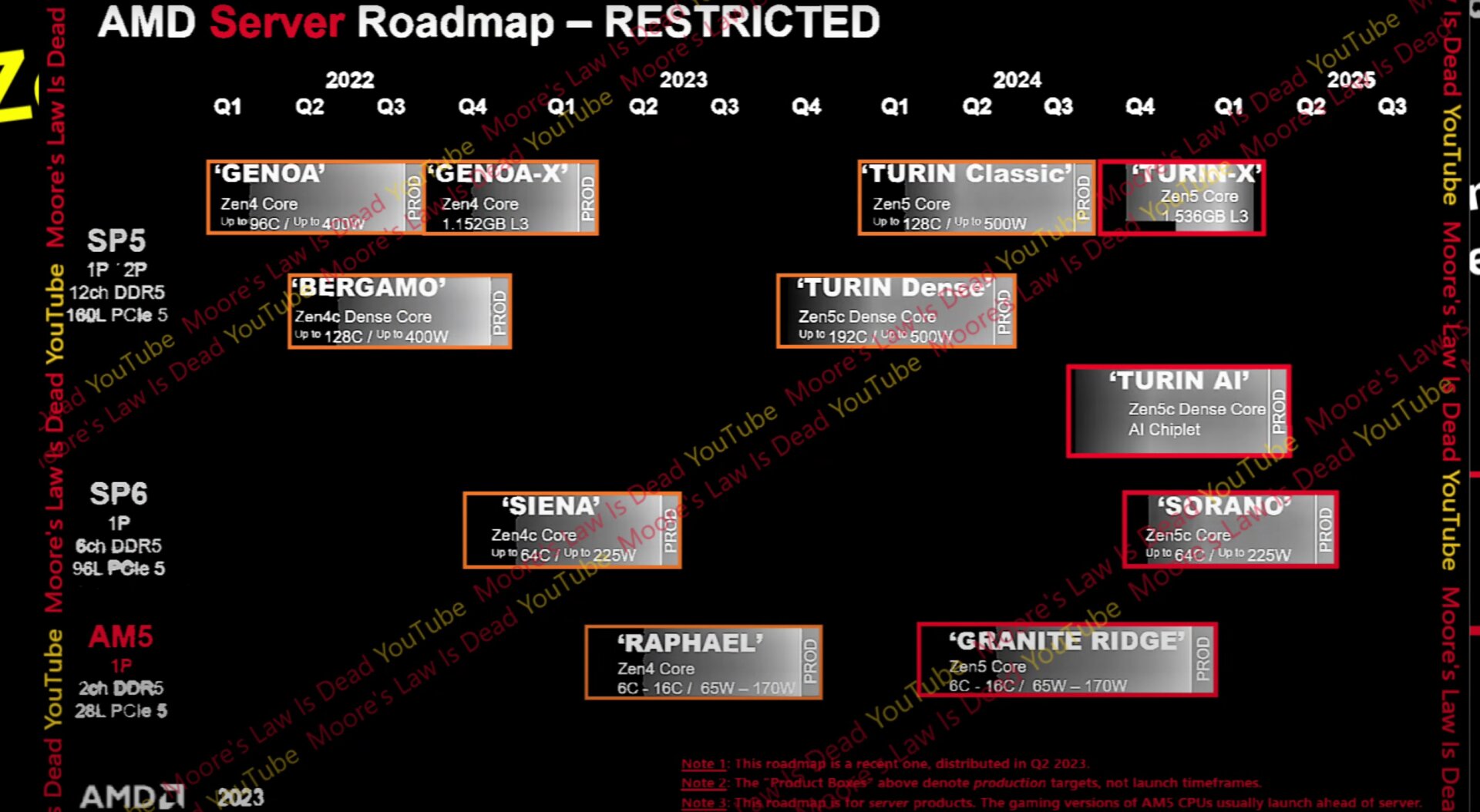

Zuvor hatte der Kanal eine weitere Roadmap mit ebenso unbestätigten Daten zu kommenden Server-Prozessoren von AMD veröffentlicht. Dort ist von bis zu 128 Zen-5-Kernen bei Turin, dem Nachfolger von Genoa und 192 Zen-5c-Kernen bei „Turin Dense“, dem Nachfolger von Bergamo, die Rede.

Angaben zu Zen 6 (Morpheus)

Wieder nur einen kleinen Sprung soll es von Zen 5 zu Zen 6 (Codename Morpheus) geben. Die noch sehr frühe und somit grobe Prognose lautet, dass die IPC nochmals um mindestens 10 Prozent zulegen werde. Zudem wird erstmals ein 32-Kern-CCX genannt. Ferner ist von einem Memory Profiler und FP16-Befehlen für AI und Machine Learning die Rede.

Für Zen 6 erwartet MLID ein neues Layout mit neuen Packaging-Techniken und einer neuen Generation des Infinity Fabric. Noch nicht so sicher ist sich der Kanal dabei, dass dann die CPU-Chiplets (CCD) direkt auf den I/O-Die (IOD) gestapelt werden.

Zeitlich wird Zen 5 für das erste Halbjahr 2024 und Zen 6 für das zweite Halbjahr 2025 erwartet.