Erstes funktionales 20-nm-Silizium mit TSV von Globalfoundries

Statt durch immer feinere Herstellungsverfahren die Bauteile von Mikroprozessoren zu verkleinern, um mehr davon auf gleicher Fläche unterbringen zu können und dadurch die Leistung zu steigern, sucht die Halbleiterindustrie parallel bei sogenannten „3D-Chips“ ihr Heil in der Vertikalen. Dabei kommt die TSV-Technik zum Einsatz.

Globalfoundries vermeldet nun Fortschritte auf dem Weg zu „gestapelten“ Chips mittels Through-Silicon Via (TSV), also einer Technik zur Durchkontaktierung von Silizium, die auch vertikale elektrische Verbindungen in Mikrochips und somit auch dreidimensionale Chips ermöglicht. Hier wird oftmals vom 3D Stacking (Stapeln, Aufschichten) gesprochen.

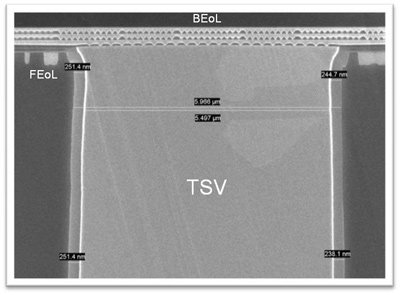

In der Fertigungsanlage „Fab 8“ hat der Auftragsfertiger seine ersten funktionsfähigen Silizium-Wafer mit 20-nm-Strukturbreite und integrierten TSVs vorgeführt. Dabei fand der 20-nm-LPM-Herstellungsprozess Verwendung. Nach der von Globalfoundries beschriebenen Methode wurden die TSVs nach der Herstellung der Transistoren (dem sogenannten Front-End-of-Line (FEOL)) und vor deren Verdrahtung (Back-End-of-Line (BEOL)) in das Silizium eingesetzt. Somit würden die beim FEOL-Abschnitt herrschenden hohen Temperaturen umgangen, sodass Kupfer als Füllmaterial für die TSVs genutzt werden könne, so der Hersteller. Zuvor hatte man bereits mit TSVs im 28-nm-Prozess experimentiert.

„Seit Jahren hat unsere Branche über die Aussichten des 3D Chip Stacking gesprochen, aber diese Entwicklung ist ein erneutes Zeichen, dass die Hoffnungen bald Realität werden“, erklärt David McCann President of Packaging R&D bei Globalfoundries. Nun heiße es, die TSV-Einsatzmöglichkeiten der Fab 8 wirksam in Verbindung mit Partnern einzusetzen und Prototypen herzustellen sowie zu testen. Bis die Technik in Endprodukten Verwendung finden wird, dürfte somit noch einige Zeit vergehen. Bereits vor knapp einem Jahr hatte Globalfoundries in der Fab 8 mit der Installation der für TSV benötigten Werkzeuge begonnen.

Obgleich dies klingen mag, als wäre Globalfoundries der erste Halbleiterfertiger, der erfolgreich 3D-Chips mittels TSV hergestellt habe, ist dies längst nicht der Fall. Speziell in der Speicherbranche sind „Stapelchips“ schon lange ein Thema. So hatte Samsung bereits 2007 ein Verfahren zum Aufschichten von DRAM-Chips mit Hilfe von Through Silicon Vias vorgestellt. 2010 folgten erste RDIMMs auf Basis dieser Technik. Ein jüngeres Beispiel für mittels TSV ermöglichte 3D-Chips ist Microns „Hybrid Memory Cube“, dessen finale Spezifikationen erst vor Kurzem verkündet wurden.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!