Intel zeigt Prozessor mit 48 Kernen in Aktion

Am 1. Dezember hat Intel in Braunschweig für ausgewählte Pressevertreter seine neueste Entwicklung gezeigt. Und diese kann sich sehen lassen: 48 Kerne auf einer Fläche von lediglich 567 mm². ComputerBase hat sich das lauffähige Modell vor Ort angesehen und gibt einen detaillierten Überblick.

Der Prozessor mit 48 Kernen, Codename „Rock Creek“, ist ein Prototyp, der zum großen Teil in Braunschweig entwickelt wurde. Bereits kurz nach dem Polaris-Projekt wurde von Intel 2007 angekündigt, dass man mit der aktuell auf dem Markt im Einsatz befindlichen x86-Architektur weiter arbeiten will, um ein Produkt für die Forschung mit großem Realitätsbezug bereit zu stellen. Der gezeigte 48-Kern-Prozessor ist das Ergebnis der Forschung der letzten Jahre auf dem Gebiet. Wie Polaris soll er in sehr geringer Stückzahl im kommenden Jahr an Entwickler ausgeliefert werden. Zusammen mit Intel sollen diese an Softwarelösungen und Optimierungen für Programme bei Nutzung von mehr als der heute üblichen Zahl von CPU-Kernen arbeiten.

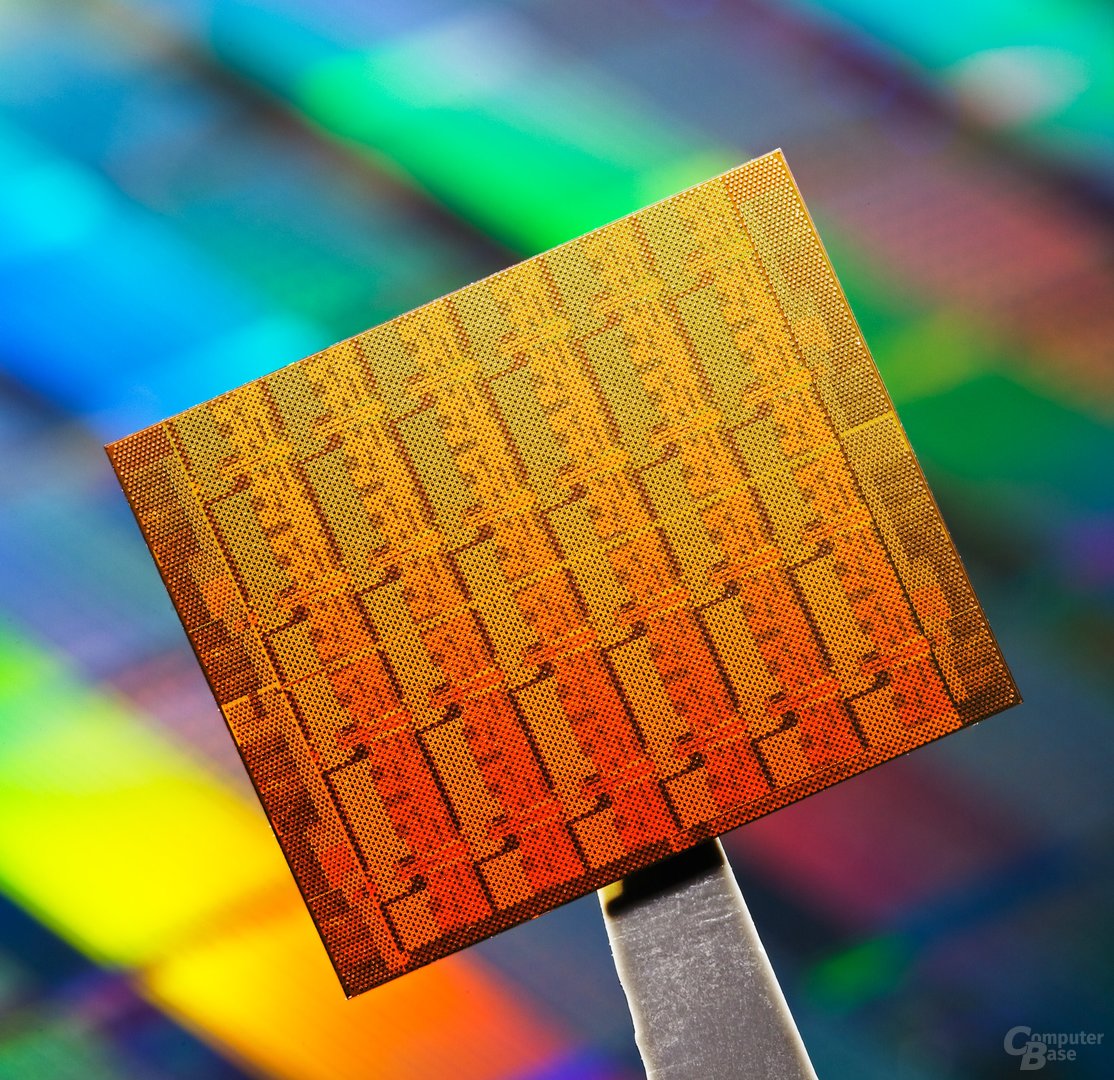

Der experimentelle Prozessor mit 48 voll programmierbaren Kernen stellt Intels aktuelle Speerspitze in der öffentlich bekannt gegebenen Entwicklung dar. Diese Kerne basieren auf der Pentium-Technologie und können entsprechend skaliert werden, so wie dies auch für Larrabee im Grafikmarkt gedacht ist. Während im kommenden Jahr Prozessoren mit acht Kernen in den Markt entlassen werden, zielt der neue Prozessor, der von Intel „single chip cloud computer“ genannt wird, auf den Markt der Zukunft. Da in Zukunft aber – ebenso wie heute – nicht nur Leistung gefragt ist, sondern auch immer ein Blick auf den Energiebedarf solch eines Derivats geschaut wird, ist Intel besonders stolz, diesen mit 25 bis 125 Watt zu beziffern. Dabei beziehen sich die 25 Watt auf den Idle-Modus, was auf einen Energiebedarf von ungefähr 0,5 Watt pro Kern hinausläuft. Unter Volllast sind es fünf Watt pro Kern, was in den gezeigten Demos bei Aktivität aller 48 Kerne jedoch nie erreicht wurde. Ein ausgeklügeltes System soll dafür sorgen, dass in dem Prozessor bis zu acht verschiedene Spannungen in unterschiedlichen Bereichen anliegen können.

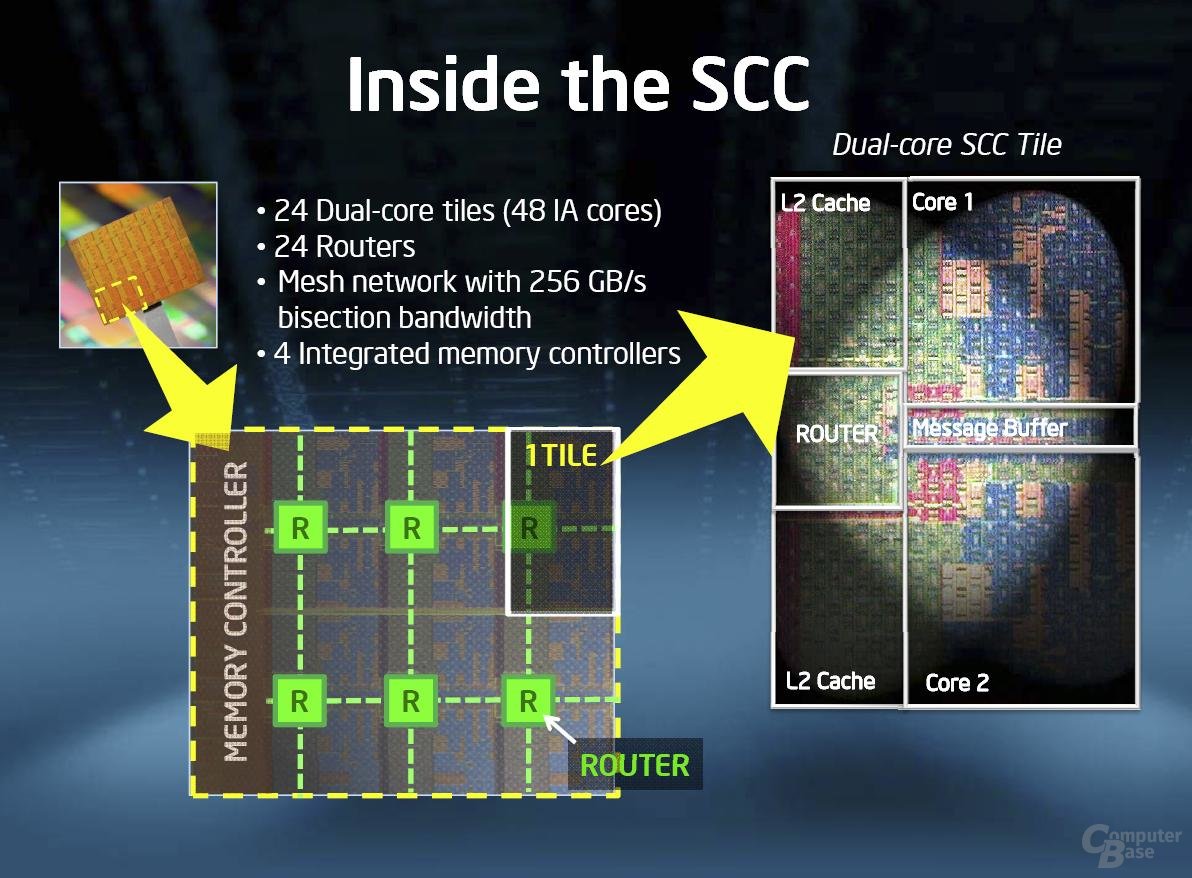

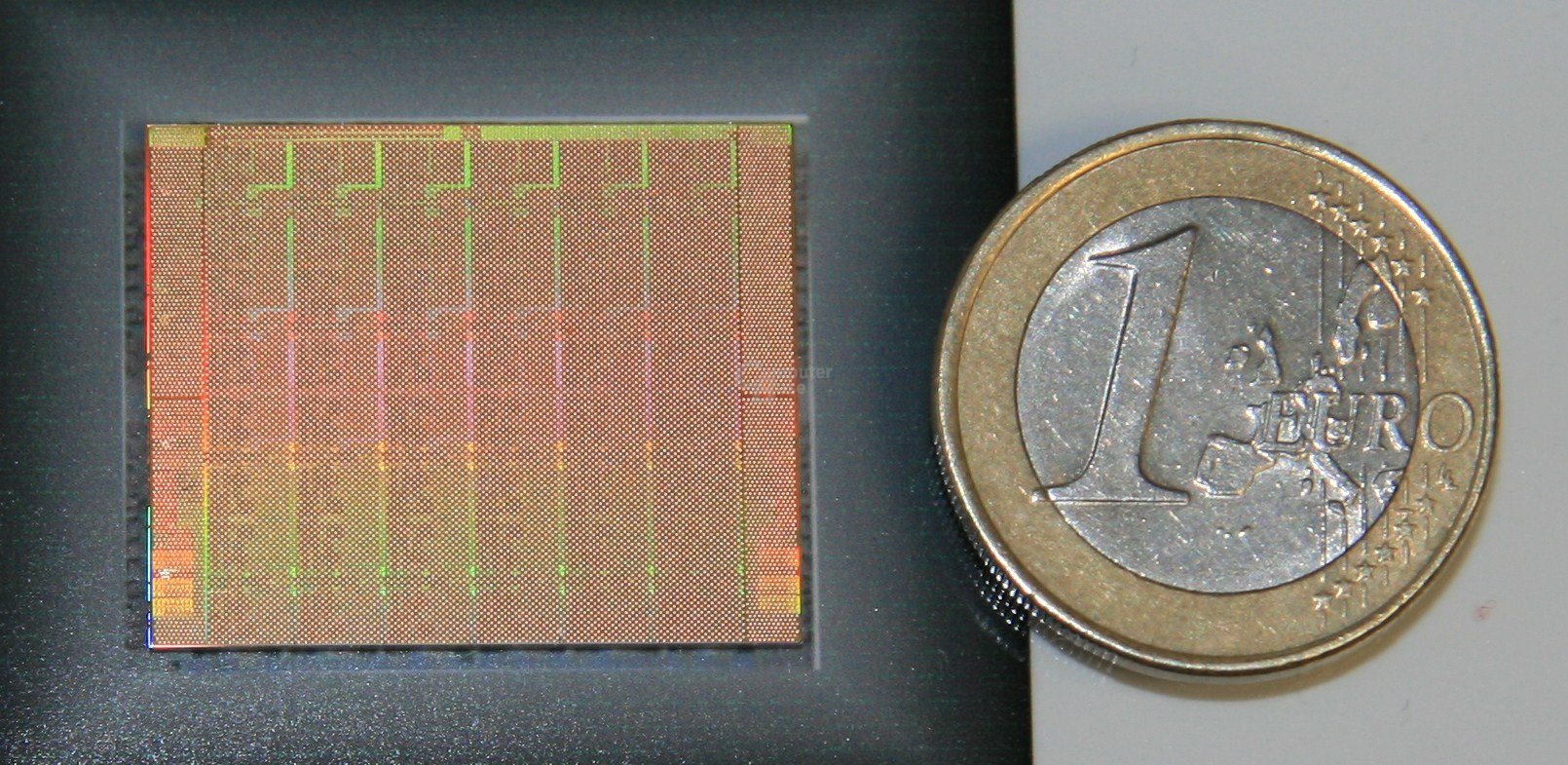

Der Prozessor setzt auf die 45-nm-Technologie und belegt dabei eine Fläche von 567 mm². Zum Vergleich: Eine 1-Euro-Münze hat eine Oberfläche von 425 mm². Der Prozessor operiert in einer 32-Bit-Umgebung, als Hauptspeicher kommt DDR3 zum Einsatz, der maximal 32 GByte groß sein kann. Die 48 Kerne sind auf dem „Die“ in 24 „Tiles“ aufgeteilt, von denen jeweils sechs ein Segment bilden. Vier dieser Segmente setzten sich mit jeweils einem Speichercontroller dann zum kompletten Prozessor zusammen. Was rechnerisch jetzt aber erst nach der halben Anzahl an Kernen aussieht, erklärt sich leicht: Intel bringt pro Tile zwei Kerne unter, die jeweils von L2-Cache unterstützt werden, was schlussendlich zu der Gesamtzahl von 48 Kernen mit vier Speichercontrollern führt. Es sind, im einfachsten Sinne ausgedrückt, 48 kleine PCs mit der experimentellen CPU in einem einzigen Stück Hardware verwirklicht.

Eine weitere Besonderheit ist jedoch in jedem dieser Tiles zu finden. Jeder der zwei Kerne in einer dieser Einheiten besitzt neben dem L2-Cache auch einen „Message Buffer“. Über ein Mesh-Netzwerk mit einer Bandbreite von 256 GB/s kommunizieren die Tiles untereinander, wobei der zusätzliche, 384 KByte große Message Buffer pro komplettem Prozessor eine wichtige Rolle spielt. Geht es nach dem vorliegen Schema, so verfügt der Prozessor im Ganzen über 24 dieser Message Buffer, so dass diese pro Tile jeweils 16 KByte groß sind. Jedes separate „Tile“ kann auf ihren eigenen Speicher zurückgreifen, aber auch auf den anderer Kerne. Das heißt im Gesamtpaket, dass jeder der einzelnen Kerne auf den Teil des 384 KByte großen Speichers eines anderen Kerns zugreifen kann, wobei das „Mesh“ für die schnelle Kommunikation sorgen soll. Damit unterschiedet sich der experimentelle Prozessor deutlich von aktuellen Intel-Prozessoren, zum Beispiel auf Basis der Nehalem-Architektur, bei denen die Kerne untereinander nur über den L3-Cache kommunizieren, niemals aber direkt untereinander.

Jeder der Kerne in dieses Prozessors funktioniert damit quasi als eigenständige CPU, die beispielsweise ihr eigenes Linux booten oder einen Webserver betreiben kann. Die unabhängigen CPUs werden dann aber wieder gemeinsam genutzt – es entsteht ein Supercomputer auf lediglich einem Die (siehe Beispiel weiter unten). Dabei spielt insbesondere der Punkt der Speicher- bzw. Cache-Kohärenz eine wichtige Rolle. Dieser Punkt ist bei aktuellen Prozessoren über komplexe Hardware gelöst, die dafür sorgt, dass alle Kerne die gleichen Daten sehen und verarbeiten können und es zu keinen Fehlern kommt. MESI ist dabei die aktuell am häufigsten genutzt Form. Der vorgestellte Testchip von Intel verzichtet auf diese komplexen Schaltungen und ermöglicht so Forschungen an alternativen Many-Core-Chips, die diese Kohärenz über Software realisieren sollen oder dank der Benutzung des Message Passing Interface (MPI), welches bei den meisten Cluster- und Supercomputern zum Einsatz kommt, vollständig darauf verzichten können.

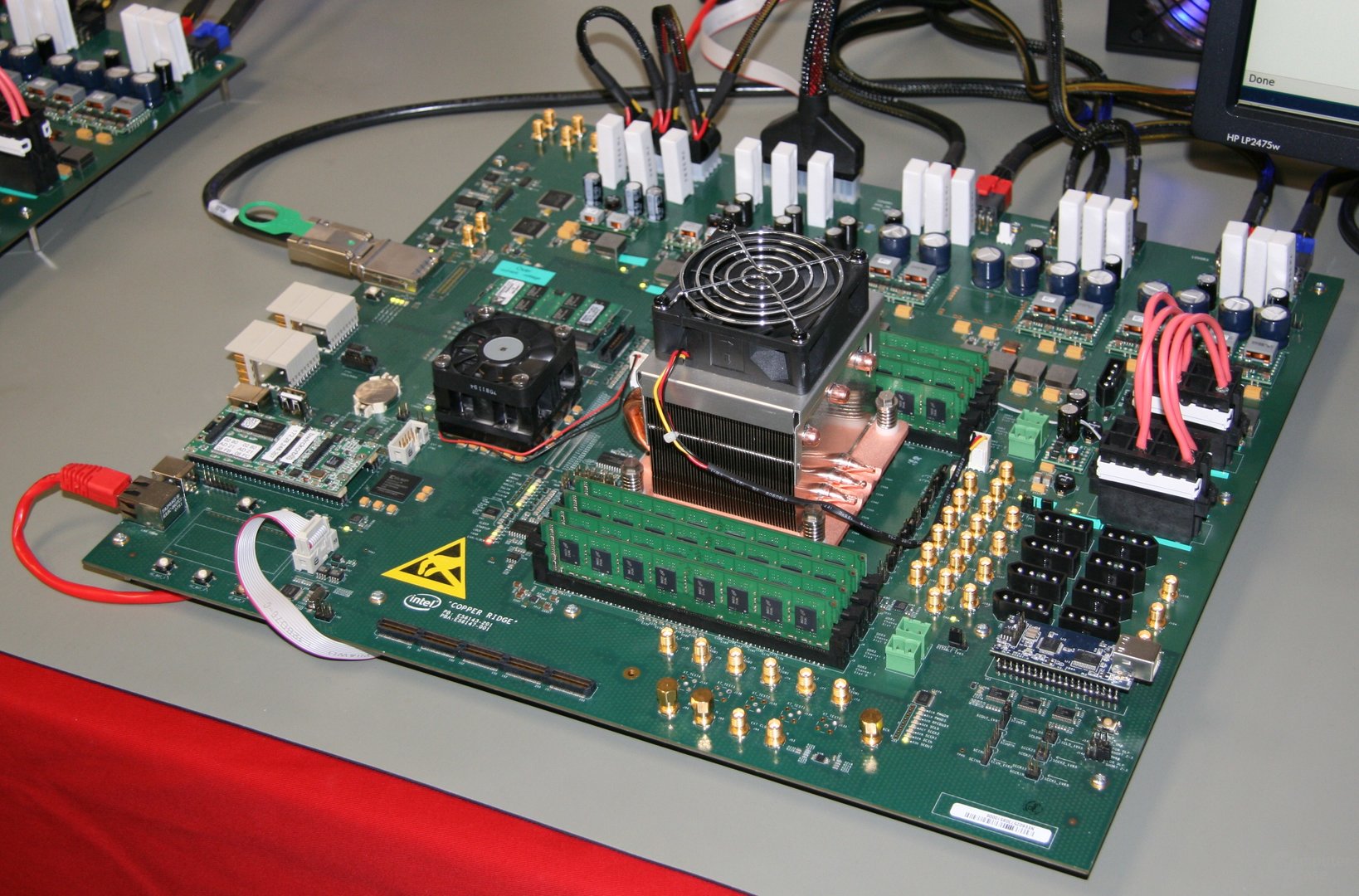

Die genauen technischen Daten will Intel zur kommenden Integrated Solid State Circuits Conference (ISSCC) im Februar 2010 bekannt geben. Seite 21 der Agenda kündigt bereits den Vortag zum 48-Kern-Prozessor an. Um der ganzen Theorie jedoch auch Taten folgen zu lassen, hatte Intel einige Demos vorbereitet. Während man die eigentliche CPU unter einem großen Kühler versteckte, waren die Ausmaße des Testmainboards schier riesig. Intel betonte aber sofort, dass es sich nur um eine Test-Station handelt, was angesichts der vielen zusätzlichen Steckverbindungen anhand der Bilder ersichtlich wird. Partner sollen eine deutlich kleinere Variante bekommen.

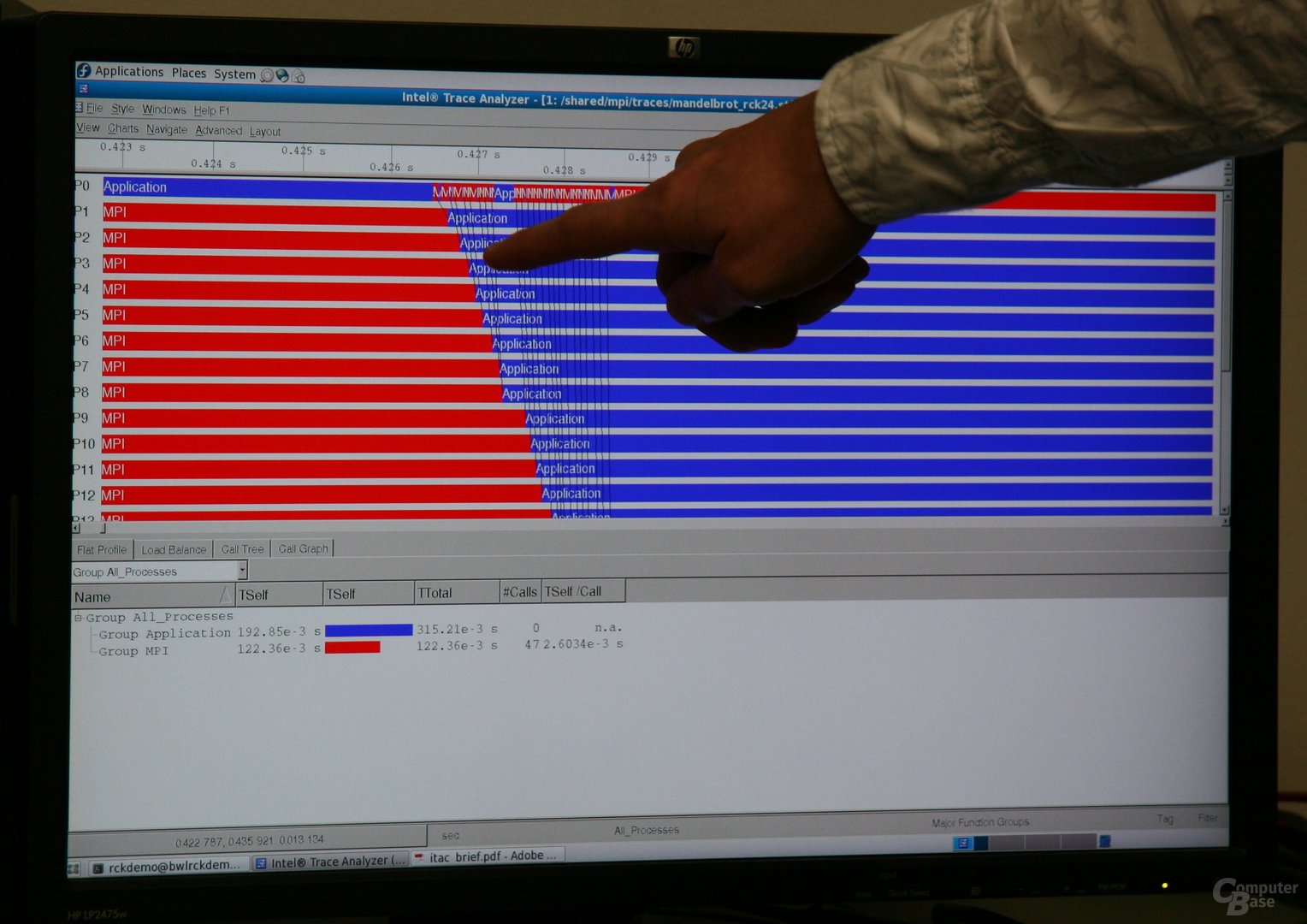

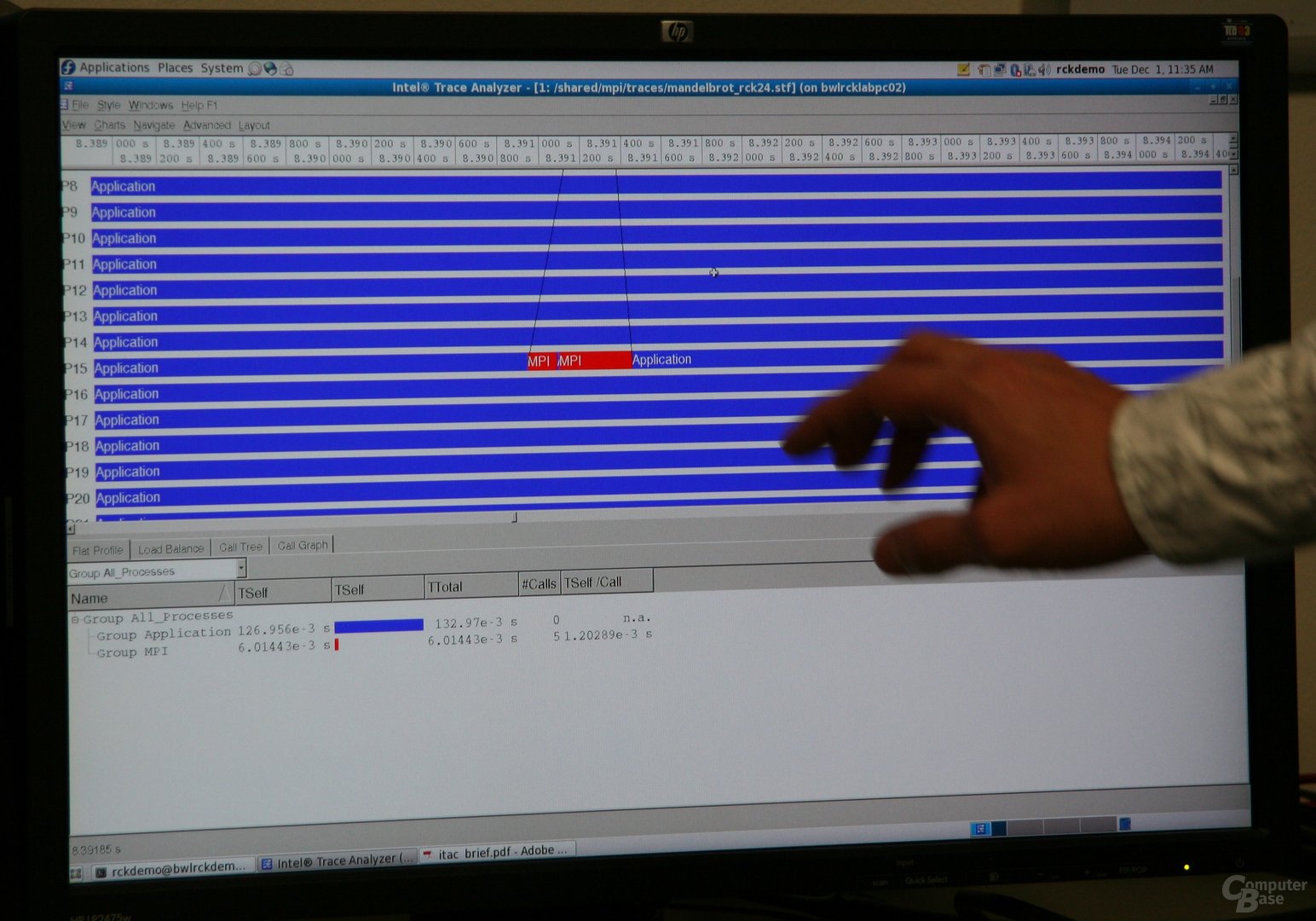

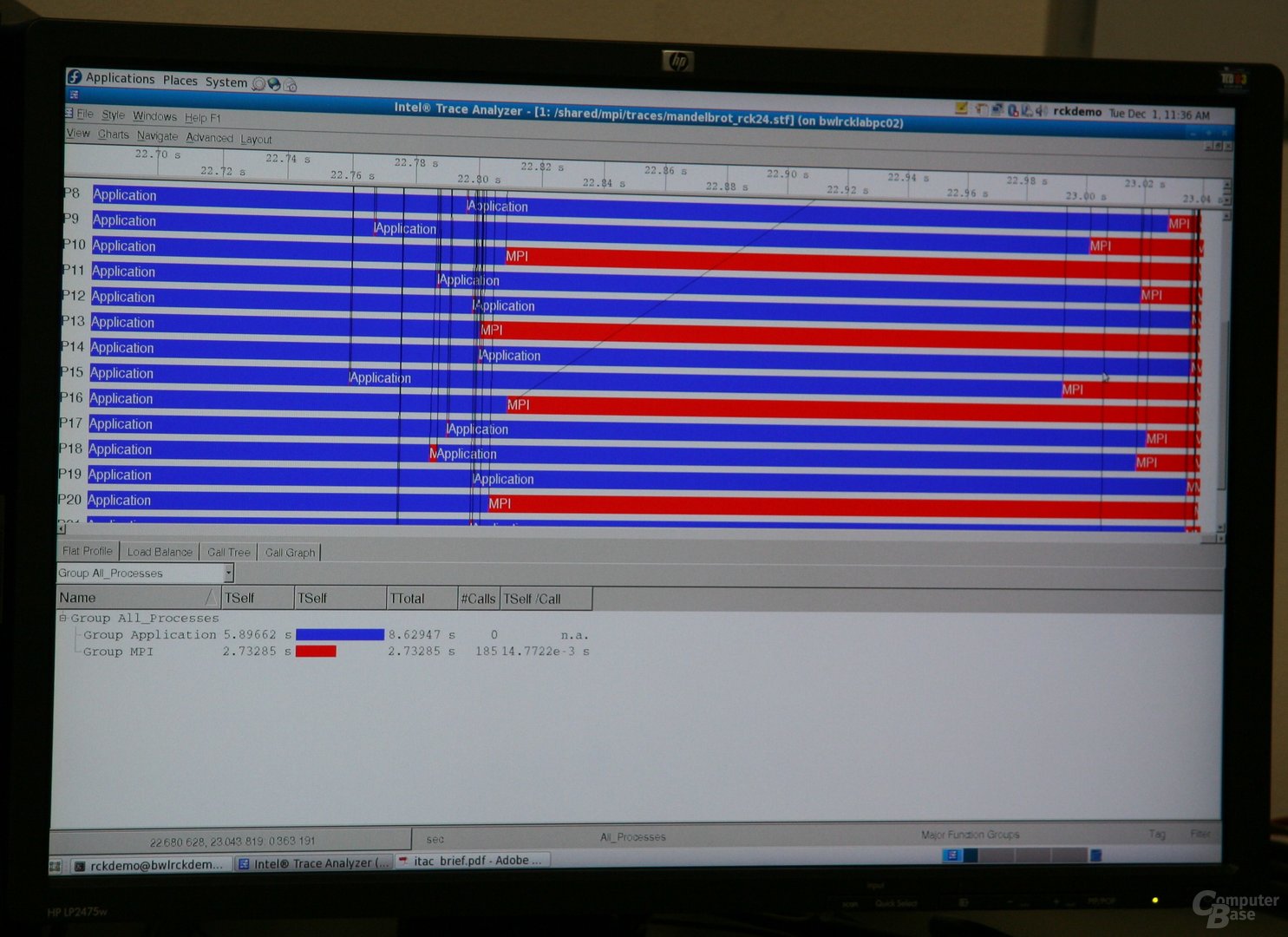

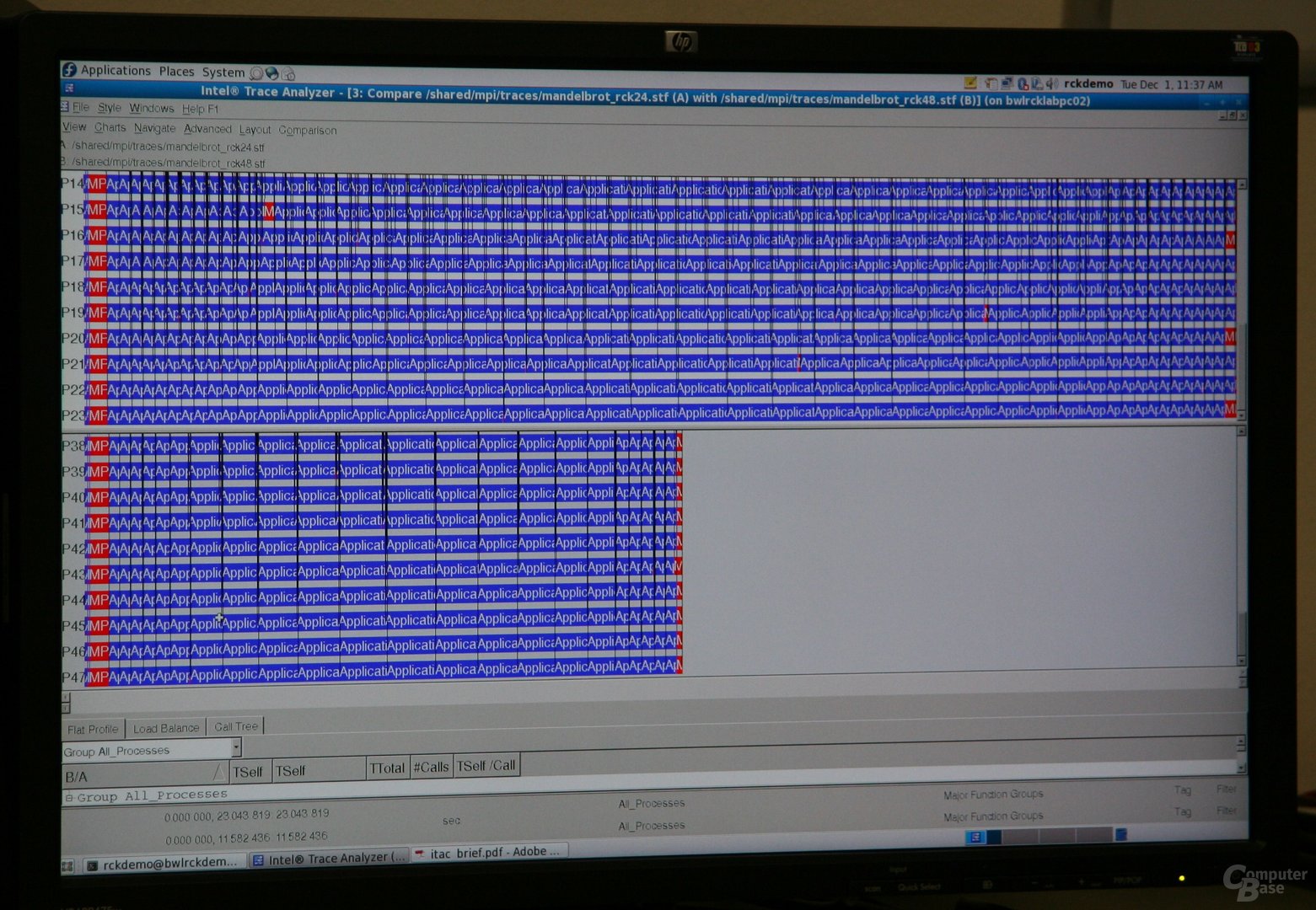

Ein beliebter Test für Multi-Kern-Simulationen ist das „Mandelbrot“. In der Vorführung wurde dies einmal mit 24 und einmal mit 48 Kernen erzeugt, wobei die nahezu perfekte Skalierung auffiel. Dafür sorgen der Aufbau und die interne Abwicklung. Der erste Prozessorkern kümmert sich um die Verteilung der Aufgaben an die weiteren Kerne. Die rote Farbe im Balken bedeutet, dass der einzelne Kern gerade nichts zu tun hat und auf Arbeit wartet. Der erste Prozessor gibt dem Kern innerhalb kürzester Zeit eine weitere Aufgabe, weshalb sich der rote in den blauen Status – Arbeit – wandelt. Dies geschieht so oft, bis die Arbeit erledigt ist.

Zum Abschluss des Tages gab es noch eine Führung durch die Labore in Intels Gebäude in Braunschweig. Dabei waren eigene Kameras natürlich nicht erlaubt. Geheime Sachen bekam man aber nicht zu Gesicht, denn die meisten Arbeitsplätze waren so aufgeräumt, wie es wohl selten der Fall sein dürfte. Einige interessante Dinge gab es aber doch zu sehen, obwohl die meisten Test-Stationen abgebaut waren und nur zufällig ein H55-Mainboard mit Clarkdale-Prozessor herum lag – aber dieses Gespann ist in vier Wochen auch im Handel verfügbar. Interessant war der Versuchsaufbau mit einem Asus-Mainboard mit 4 x 16 MByte EDO-RAM aus den alten Pentium-Zeiten. Dort lief über einen großen Adapter tatsächlich ein 45-nm-Atom-Prozessor mit 50 MHz. Man nutzt solche Aufbauten, um verschiedene Tests mit neuerer Hardware auf immer ein und derselben Grundlage/Plattform durchzuführen. Dabei spielt die eigentliche Taktfrequenz kein Rolle, es geht um quasi alle anderen Dinge, die Grundlagenforschung. Aktuell geht man den Weg in Richtung 22-nm-Fertigung, forscht an neuen Speicherlösungen und vielen weiteren Dingen.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!