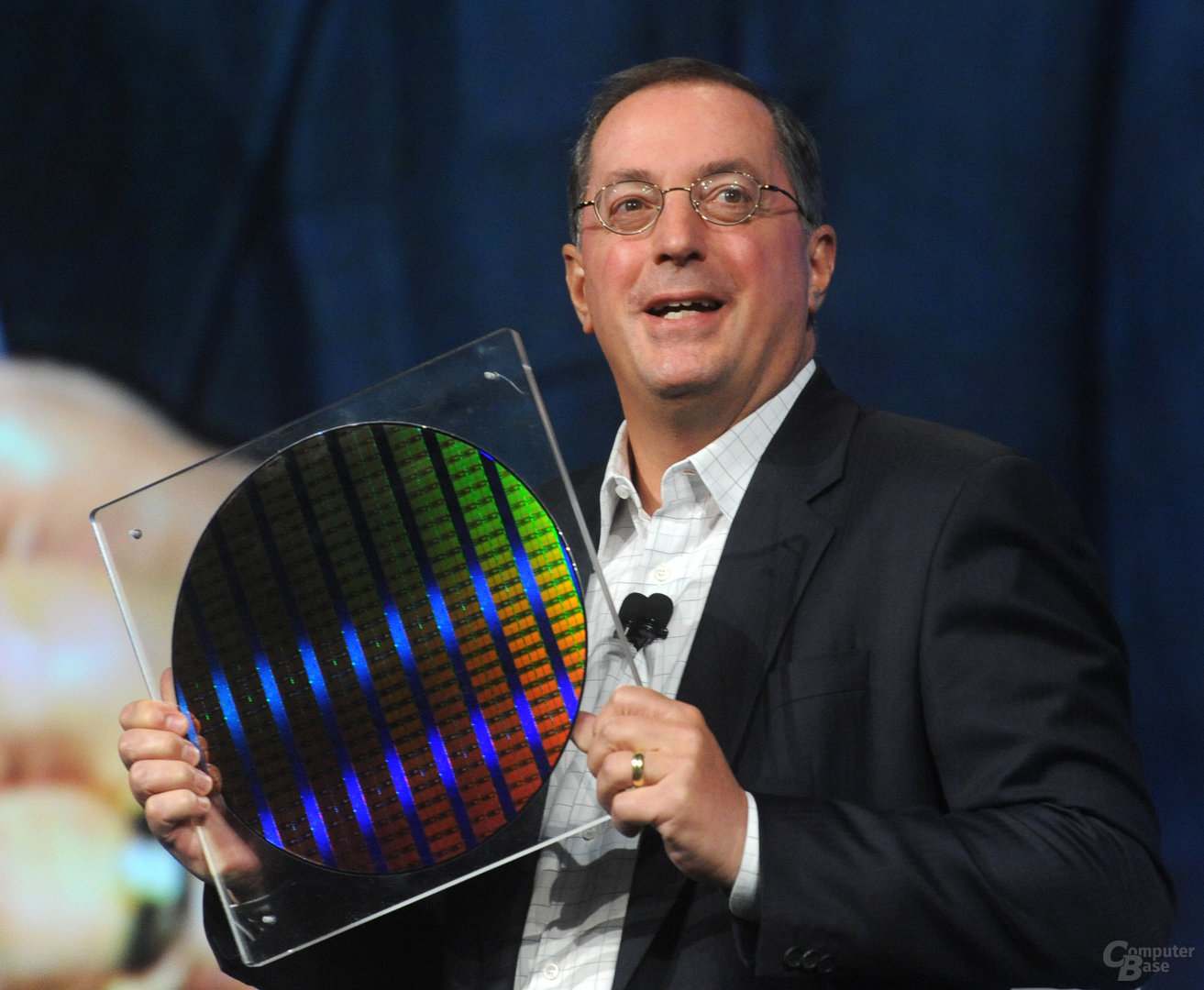

Intel zeigt Testwafer in 22 Nanometer

Intels Präsident und CEO Paul Otellini präsentierte heute auf dem Intel Developer Forum (IDF) in San Francisco den weltweit ersten Silizium-Wafer mit funktionsfähigen Chips, deren Transistoren eine Strukturbreite von 22 Nanometern aufweisen.

Die Test-Chips enthalten Logik und SRAM-Speicher, die in künftigen Mikroprozessoren eingesetzt werden sollen. Der von Otellini gezeigte 22-nm-Wafer besteht aus einzelnen Silizium-Chips mit insgesamt 364 Millionen Bits SRAM-Speicher und verfügt über mehr als 2,9 Milliarden Transistoren auf einer Fläche, die nicht größer ist als ein Fingernagel. Die Chips integrieren die laut Intel bis heute kleinste funktionsfähige SRAM-Zelle mit Ausmaßen von 0,092 Quadratmikrometer. Diese Bauelemente setzen auf die dritte Generation „Hi-k Metal Gate“-Transistortechnologie, die die Leistung steigern und Leckströme reduzieren soll. Erste, im 22-nm-Prozess gefertigte Prozessoren sollen 2012 unter dem Codenamen „Ivy Bridge“ erscheinen.

Otellini teilte zudem mit, dass das 32-nm-Herstellungsverfahren zertifiziert ist und die ersten „Westmere“- Prozessor-Wafer bereits produziert werden. Im Laufe des vierten Quartals 2009 will Intel mit der Herstellung von für den Verkauf bestimmten Prozessoren beginnen. Nach der Umstellung auf das 32-nm-Herstellungsverfahren soll im Jahr darauf Intels neue Mikroarchitektur (Codename „Sandy Bridge“) eingeführt werden. Diese integriert erstmals einen Grafikkern der sechsten Generation (45 nm) und den Prozessorkern (32 nm) auf einem einzigen Silizium-Chip. Zudem verfügt Sandy Bridge über AVX-Instruktionen (Advanced Vector Extensions) für beschleunigte Fließkommaberechnungen sowie Media- und weitere rechenintensive Software.