Initiative für Speicher mit 1 TB/s von Rambus

Einem Bericht von TG Daily zu Folge plant Speicherspezialist Rambus eine Initiative für Speicher mit einer theoretischen Gesamtbandbreite von einem TB pro Sekunde. Die „Terabyte Bandwidth Initiative“ (TBI) soll am Mittwoch vorgestellt werden und zukünftigen Manycore-Architekturen ausreichend Bandbreite zur Seite stellen.

Dabei setzt Rambus wohl auf 16 parallele DRAM-Kanäle, die jeweils mit 16 Gbps und 4 Byte Daten pro Takt arbeiten und es so auf eine theoretische Gesamtbandbreite von einem Terabyte pro Sekunde bringen. Jeder der Kanäle würde dabei eine Gruppe von mehreren Rechenkernen direkt bedienen. Bislang soll es laut TG Daily noch keinen voll funktionsfähigen Prototypen geben. Rambus habe aber einen in 65 nm gefertigten Prototypen, der es mit einem Speicherkanal bereits auf die veranschlagte Bandbreite von 64 GB/s bringt.

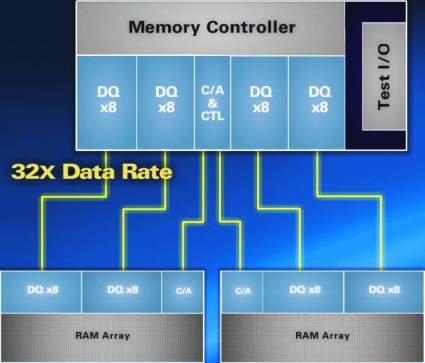

Um die Taktfrequenz von 16 Gbps pro Kanal zu erreichen, soll Rambus auf den Chips das PLL-basierte FlexLink Taktungssystem einsetzen. Durch den PLL wird der Eingangstakt von 500 MHz auf die 32fache Übertragungsrate von 16 Gbps geschraubt. Zudem setzt man erstmals auf eine vollständig differenzielle Speicherarchitektur (Fully Differential Memory Architecture – FDMA) für das Signalsystem (Command/Adress-, Daten- und Taktsignal), die zusammen mit Rambus' FlexPhase-Technologie, die die hohen Taktfrequenzen exakt mit den Daten abgleichen soll, trotz der hohen Taktraten die Zahl der Übertragungsfehler niedrig halten soll. Weiterhin soll Rambus den Command/Address-Bus neu gestaltet haben. Im Gegensatz zu aktuellen DRAM-Chips mit zwölf Anschlüssen zwischen DRAM und Controller soll TBI nach Bedarf skalierbar nur zwei Anschlüsse nutzen, die aber ebenfalls bei 32fachem Takt arbeiten. Dies soll in erster Linie günstigere „System on Chip“-Systeme ermöglichen und gleichzeitig die Unterstützung für verschiedene Granularitäten (d. h. wie viel Speicher pro Anfrage abgerufen wird, typischerweise 64 oder 128 Byte) erhöhen. Durch die zusätzliche Bandbreite der 32fachen Anbindung sollen ohne Einfluss auf Durchsatz oder Latenz niedrigere Granularitäten möglich sein.

Die Massenproduktion des neuen Speichers soll Rambus für 2010 oder 2011 anvisiert haben, wobei der Stromverbrauch und die damit einhergehende Hitzeentwicklung derzeit die Hauptprobleme darstellen sollen. Daher müssten erste Produkte zumindest im 45-nm-Prozess hergestellt werden. Weitere Informationen zur Terabyte Bandwidth Initiative soll es am Mittwoch auf dem Rambus Developer Forum in Tokio geben.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!