Qimonda: Speicherfahrplan bis 30-nm-Fertigung

Die Qimonda AG hat in einem offenen Webcast in der letzten Nacht ihre Technologie-Roadmap bis zur 30 nm-Generation für DRAM-Speicherchips mit Zellgrößen von bis zu 4F² vorgestellt. Die neue „Buried Wordline DRAM“-Technologie von Qimonda soll hohe Leistungsfähigkeit, niedrigen Stromverbrauch und kleine Chipgrößen miteinander kombinieren.

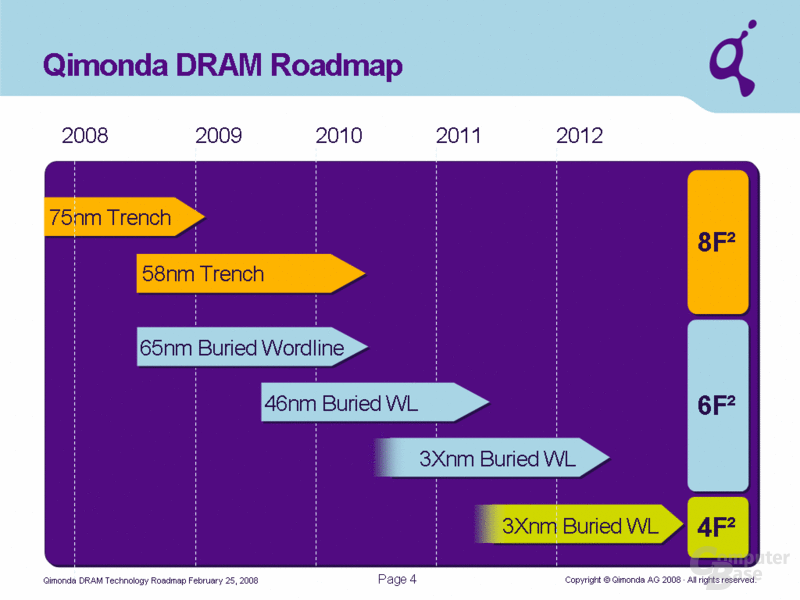

Die neue Technik soll die weitere Entwicklung des diversifizierten Produktportfolios des Unternehmens vorantreiben. Qimonda führt diese Schlüsseltechnologie jetzt für Strukturbreiten von 65 nm ein. Der Produktionsbeginn für 1-Gbit-DDR2-Speicherchips ist für die zweite Jahreshälfte des Kalenderjahres 2008 geplant. Qimonda ist nach eigenen Angaben das erste Unternehmen in der Industrie, das eine Technologie-Roadmap zur Einführung der 30 nm-Generation vorlegt, die kleinste Zellgrößen von 4F² ermöglichen und voraussichtlich ab 2011 Einzug halten wird.

Qimonda plant den Start der Massenfertigung seiner 46 nm Buried Wordline-Technologie für die zweite Jahreshälfte 2009. Diese Strukturbreite ermöglicht mehr als doppelt so viele Bits pro Wafer im Vergleich zur 58 nm Trench-Technologie. Für die Umstellung von der aktuellen Trench-Technologie auf die Buried Wordline-Technologie erwartet Qimonda einen zusätzlichen, einmaligen Investitionsaufwand in Höhe von etwa 100 Millionen Euro in den Geschäftsjahren 2009 und 2010, der voraussichtlich über den Cashflow finanziert wird. Dieser relativ geringe zusätzliche Investitionsaufwand resultiert aus der Kombination von Qimondas Buried Wordline und vereinfachten Fertigungsprozessen mit einem marktüblichen Stack Kondensator.