„Bulldozer“: Details zu Turbo, Cache, Verbrauch & Co.

Seit dem gestrigen Financial Analyst Day ist bekannt, dass die ersten „Bulldozer“-CPUs im zweiten Quartal 2011 zu erwarten sind. Zu den etwas später folgenden Server-Varianten von „Bulldozer“ gab AMD zum Abschluss weitere Details preis. Darunter sind Angaben zu den Produktnamen, dem Turbo-Modus, der TDP/ACP, dem Cache und mehr.

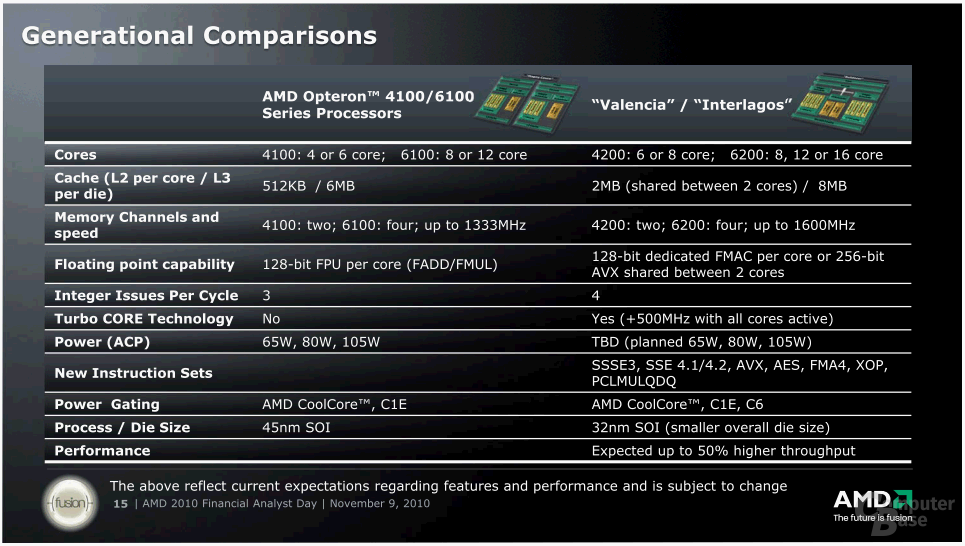

Wie bereits bekannt war, sollen die „Bulldozer“-Prozessoren mit den Codenamen „Interlagos“ und „Valencia“ die aktuellen Opteron-6100/4100-Modelle beerben, dabei aber auf die gleichen Sockel (G34/C32) setzen. „Interlagos“ soll dann mit 8, 12 oder 16 Kernen als Opteron 6200 erscheinen, während „Valencia“ mit 6 oder 8 Kernen die Bezeichnung Opteron 4200 erhält. Die Informationen, dass „Bulldozer“ mit acht Kernen über 16 MB Cache verfügen wird, werden nun offiziell bestätigt: Pro Die stehen 8 MB L3-Cache zur Verfügung, dazu gesellen sich pro Modul mit zwei Integer-Cores jeweils 2 MB L2-Cache. Damit ergeben sich beim „Orochi“ mit acht Kernen eben insgesamt 16 MB Cache (ohne L1-Cache). Das Flaggschiff mit 16 Kernen als Multi-Chip-Package (MCP) mit zwei Dies, kommt somit sogar auf insgesamt 32 MB L2- und L3-Cache, wie John Fruehe von AMD in seinem Blog bestätigt.

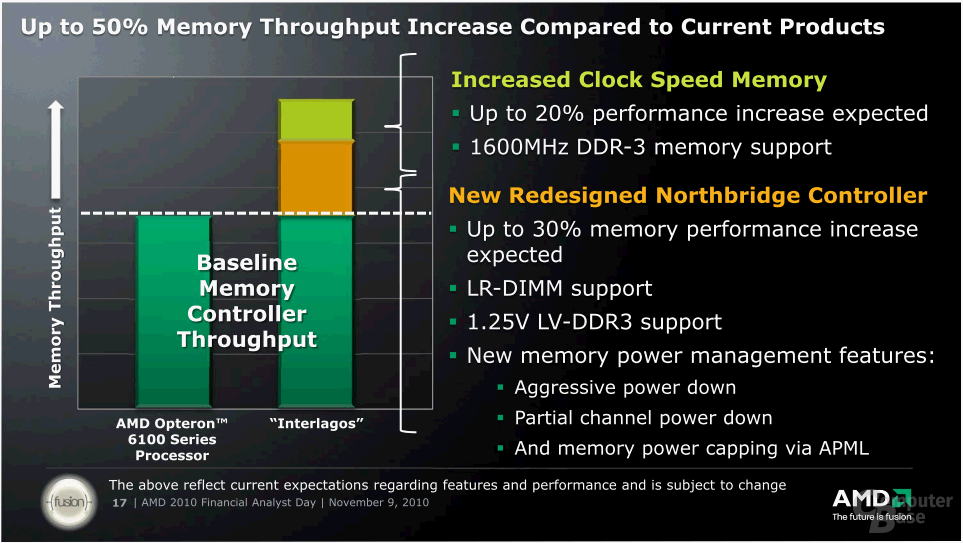

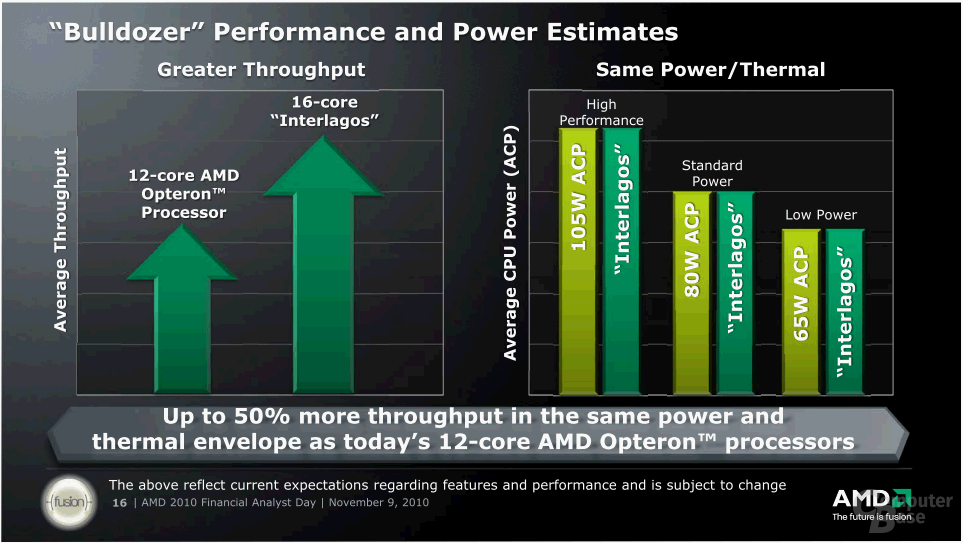

Der integrierte Speichercontroller wurde im Vergleich zu den Vorgängern optimiert und soll in Kombination mit schnellerem DDR3-1600-Speicher bis zu 50 Prozent mehr Leistung/Bandbreite bieten sowie einige neue Stromsparfeatures. Die ACP/TDP, immer auch ein Indiz für die Leistungsaufnahme und somit den Verbrauch, der neuen Opterons soll sich in den gleichen Stufen gliedern, wie bei den Vorgängern, womit man je nach Leistungsklasse eine „Average CPU Power“ (ACP) von 65, 80 oder 105 Watt anpeilt. Diese Werte sind aber noch nicht final. Zu den Taktraten der Prozessoren macht AMD leider noch gar keine Angaben. Allerdings gibt man nun bekannt, dass die Server-CPUs über einen Turbo-Modus verfügen, der den Takt dynamisch um 500 MHz oder mehr anhebt – und das sogar für alle Kerne.

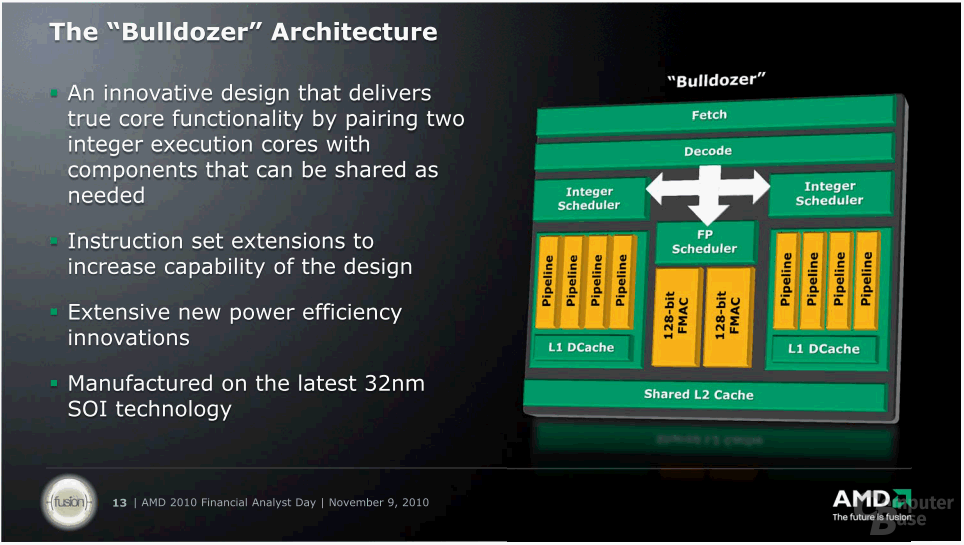

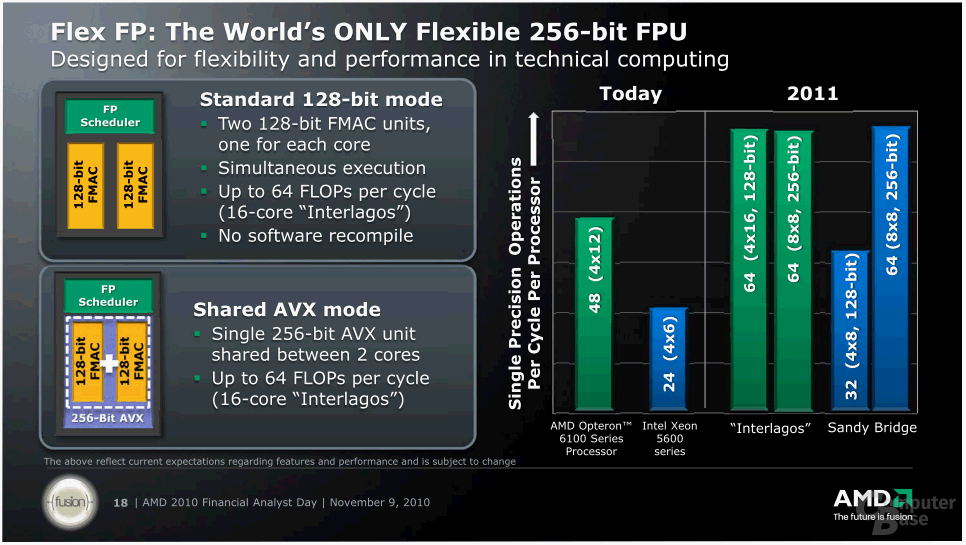

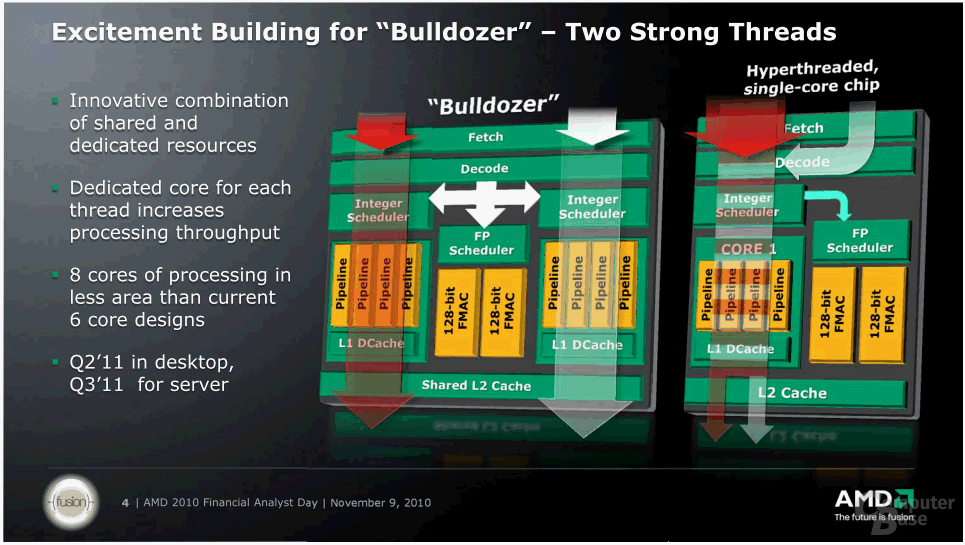

Die neue 256-Bit-FPU für Gleitkommaberechnungen, die AMD „Flex FP“ nennt, ist bereits bekannt. Sie soll je nach Anwendungsbedarf entweder beiden Kernen eines Moduls jeweils als 128-Bit-Einheit (dedicated) dienen oder als vollwertige 256-Bit-Einheit fungieren, die sich die Kerne allerdings teilen müssen. Im Bereich der Integer-Berechnungen nennt AMD nun die Zahl von vier Integer Issues pro Taktzyklus, während es beim Vorgänger nur deren drei sind. Die weiteren Daten mit den neuen Befehlssatzerweiterungen, dem verbesserten Power Gating sowie der neuen 32-nm-Fertigung (SOI + HKMG) sind ebenfalls schon länger bekannt.

Wie wir bereits berichteten, wird „Bulldozer“ nun doch etwas früher als zuletzt erwartet erscheinen. Während dabei „Zambezi“ für das Desktopsegment im zweiten Quartal 2011 den Anfang machen soll, werden die neuen „Bulldozer“-Opterons wohl erst im dritten Quartal folgen. 2012 sollen dann sogar Modelle mit bis zu 20 Kernen folgen, die aber auf einer verbesserten „Bulldozer“-Architektur basieren werden.

Weitere Berichterstattung zum Financial Analyst Day von AMD:

- AMDs erster „Fusion“ bereits mit 100+ „Design Wins“

- AMD will im Notebook-Markt verstärkt angreifen

- AMD kündigt 20-Kern-Prozessor für 2012 an

- AMD zeigt neue Desktop-Prozessor-Roadmap

- Notebook-Roadmap von AMD bis 2012 im Detail

- „Bulldozer“ von AMD fährt ab dem 2. Quartal

- Ausblick auf Zukunft von „Bulldozer“ und „Bobcat“

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!