IDF: 1,7 Mrd. Transistoren bei nur 100 Watt

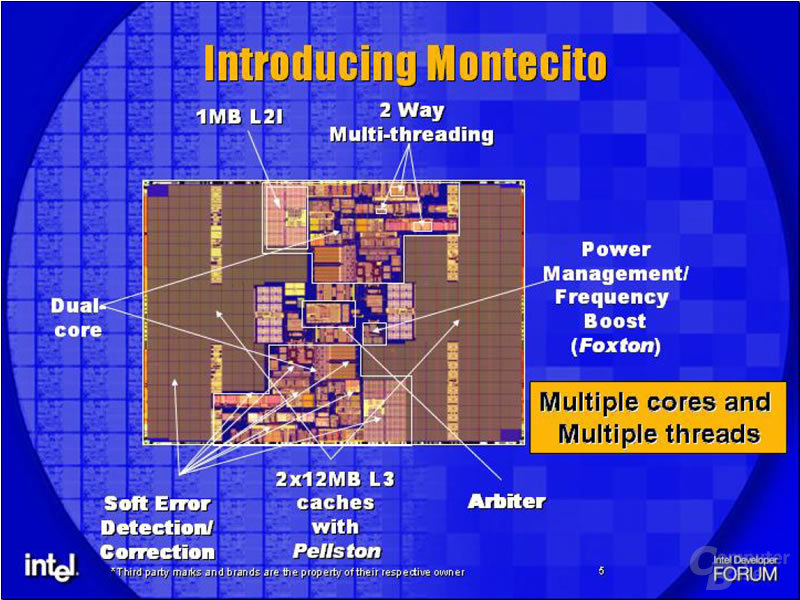

Intel hat im Rahmen diverser Präsentationen weitere Details zum kommenden Dual-Core-Itanium-Prozessor „Montecito“ preisgegeben. So hat sich der Prozessorhersteller aus dem sonnigen Kalifornien dafür entschieden, jedem Prozessorkern seinen eigenen 12 MB großen Cache zur Verfügung zu stellen.

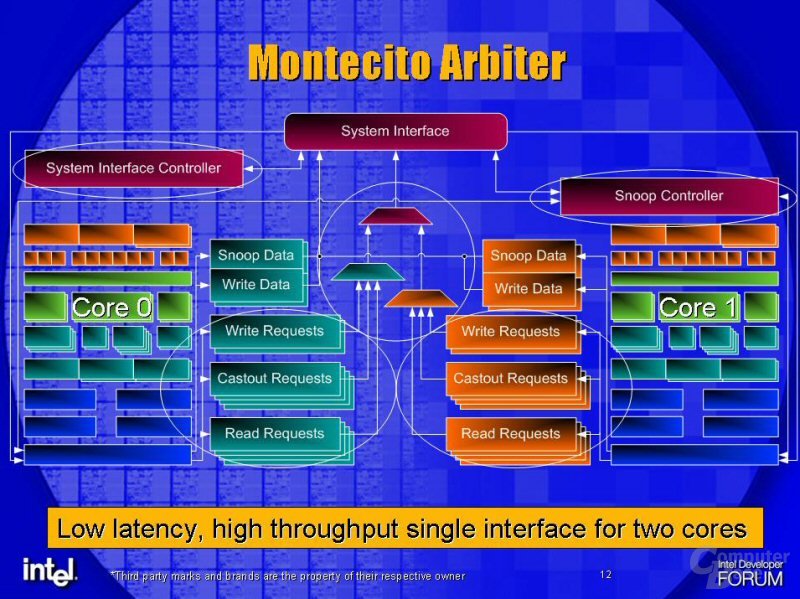

Damit hat man für den Montecito einen Weg gewählt, den auch AMD bei seinen kommenden Dual-Core-Opteron- und Athlon 64-Prozessoren eingeschlagen wird. Allerdings scheint Intel in Sachen Cache-Architektur zweigleisig zu fahren, denn bei den kommenden Dual-Core-Produkten hat man eine andere Cache-Lösung in Aussicht gestellt. Die Gerüchteküche spricht hier von einem gemeinsamen Cache. Doch zurück zum Montecito. Um die Kohärenz - also die Gültigkeit der Daten - zwischen beiden getrennten Caches herstellen zu können, kommt ein sog. Arbiter zum Einsatz, der den Inhalt beider Speicher überprüft und auf dem aktuellen Stand hält. Schließlich wäre es unglücklich, wenn der erste Prozessorkern Daten aus dem Speicher liest, diese verändert und der zweite Kern, der diesen Datenblock ebenfalls bei sich im Cache abgelegt hat, nichts davon mitbekommt und noch mit den inzwischen veralteten Werten rechnet.

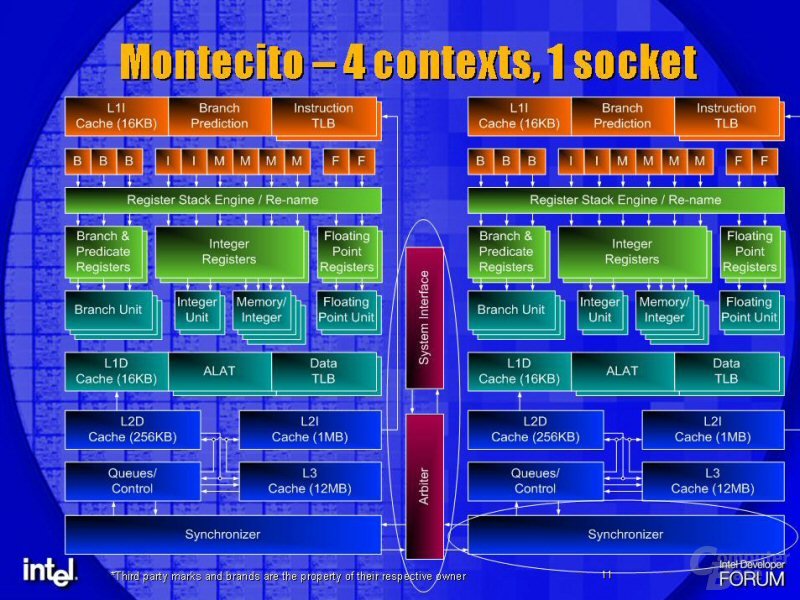

Die 12 MB L3-Caches jedes Kerns werden von einem (offenbar) exklusiv verwalteten 1 MB L2-Cache für Instruktionen und 256 KB fassenden L2-Cache für Daten erweitert. Entgegen bisheriger Cache-Lösungen von Intel scheint es sich nicht um eine „Inclusive Cache“-Lösung zu handeln, bei der der komplette L1 im L2 und der L2 auch im L3 vorhanden war. Damit würde sich der effektiv verfügbare Cache auf 26,5 MB erhöhen. Wir könnten es also mit einem Victim-Cache zu tun haben. Wir werden versuchen, diese Frage im laufe des heutigen Tages zu klären.

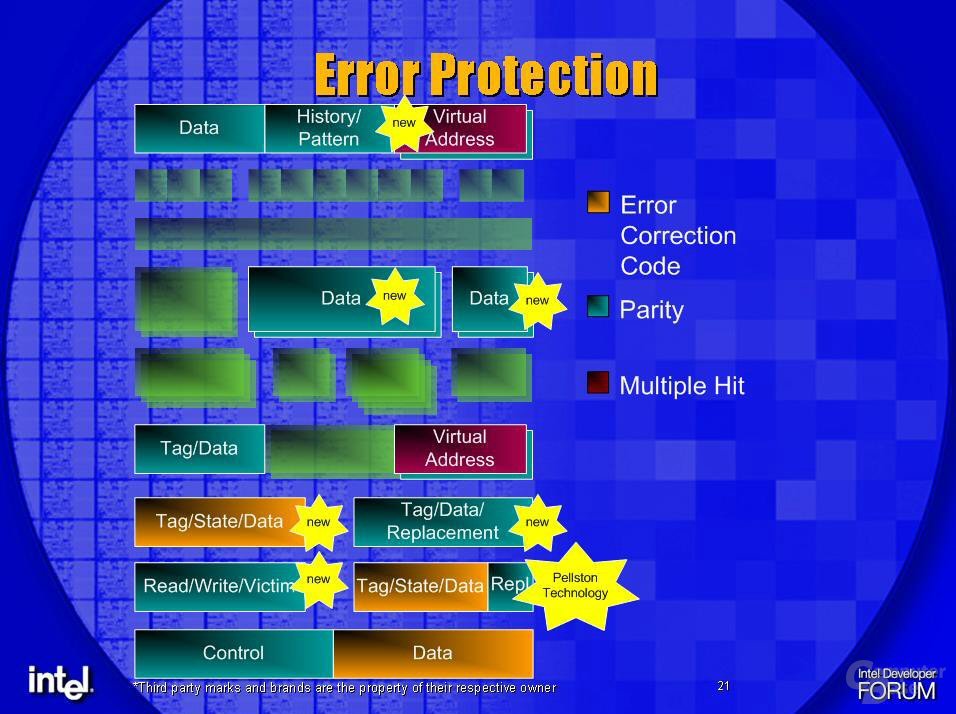

Der Montecito kann mit der Foxton-Technologie für das Last-bezogene Übertakten, der Pellston-Technologie, durch die defekte Cache-Bereiche automatisch deaktiviert werden, und der Silvervale-Technologie, die es ermöglicht, mehrere Betriebssysteme parallel und zu gleichen Zeit auszuführen, aufwarten.

Zusätzlich zu den zwei Prozessorkernen bietet jeder Kern des Montecito Multi-Threading, so dass dem Betriebssystem letztendlich vier virtuelle Prozessoren zur Verfügung stehen. Die Verteilung der Ressourcen wird dabei dynamisch erfolgen.

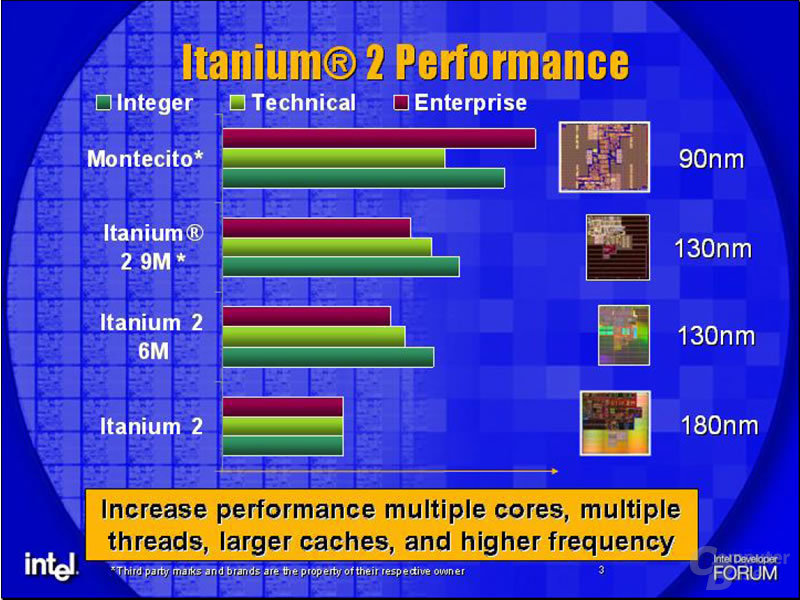

Zum Abschluss seien noch einige zahlen genannt: Der in 90 nm gefertigte Itanium 2-Prozessor, der mit insgesamt 1,7 Mrd. Transistoren aufwarten kann und damit mehr als zehn mal so viele Transistoren wie der Pentium 4 „Prescott“ besitzt, kommt mit einer Thermal Design Power (TDP) von lediglich 100 Watt daher! Offensichtlich lassen sich mit 90 nm also doch stromsparende Prozessoren produzieren - nur beim 115 Watt verschlingenden und mit derzeit 3,6 GHz schnellsten Pentium 4 560 scheint das nicht ganz geklappt zu haben.