IDF: Intel zeigt 6,26 GHz „Polaris“ mit 2 Teraflops

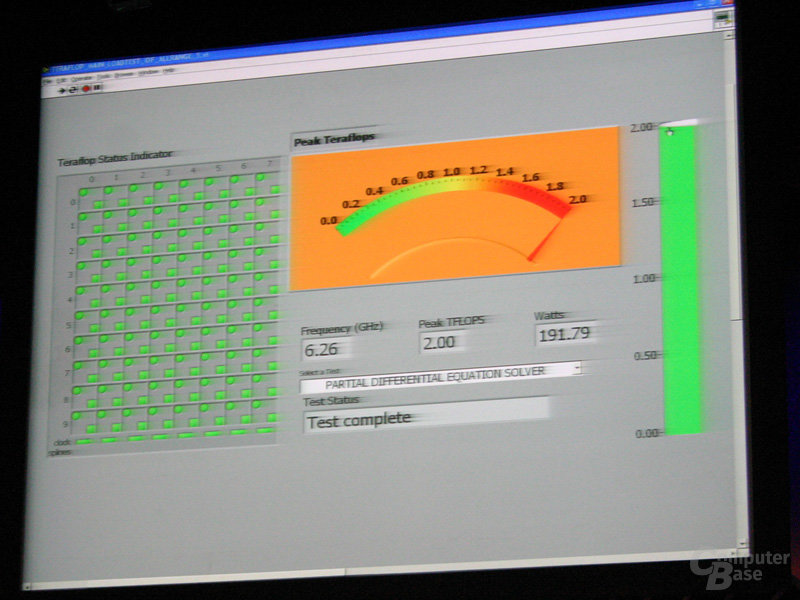

Prozessorhersteller Intel hat im Rahmen des Intel Developer Forum Spring 2007 in Beijing seinen Terascale-Testchip „Polaris“ auf 6,26 GHz beschleunigt und konnte dem Chip dadurch eine Höchstleistung von 2 Teraflops entlocken.

Der Stromverbrauch des mit 80-Kernen ausgestatteten System stieg dabei auf 191,79 Watt an. Zum Durchbrechen der 1-Teraflops-Marke sind bei einem Takt von 3,16 GHz dagegen nur 62 Watt erforderlich. Das im Februar 2007 im Zuge der Vorstellung von Polaris veröffentlichte und bislang beste Ergebnis wurde mit 1,81 Teraflops bei einem Takt von 5,7 GHz und eine Verbrauch von 265 Watt eingefahren. Intel hat die vergangenen zwei Monate genutzt, um den Takt zu steigern und den Stromverbrauch nicht unerheblich zu senken.

Polaris ist ein experimenteller Prozessor mit dem Intel verschiedene Wege erforscht, möglichst viele Kerne auf einem Siliziumchip zu integrieren. Hierfür wurde ein Kommunikationsnetz geschaffen, dass die verschiedenen Kerne untereinander verbindet. Da Polaris noch keinen Cache besitzt, müssen die Befehle, die jeder Kern abzuarbeiten hat, direkt in die Befehlsschlange des Prozessors geladen werden. Die ermittelte Performance hat daher einen höchst synthetischen Charakter. Andererseits sorgen in modernen Prozessoren verschiedene Prefetcher dafür, dass die Caches die Daten und Instruktionen bei der Ausführung direkt zur Verfügung stehen. So dass sich die Ausführung von Befehlen in Polaris wiederum den von normalen (verfügbaren) Prozessoren etwas annähert.

Eine Besonderheit von Polaris, auf die wir bislang noch nicht eingegangen sind, ist, dass der Takt nicht synchron über den Chip verteilt wird. Hierzu muss man wissen, dass bei vollständig synchron (mit einem Takt) arbeitenden Prozessoren einen äußert aufwendige Schaltung zur Verteilung des Taktsignals benötigt wird (idealerweise H-Clock-Tree), auf die, je nach Design, bis zu 40 Prozent des gesamten Stromerverbrauchs entfallen. Polaris dagegen besitzt einen sogenannten Mesochronen-Takt, bei dem jeder der 80 Kerne für sich zwar synchron arbeitet, die Kommunikation untereinander jedoch durch kleine Bufferspeicher synchronisiert wird. Die Verdrahtung für die Verteilung des Prozessortakts wird dadurch wesentlich vereinfacht. In Folge dessen kann der Stromverbrauch des Clock-Netzes auf unter zwei Prozent reduziert werden. Dieser Vorteil überwiegt den Nachteil der ggf. um einen Takt verzögerten Datenübertragung bei weitem und wird daher auch bei zukünftigen Projekten dieser Art Verwendung finden.