IDF: Polaris 2 mit IA und Larrabee mit IA++

Justin Rattner hat bereits Pläne für einen Polaris-Nachfolger. Beim Polaris 2, der weiterhin ein Chip für Experimente sein wird, will man den derzeit auf Floating-Point ausgelegten Spezialbefehlssatz auf ein Derivat von x86 (IA-32, Intel Architecture)* umstellen, um so Anwendungen mit größerem Realitätsbezug erproben zu können.

Außerdem sollen die 5-Port-Router der einzelnen Kerne ein breiteres Businterface erhalten, um sich einem massentauglichen Produkt weiter anzunähern. Schließlich ist diese Verbindung in Polaris 1 mit einem 36 Bit breiten Datenbus (mit Double Data Rate und vollem Prozessortakt) den späteren Aufgaben nicht gewachsen.

Wo Polaris 1 nur mit einem 3 KByte großen Befehls- und 2 KByte großen Datenspeicher aufwarten kann, wird Polaris 2 sehr wahrscheinlich zusätzlich mit einem Cache ausgerüstet werden. Bereits jetzt ist beim Router der Anschluss von Speicher vorgesehen. Derzeit hat Intel den Einsatz von 3D Stacked Memory auf der Roadmap, wobei parallel jedoch immer Alternativen in Betracht gezogen werden.

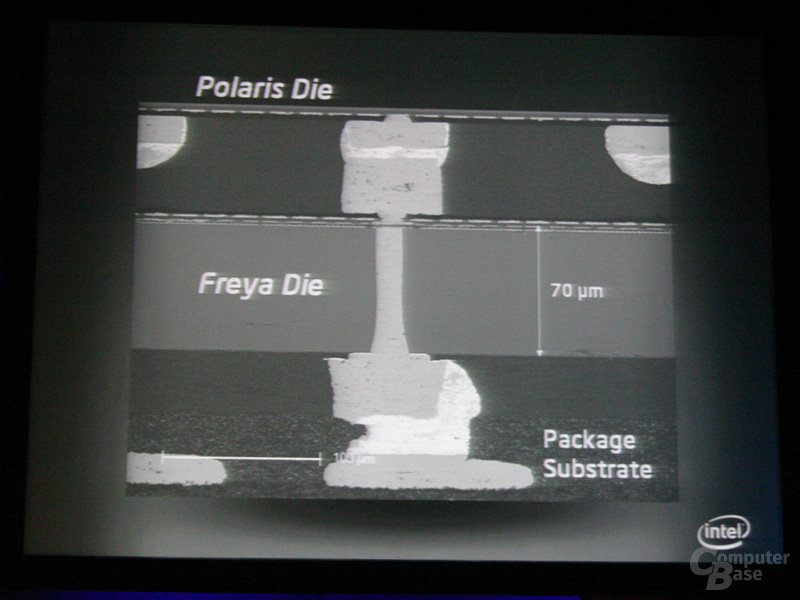

Wie sich Intel den Einsatz von 3D Stacked Memory vorstellt, hat man im Rahmen des Intel Developer Forum 2007 Spring bekannt gegeben. Demnach soll Polaris (2) auf der vollen Fläche mit einem darüber liegendem SRAM-Speicher (Codename Freya) verbunden werden – es wird gestapelt („stacked“). Jeder der aktuell 80 Prozessorkerne erhält somit direkten Zugang zum Cache.

„Freya“ wird sich unter Polaris befinden. Hierdurch soll eine bessere Wärmeableitung für den Prozessor-Chip gewährleistet werden. Damit Polaris Kontakt zum Sockel hat, soll „Freya“ aufwendig herzustellende Durchkontaktierungen (Through Silicon Vias) besitzen. Die beiden Chips werden dann über ebenso komplizierte, hunderte von „Ball“-Kontakten miteinander verbunden.

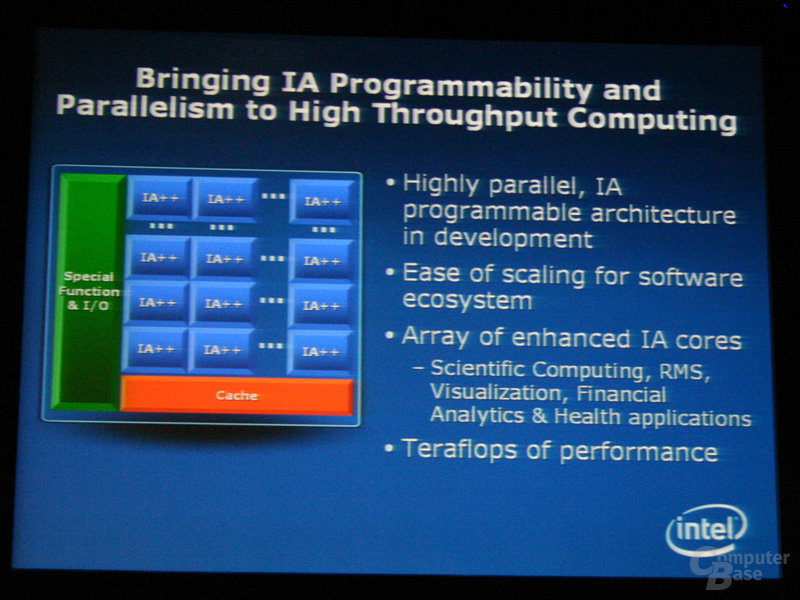

Die Forschungsergebnisse in Polaris und dem bis Ende 2007 erwarteten Polaris 2 kommen dem in der Vergangenheit heiß diskutierten Larrabee-Projekt zu Gute, welches als echtes Produkt in den Handel kommen soll. Als hochleistungsfähige Grafikkarte erwartet, hat Pat Gelsinger diesen Einsatzzweck in seiner Rede nur als einen von vielen genannt. Larrabee wird mit „IA++“-Kernen bestückt sein, die für wissenschaftliches Rechnen, Visualisierungen (ein Hinweis auf 3D-Grafik?) oder andere Anwendungen im Bereich Gesundheit und Analyse angesiedelt sind. Die Performance soll Polaris-typisch im Teraflop-Bereich liegen.

Außerdem soll Larrabee einen Einheitenblock mit speziellen Funktionen besitzen. Hier wäre z.B. ein optischer Siliziumtransceiver (Sender und Empfänger) für die Kommunikation mit der Außenwelt denkbar. An entsprechenden Lösungen wird im Rahmen der Tera Scale-Forschung gearbeitet.

* Justin Rattner hat allgemein den Support von Intel Architecture (IA) in Polaris 2 bestätigt. Neben dem geläufigen IA-32 (x86; derzeit geläufig) hat das Unternehmen jedoch auch das im Itanium eingesetzte Programmiermodell IA-64 im Portfolio, das mit IA-32 nichts gemein hat.