Weitere Details zu Intels „Nehalem“

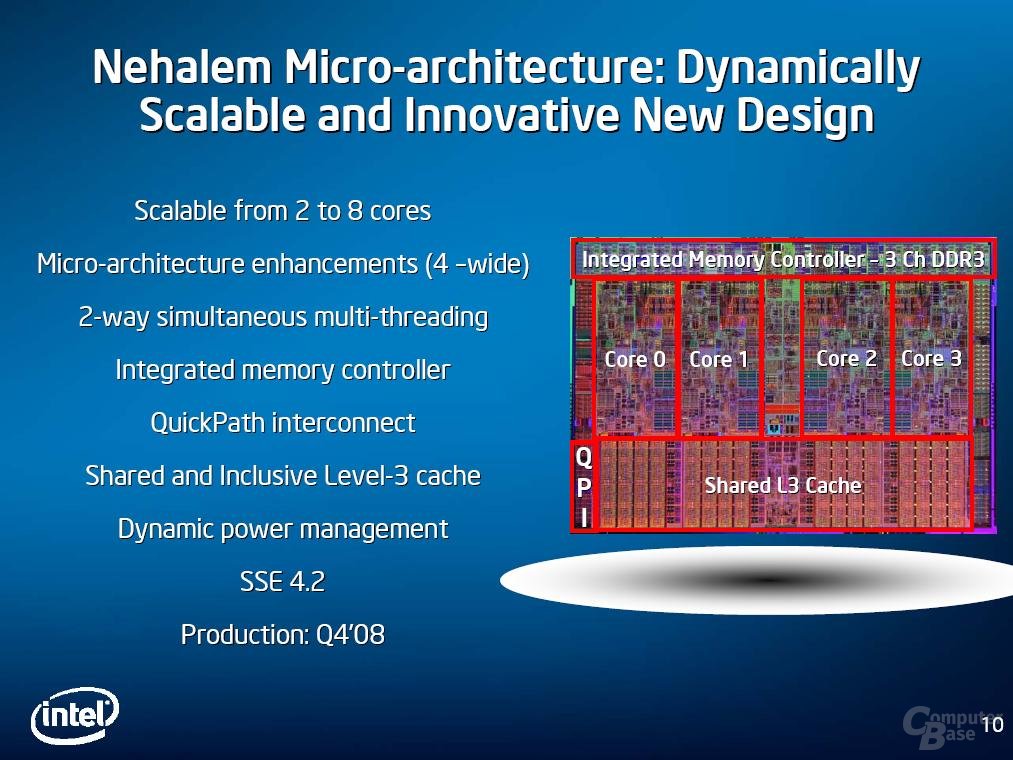

In einem neuen Dokument hat Branchenprimus Intel weitere Details zu ihrer kommenden Prozessor-Generation und Architektur unter dem Codenamen „Nehalem“ verraten. Dazu gehören unter anderem neue Informationen zur Cache-Struktur und zahlreiche interne Verbesserungen.

Anders als bei den aktuellen Penryn-Prozessoren mit 3, 6 oder gar 12 Megabyte gemeinsamen L2-Cache, hat Intel beim Nehalem nur 256 kByte dedizierten L2-Cache pro Prozessor-Kern vorgesehen. Im Gegensatz dazu erweitert man die Cache-Hierarchie um einen zusätzlichen komplett gemeinsamen 8 MB große L3-Cache (voll inklusive). Dank des Baukasten-Prinzips lässt sich die Nehalem-Architektur von zwei bis hin zu acht CPU-Kernen skalieren und gibt somit genug Spielraum nach oben. Mit 731 Millionen Transistoren besitzt der Nehalem sogar fast 100 Millionen Transistoren weniger als Intels aktueller „Yorkfield“ Prozessor, was in erster Linie auf die geschrumpfte Gesamtmasse an Cache von 12 (L2-Cache) auf 9 MB (L2 + L3-Cache) zurückzuführen ist.

Zu den Detailverbesserungen in der Architektur gehören neben einem komplett neuen Second-Level Translation Look-aside Buffer (TLB) mit 512 zusätzlichen Einträgen auch ein neuer Second-Level Branch Target Buffer sowie ein neuer Renamed Reture Stack Buffer. Während ersterer für eine verbesserte Übersetzung der logischen in physikalische Speicher-Adressen sorgt, soll der neue Branch Target Buffer eine höhere Trefferquote bei der Sprung-Vorhersage (Branch Prediction) erzielen. Zudem besitzt der Nehalem eine bessere Parallelisierung, sodass jetzt bis zu 128 Micro-Ops „in flight“ möglich sein. Dies ist auch nötig, da dank Simultanous Multi-Threading nun wieder zwei Threads pro Kern gleichzeitig verarbeitet werden können. Der neue QuickPath Interconnect liefert eine Bandbreite von maximal 25,6 Gigabyte pro Sekunde und geht damit doppelt so schnell zu Werke wie Intels aktueller Frontside-Bus mit 1600 MHz. In Zwei-Prozessor-Umgebungen wird die nutzbare Transferrate sogar vervierfacht.

Laut Intels eigenen Angaben erreicht der integrierte Triple-Channel DDR3-1333 Controller des Nehalem eine bis zu vier Mal höhere Bandbreite als der aktuelle Quad-Channel-Speicher-Controller des i5400 Chipsatzes mit Fully-Buffered DIMMs. Der neue Speicher-Controller unterstützt dabei sowohl registered, als auch unbuffered Module. Alle weiteren Details sowie einen Überblick über die einzelnen Modelle haben wir bereits am Anfang des Jahres in einem kleinen Bericht zusammengestellt.