Intel Yorkfield & Wolfdale: Auf M0 folgt R0

Nachdem in den letzten Tagen zuerst die Xeon-Server-Prozessoren mit einem neuen Stepping versorgt wurden und kürzlich die ersten Dual-Core-Desktop-Prozessoren folgten, ist nun klar, was mit den fehlenden Prozessoren passiert. Auch sie bekommen ein neues Stepping spendiert.

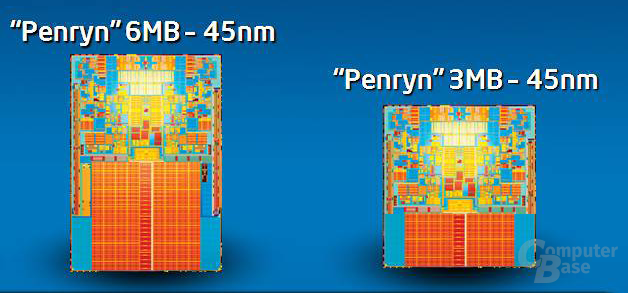

Gemeint ist dabei in erster Linie die Serie der Wolfdale-Prozessoren, unter anderem in Form des Core 2 Duo E7200, die nur mit 3 statt 6 MB L2-Cache daherkommen. All' diese Prozessoren, auch die Quad-Core-Modelle Q9300 und der zukünftige Q9400, die auf zwei dieser Wolfdale-Prozessoren basieren, sollen in Kürze im R0-Stepping erscheinen und damit das M0-Stepping ablösen. Damit ist auch klar, dass die restlichen Yorkfield-Prozessoren mit 12 MB Cache wie die Xeon-Prozessoren und die Core 2 Duo E8500 und E8400 ebenfalls das E0-Stepping bekommen werden.

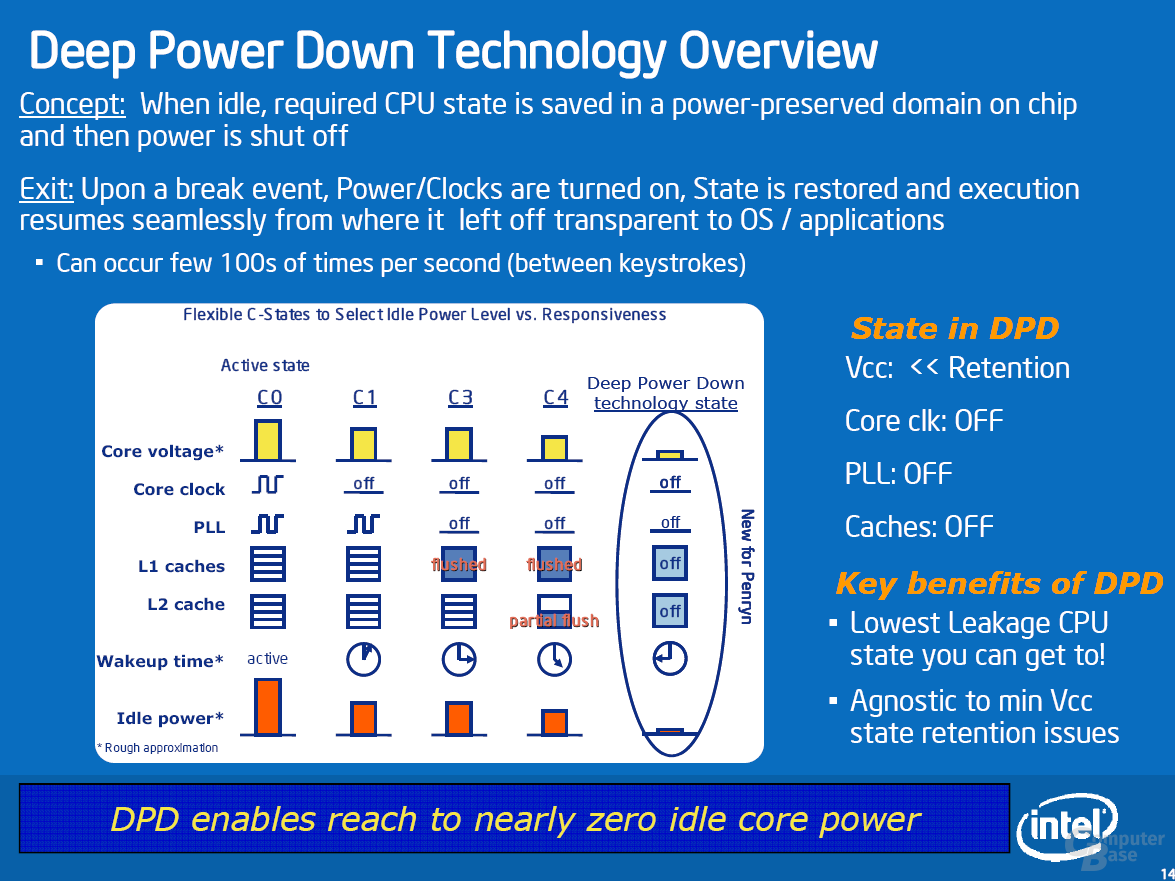

Im Zuge der Änderungen am Stepping wird es in Form des Features des „Power Status Indicator“ (PSI) eine Neuerung geben, die jedoch Änderungen an den Hauptplatinen erfordert – wohl ein Fingerzeig in Richtung der Eaglelake-Platinen, die in den kommenden Wochen den Markt erreichen und jenes Feature wohl unterstützen. Was genau diese Neuerung im Einzelnen bei den Desktop-Prozessoren leisten soll und in der Realität letztendlich bewirkt, wird sich erst zeigen müssen. Primär wird es wohl die Ergänzung zu den bestehenden Energiesparmodi der „C-States“ (C1E, C2E, C3 und C4) sein, die teilweise bei den kommenden R0-Prozessoren erst nachgerüstet werden, da das bisherige M0-Stepping nur C1E beherrschte. Diese Features, auch PSI, sind schon von mobilen Prozessoren der Core-Familie und auch den noch etwas älteren Merom-Prozessoren bekannt; alle dienen der Senkung des Energiebedarfs. Inwiefern es daraus folgend (wünschenswerte) offizielle Senkungen im Bereich der Leistungsaufnahme oder der Angabe der TDP durch diese Features geben wird, wie es die Xeon-Prozessoren vormachen, bleibt abzuwarten. Als krönender Abschluss sollen die zwei neuen Instruktionen XSAVE/XRSTOR zu den SSE-Befehlen der Prozessoren stoßen.