Infineon optimiert Chipfertigung

Infineon hat einen neuen Testchip hergestellt, mit dem die Fertigungsprozesse von komplexen Halbleitern kontrolliert und verbessert werden können. Diese Neuentwicklung ist das Ergebnis einer mehrjährigen engen Kooperation mit der Fachhochschule Regensburg.

Mit dem Testchip können Prozessabläufe jetzt mit einer bisher nicht erreichten Präzision überprüft und die Funktionsfähigkeit der Mikrochips durch Messungen schon während des Herstellungsprozesses optimiert werden. Damit werden eventuelle Fehler schneller erkannt, die Produktivität erhöht und die Fertigungskosten gesenkt. Außerdem liefert der Testchip die erforderlich hohe statistische Genauigkeit, um auch selten auftretende Fertigungsprobleme zu erfassen. Der Testchip basiert auf einem innovativen Schaltungskonzept, das von der FH Regensburg entwickelt wurde. Die volle Funktionsfähigkeit konnte jetzt nachgewiesen werden. Der Testchip wird zunächst in der Regensburger Wafer-Fertigung von Infineon und später auch in anderen Produktionsstätten zum Einsatz kommen. Er besteht im Wesentlichen aus einer intelligenten und universellen Adressierungsschaltung und einem Array von Teststrukturen. Der Chip basiert auf einem 0,35-µm-CMOS-Prozess und wird auf 8-Zoll-Wafern gefertigt. Auf dem Chip mit seiner speicherähnlichen Struktur sind auf nur sechs Quadratmillimetern mehr als 1,2 Millionen Transistorfunktionen integriert.

Doch wie funktioniert dieser Chip nun wirklich?

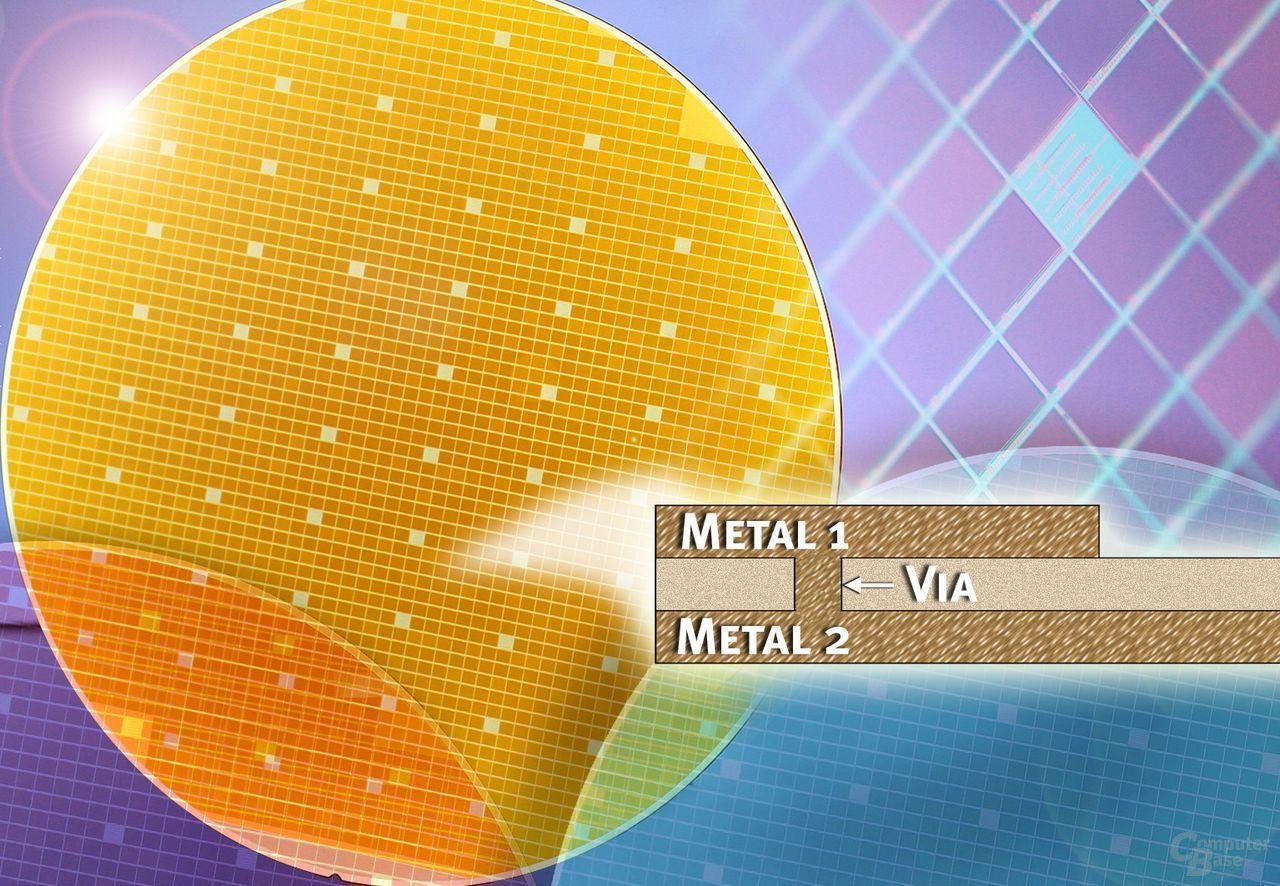

Mit dem jetzt realisierten Testchip werden Vias - das sind die leitenden Verbindungen zwischen zwei Metallisierungsebenen - untersucht. Da in einem ausgereiften CMOS-Prozess die typische Ausfallwahrscheinlichkeit für die hier untersuchten Vias nur bei etwa 10 bis 20 ppb (parts per billion) liegt, müssen ausreichend viele Testdaten für eine statistische Auswertung vorliegen. Der Testchip hat dazu ein Array mit 512 x 512 Vias (262 144) mit den dazugehörigen Auswahltransistoren für die Adressierung integriert. Auf einem Wafer wurden 60 Belichtungsblöcke mit je 42 Testchips abgebildet, das sind 2.500 Testchips/Wafer und damit etwa 640 Millionen Vias. Jedes Via ist einzeln adressierbar und sein elektrischer Widerstand sowie der Spannungsabfall am Via können genau gemessen werden.

Die Funktionsfähigkeit des Testchips wurde durch die Ermittlung von gezielt präparierten Via-Defekten mit einem Tester nachgewiesen. Durch die Adressierung konnten die Fehler auf dem Chip genau lokalisiert werden. Der Via-Array-Testchip stellt damit ein äußerst empfindliches Testinstrument zur Überwachung der Fertigungsprozesse im Via-Bereich dar. Bereits minimale Prozessveränderungen beeinflussen das elektrische Verhalten der Vias und können mit einer einfachen Messung am Tester erfasst werden. Das Testchip-Konzept wird in Kooperation mit der FH Regensburg weiterentwickelt, um auch andere Prozessschritte bei der Chip-Fertigung zur Sicherung der Schaltungsfunktionalität und Steigerung der Produktivität untersuchen zu können.