Duron 950 bis Athlon XP 1,7+ im Test: AMD Prozessor Roundup

Vorwort

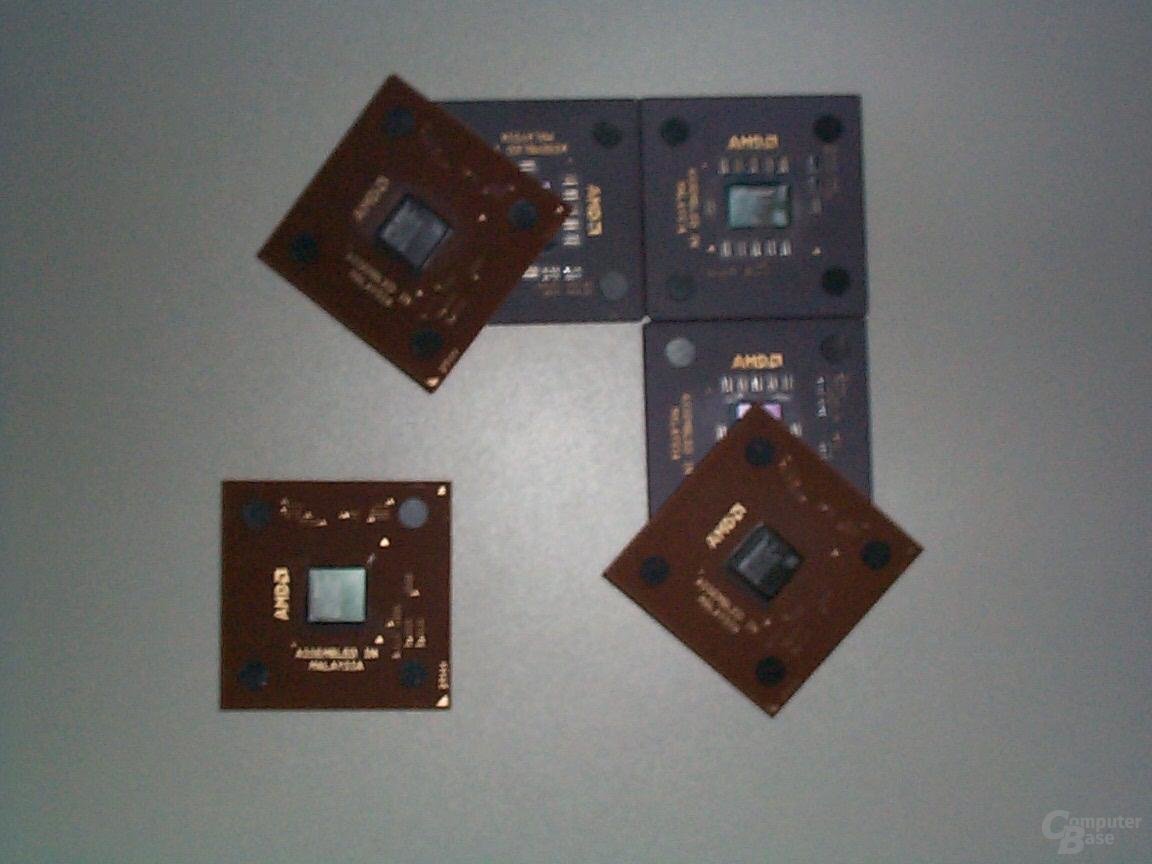

Nachdem wir uns in der Vergangenheit oft mit Mainboards für den von Advanced Micro Devices (AMD) eingeführten Sockel A beschäftigt haben, soll es nun zum ersten Mal um die Prozessoren für diesen Prozessorsockel gehen. Im Gegensatz zu Intel hält AMD seit der Präsentation im Jahre 2000 weiter an diesem System fest. Intel erkor dagegen von 1999 bis in die Gegenwart den Sockel 370, Sockel 423 und letztendlich den Sockel 478. Für Intel ist ein neuer Sockel zumeist mit einer völlig neuen Architektur verbunden gewesen, die mit dem Pentium 4 mit dem älteren Willamette- und dem neuen Northwood-Kern, der bereits in 0,13µm gefertigt wird, vorerst seinen Höhepunkt erreicht hat. Dass es aber nicht unbedingt immer einen neuen Sockel benötigt, um die Leistung des Prozessors deutlich zu erhöhen, zeigte AMD kürzlich mit der Einführung des Athlon XP mit Palomino-Kern sowie des neuen Duron-Prozessors mit Morgan-Core. Wir haben uns einmal die neuesten Prozessoren aus diesem Hause angesehen und möchten zeigen, wo die eventuellen Stärken und Schwächen der Neulinge liegen. Unser Dank geht an dieser Stelle an AMD, die so freundlich waren, uns ein breites Spektrum an Testprozessoren zur Verfügung zu stellen.

Geschichte

Um nicht zu sehr vom eigentlichen Thema dieses Prozessor-Vergleichstest abzulenken, haben wir uns dazu entschiedenen, die Geschichte der AMD Prozessoren, beginnend beim K5, in einem gesonderten und daher auch etwas ausführlicheren Artikel zu veröffentlichen. Wir haben uns bemüht, die Entwicklung und die einzelnen Architekturschritte so genau wie nötig darzustellen. Sicherlich ginge es noch etwas genauer, doch schließlich handelt es sich um Auslaufmodelle, die heute kaum noch eine Rolle spielen. Allerdings gibt es auch einige interessante Parallelen zu beobachten. So kam der K5 ähnlich wie der Athlon XP aus der heutigen Zeit mit einem Performance Rating daher. Das heißt, die Geschwindigkeitsangabe auf dem Prozessor ist nur eine Vergleichsgröße zu einem anderen Prozessor, hat aber selbst nur wenig mit dem realen Takt des Prozessors zu tun. Auf das Performance Rating des Athlon XP sowie dessen technischen Raffinessen und auch die des neuen Duron werden wir unter anderem im nächsten Abschnitt dieses Artikels eingehen.