Athlon 64 FX-51 und Athlon 64 3200+ im Test: Zauber der AMD64-Architektur

26/57Silicon on Insulator - Ein Schritt in die Zukunft (Fortsetzung)

Eines der Probleme der Silicon on Insulator-Technik ist der hohe Preis der Wafer. So kosten diese zu diesem Zeitpunkt noch en Vielfaches der alten und wirken sich somit nicht positiv auf den Preis des daraus resultierendes Prozessors aus. Doch wie werden diese Wafer überhaupt hergestellt? Wir erklären es euch:

Zur Zeit gibt es mehrere Methoden, um einen Wafer der SOI-Technik herzustellen. IBM selbst nutzt laut eigenen Whitepaper-Angaben eine Technik Namens SIMOX, Separation by Implantation of Oxygen. Bei diesem Verfahren wird bei extrem hohen Temperaturen eine Schicht reinster Sauerstoff auf eine Siliziumschicht aufgetragen. Unter diesen hohen Temperaturen verbinden sich Silizium und Sauerstoff zu jenem Oxid der SOI-Technik. Die so erzeugte SOI-Schicht muss dann nur noch auf einen normalen Silizium-Wafer aufgetragen werden. IBM behauptet sogar, dass man durch dieses Verfahren eine gleich hohe Ausbeute hat wie bei den normalen Wafern.

Eine weitere Technik zur Herstellung von SOI-Wafern ist BESOI, Bond and etch-back SOI. Bei dieser Technik werden zwei Wafer genommen und beide mit einer Oxidschicht unter zur Hilfenahme der Van der Waals-Kräfte zusammengefügt. Um eine angemessene Dicke des Wafers zu erzeugen, wird einer der beiden vor oder nach der Zusammenfügung maschinelles Abschleifen und Polieren auf eine Dicke von knapp 0,1µm geschrumpft. Mit diesem Verfahren ließen sich in der Vergangenheit qualitativ hochwertigere, aber auch teurere Wafer herstellen. Mittlerweile ist aber auch die SIMOX-Technik fortgeschritten und erzeugt Wafer mit gleicher Qualität.

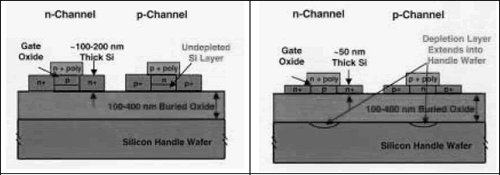

Des Weiteren gibt es zwei verschiedene Modi, in denen Transistoren auf Basis der SOI-Technik hergestellt werden können. AMD nutzt die „half depleted“-Technik für die Produktion der aktuellen Opteron, Athlon 64 und Athlon 64 FX Prozessoren. Ob ein Transistor half oder fully depleted ist bestimmt letztendlich die Dicke der verwendeten Silizium-Schicht. Die Vorteile der Transistoren, deren Silizium-Schicht besonders gering ist (fully depleted), liegen dabei auf der Hand. So weisen diese Transistoren eine geringere Schaltzeit auf und verbrauchen weniger Strom. Ebenfalls wird die minimale Spannung, die für einen Schaltvorgang benötigt wird, herabgesetzt. Intel will ab dem Jahr 2005 voll auf diese Technik setzen, während AMD im Moment im Half-depleted-Modus produziert. Der größte Vorteil dieser Technik ist der geringere Kostenaufwand bei der Produktion. Ebenfalls sind diese Transistoren leichter anzusteuern, da die minimal benötigte Spannung nicht so großen Fluktuationen unterzogen ist wie bei der Fully-depleted-Technik. Der größte Vorteil liegt jedoch darin, dass man größtenteils auf Wafer aufbauen kann, die im kostengünstigen und ebenso effektiven SIMOX-Verfahren hergestellt wurden. Für die Herstellung von Transistoren im Fully-depleted-Verfahren sind hingegen komplizierter aufgebaute Wafer nötig.

Silicon on Insulator gehört die Zukunft. Nicht zuletzt wird die Betagtheit des alten CMOS-Prozesses der neuen SOI-Technik den Weg ebnen, auch die vielen Vorteile dieser Technik dürften für sich sprechen. In den letzten Jahren gab es jedoch immer wieder Probleme mit der Massenproduktion dieser Transistoren, ein Grund für die verspätete Veröffentlichung AMDs neuester Prozessoren auf Basis der AMD64-Architektur. Nun, im Jahre 2003, scheint man dieser Probleme jedoch Herr geworden zu sein und startete bereits mit der Massenproduktion. So laufen schon seit einigen Monaten bei AMD Opteron-Prozessoren auf Wafern aus dem schönen Dresden vom Band und auch IBM produziert seit einiger Zeit Prozessoren auf Basis der SOI-Technik für Apple. Die Tatsache, dass sich auch bald Intel diesem Fertigungsprozess anschließen möchte, zeigt weiterhin das vorhandene Potential, wenn es um höhere Schaltzeiten von Transistoren und den damit verbundenen Mehrleistungen bei Prozessoren geht.