Intel fertigt erste 65nm Speicherzelle

Die Vorstellung des ersten in 90nm gefertigten Intel-Prozessors, "Prescott", musste entgegen des ursprünglichen Zeitplanes von Ende 2003 auf Anfang 2004 verlegt werden. Probleme in der Fertigung sollen die Probleme verursachen. Den Problemen zum Trotz hat Intel jetzt erste Speicherzellen in 65nm gefertigt.

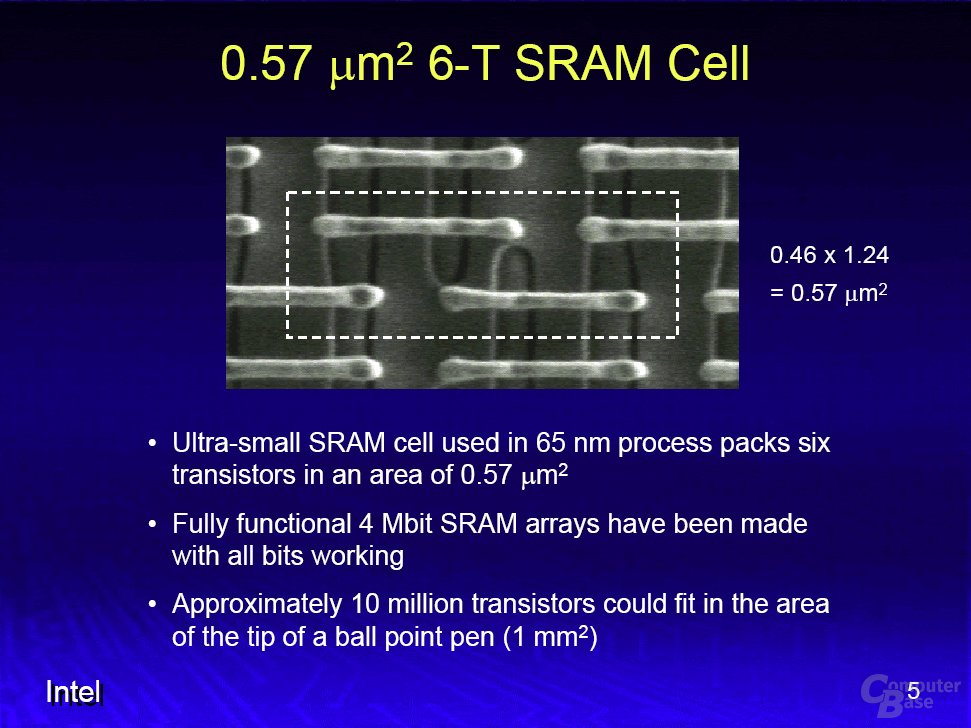

Genauer gesagt wurde ein 4Mbit großes und voll funktionsfähiges SRAM Array bestehend aus in 65nm gefertigten und 0,57 µm² großen SRAM-Zellen in Intels Entwicklungswerk für 65nm und 45nm Logik-Strukturen auf Silizium gebannt. Damit scheint der Grundstein für die übernächste Fertigungsgeneration gelegt zu sein, dessen Massenproduktion 2005 anlaufen soll - vorher müssen sich noch die 90nm Fertigungstechnologie behaupten. Hier könnte man übrigens erstmals im März 2002 die erfolgreiche Produktion einer in diesen Strukturbreiten gefertigten SRAM-Zelle verkünden.

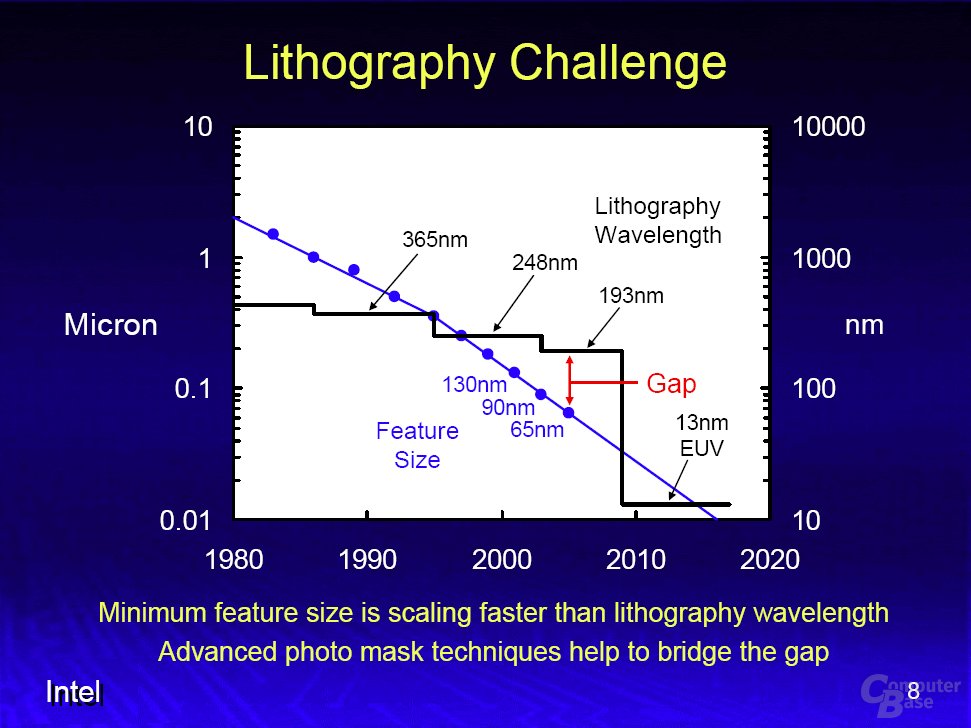

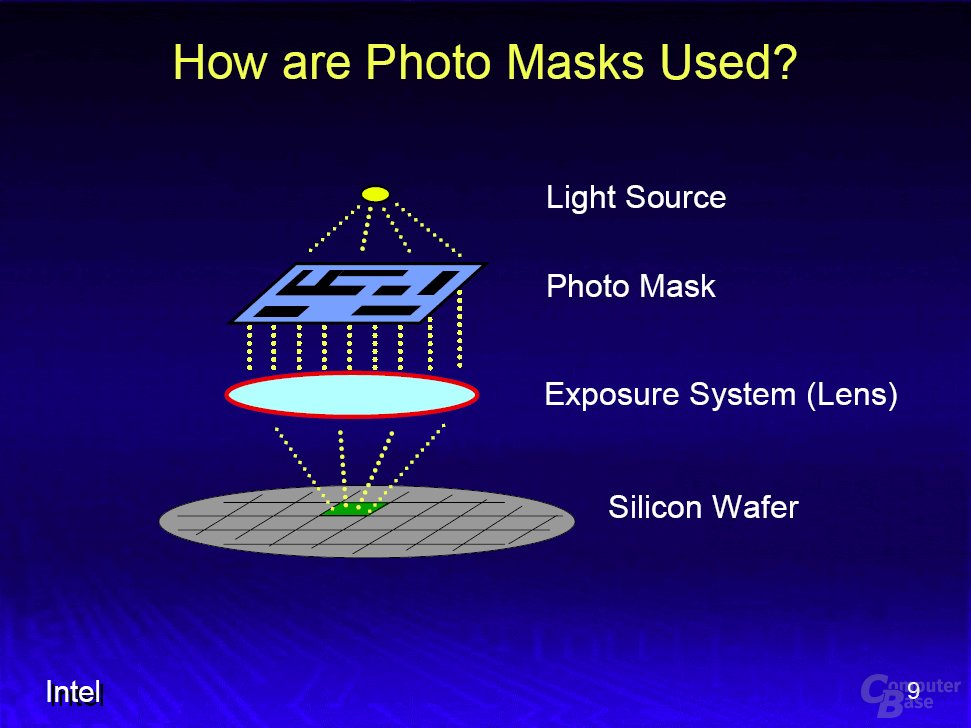

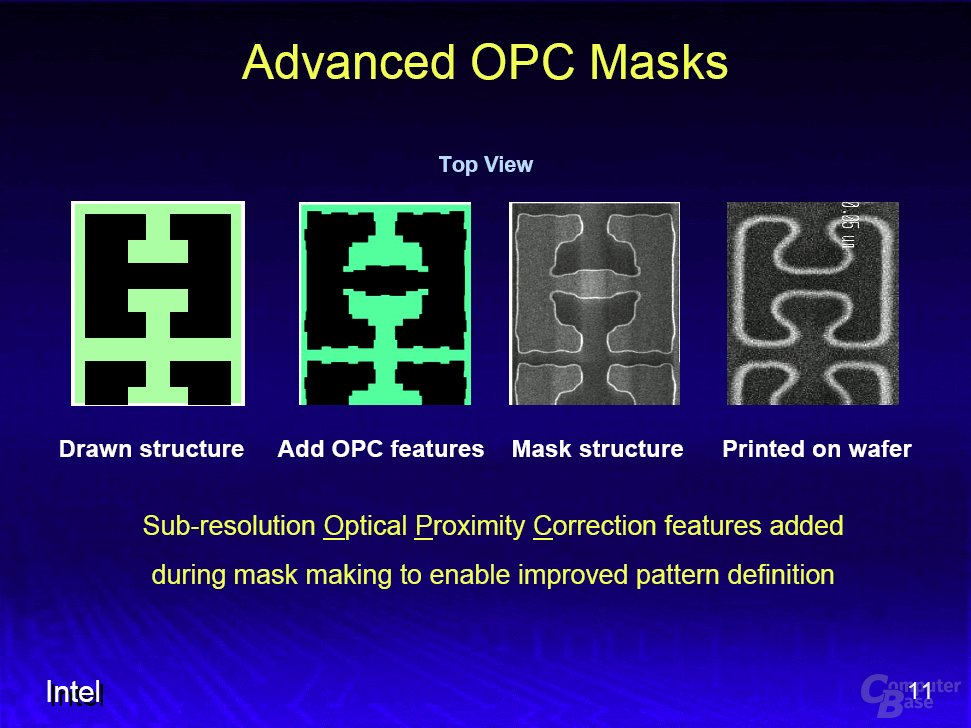

Das knifflige an der Produktion dieser kleinen Strukturen: Das für die Belichtung der Siliziumscheiben (Wafer) genutzte Licht hat eine größere Wellenlänge als die Strukturen die am Ende heraus kommen. So soll bei der 90nm und 65nm Fertigung zwar Licht mit einer Wellenlänge von 193nm zum Einsatz kommen (bei der aktuellen 130nm sind es 248nm), was jedoch im Vergleich zu den geplanten Strukturen nach wie vor zu langwellig ist. Die Strukturen der Photomaske kommen aufgrund physikalischer Grenzen nicht so auf dem Wafer an, wie eigentlich gedacht. Aus diesem Grund muss in der Fertigung etwas getrickst werden: Man nutzt einfach eine Fotomaske bei der optische Störeffekte fest eingeplant sind. Das Ganze nennt sich dann Optical Proximity Correction und hat sich auch schon bei den 130nm Strukturen des aktuellen Pentium 4 bewehrt. Allerdings wird der Abstand zwischen Wellenlänge des Lichts und den gewünschten Strukturbreiten zunehmend größer.

Feldkirchen, den 24. November 2003 - Intel stellt erstmals voll funktionstüchtige SRAM-Bausteine (Static Random Access Memory), basierend auf der kommenden 65 Nanometer Technologie, her. Damit kommt dieser Fertigungsprozess planmäßig ab 2005 auf 300 mm Wafern in der Massenproduktion zum Einsatz

Dieser neue 65 Nanometer Fertigungsprozess ist eine Kombination aus leistungsfähigeren Transistoren mit geringerer Verlustleistung, der zweiten Generation des Strained Silicon, schnellen Interconnects aus Kupfer und einem Low-k Dielektrikum.

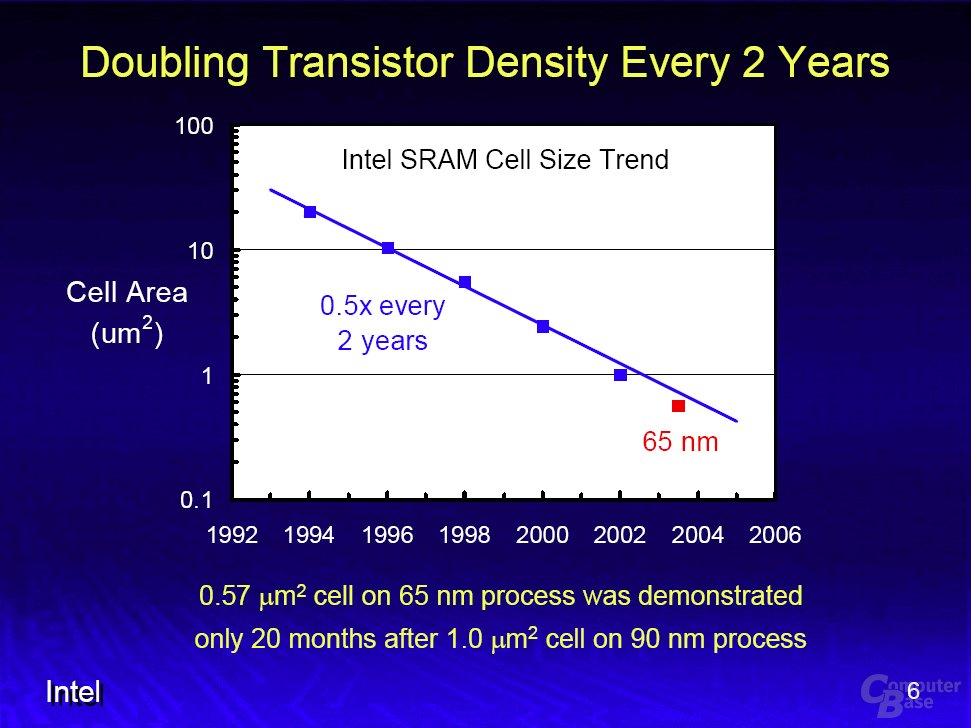

- "Intel setzt mit der 65nm Technologie den seit 15 Jahren bestehenden Trend fort, alle zwei Jahre einen neuen Fertigungsprozess einzuführen. Tatsächlich sind sogar nur 20 Monate vergangen, seit wir die volle Funktionsfähigkeit von SRAMs auf Basis unseres 90nm Prozesses angekündigt haben.", so Dr. Sunlin Chou, Senior Vice President und General Manager der Intel Technology und Manufacturing Group. "Damit verlängern wir nicht nur die Gültigkeit von Moore's Law, sondern können auch noch bessere Produkte produzieren, während wir gleichzeitig die Fertigungskosten senken."

Details zur 65 Nanometer Prozess Technologie

Intels neuer 65 Nanometer Fertigungsprozess zeichnet sich durch Transistoren aus, die nur noch 35 Nanometer lang sind (Gatelänge). In der Massenproduktion werden sie damit die kleinsten Hochleistungstransistoren auf CMOS-Basis sein. Zum Vergleich: Die Transistoren, die derzeit in Pentium 4 Prozessoren zum Einsatz kommen, messen 70 Nanometer, die Transistoren des in 90nm gefertigen Prescott-sogar nur 50 Nanometer. Kleine und schnelle Transistoren sind die Grundelemente für sehr schnelle Prozessoren.Strained Silicon: Intel integriert die zweite Generation seines sehr leistungsfähigen Strained Silicon in den 65 Nanometer Fertigungsprozess. Dank Strained Silicon fließt der Strom effizienter und mit nur 2% höheren Fertigungskosten lassen sich damit schnellere Transistoren bauen.

Interconnects aus Kupfer mit neuem Low-k Dielektrikum: Der Fertigungsprozess integriert acht Schichten eines Low-k Dielektrikums. Dies erhöht die Signalgeschwindigkeiten innerhalb des Prozessors und sorgt gleichzeitig für einen geringeren Stromverbrauch des Chips.

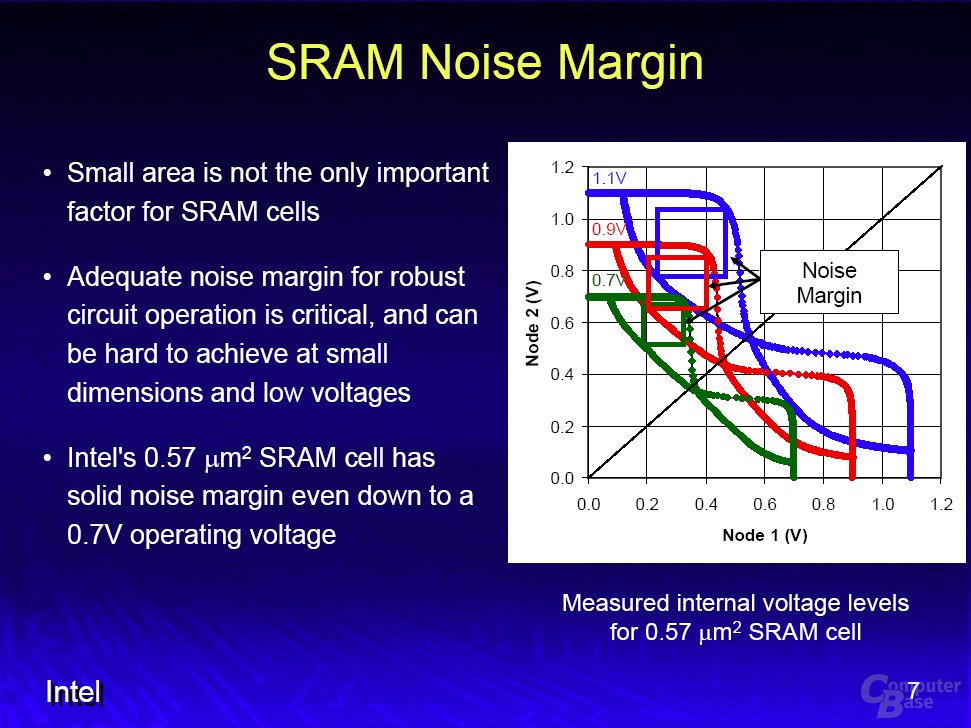

Voll funktionstüchtige, robuste Bausteine Intel produziert bereits voll funktionstüchtige 4 Megabit SRAM Bausteine mit einer winzigen Fläche von 0,57 Quadratmikrometern auf dem 65 Nanometer Fertigungsprozess. Kleine SRAM-Speicherzellen ermöglichen eine Leistungssteigerung durch die Integration größerer Cachespeicher in Prozessoren. Die ersten in 65 Nanometer Technologie gefertigten SRAM-Bausteine erweisen sich als sehr robust mit einem zuverlässigen Rauschabstand, was ein effizientes Umschalten der Transistoren erlaubt. Jede SRAM Zelle besteht aus sechs Transistoren. Zehn Millionen dieser Transistoren würden auf einem Quadratmillimeter Platz finden und somit etwa auf die Spitze eines Kugelschreibers passen.

- "Intels 65 Nanometer Fertigungsprozess ist bereits sehr zuverlässig und auf dieser Basis fertigen wir schon Wafer und Chips in unseren Entwicklungsfabriken," so Mark Bohr, Intel Senior Fellow und Leiter der Abteilung Prozessarchitektur und Integration. "Wir gehen davon aus, dass wir im Jahr 2005 das erste Unternehmen sein werden, das auf Basis der 65 Nanometer Technologie in großen Stückzahlen produzieren wird."

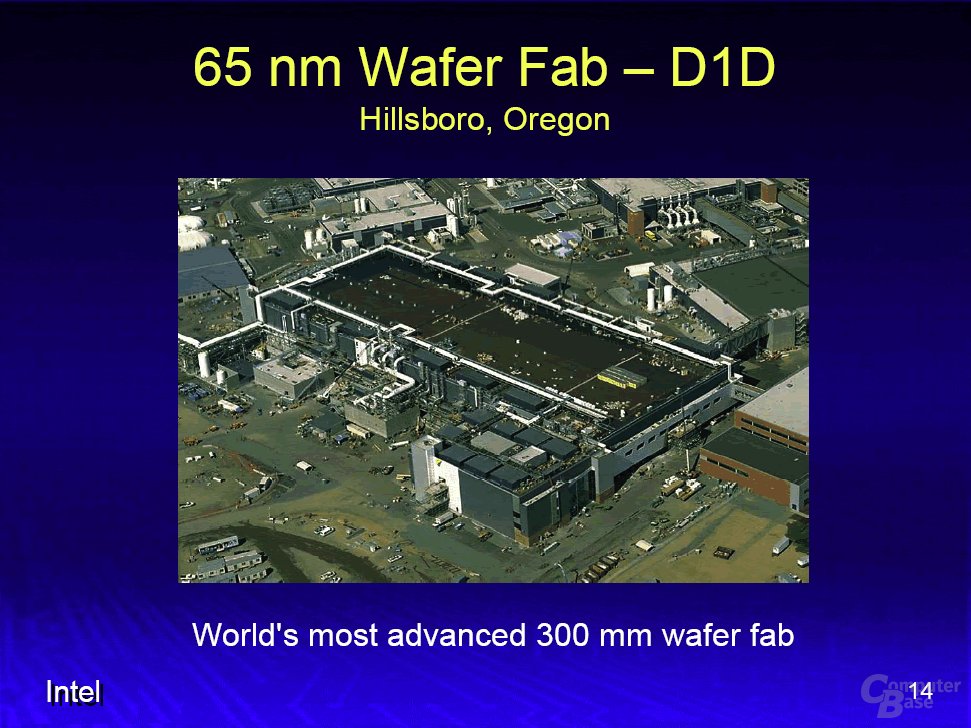

Diese Halbleiterbausteine werden in Intels 300 mm Wafer Entwicklungsfabrik D1D in Hillsboro, Oregon, hergestellt, wo der 65 Nanometer Prozess auch entwickelt worden ist. D1D ist Intels neueste und größte Fabrik. Der größte Reinraum, der dort zu finden ist, misst rund 16.500 Quadratmeter, was ungefähr der Größe von zweieinhalb Fußballfeldern entspricht.

Eigene Masken-Entwicklung verlängert die Lebensdauer von Lithografie-Tools

Intels firmeneigene Gruppe zur Herstellung von Masken trägt wesentlich dazu bei, fortschrittliche Masken zu entwickeln, um so die bestehenden Geräte für die 193 Nanometer Lithografie ebenfalls im 65 Nanometer Fertigungsprozess einsetzen zu können. Intel geht davon aus, einige aktuellere 193nm Lithografie-Tools nachrüsten zu müssen, ansonsten aber die 193nm und 248nm Lithografie-Tools, die derzeit in der 90 Nanometer Fertigung zum Einsatz kommen, weiterhin nutzen zu können. Das reduziert die Implementierungskosten und garantiert zudem ausgereifte Werkzeuge für den Fertigungsstart. Der 65 Nanometer Fertigungsprozess beginnt planmäßig in D1D für die Massenproduktion und wird auf weitere 300 mm Produktionsstätten Anfang 2005 ausgedehnt.