IDF: Dual-Core CPUs mit 24 MB Cache

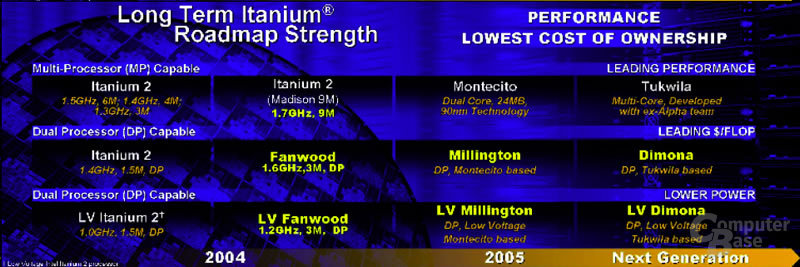

Intel nutzte das IDF und stellte mehrere neue Itanium 2 Prozessoren für Dual-Prozessor-Systeme vor. Für das Jahr 2004 plant das Unternehmen die Auslieferung der neuen Itanium 2 Prozessoren mit 1.4 GHz und 1.6 GHz, ausgestattet jeweils mit drei Megabyte Cache.

Im nächsten Jahr folgt dann der "Millington". Der erste Multi-Core Intel Itanium 2 Prozessor für Dual-Prozessor-Server und -Workstations mit Codenamen "Dimona" wird nach dem Millington folgen.

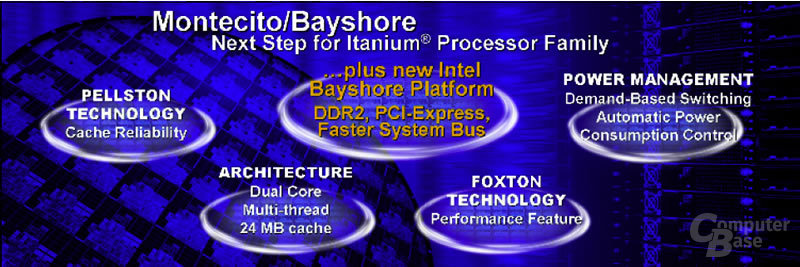

Der erste Dual-Core Itanium 2 Prozessor für Systeme mit vier und mehr Prozessoren mit Codenamen "Montecito" ist für das Jahr 2005 geplant, soll mit 24 MB Cache ausgestattet sein und wird unterstützt durch Intels Chipsatz der dritten Generation - Codename: "Bayshore". Bayshore ermöglicht einen schnelleren Front Side Bus (FSB) und unterstützt PCI Express sowie Double Data-Rate 2 (DDR2) Speicher. Montecito wartet mit zwei neuen Prozessorinnovationen unter den Projektnamen "Pellston" und "Foxton" auf. Sie sollen die Zuverlässigkeit des Caches sowie die Leistung unter hoher Belastung erhöhen. Bei Foxton scheint es sich auf den ersten Blick um eine Multi-Core und Multi-Threading Technologie zu handeln, die im Vergleich zu HyperThreading nicht nur zwei Threads parallel bearbeiten kann.

Intel plant, bis zum Jahr 2007 mehr als die doppelte Leistung mit Itanium 2 Prozessoren gegenüber der Xeon Prozessorfamilie bei gleichen Kosten für die Plattform zu erzielen.

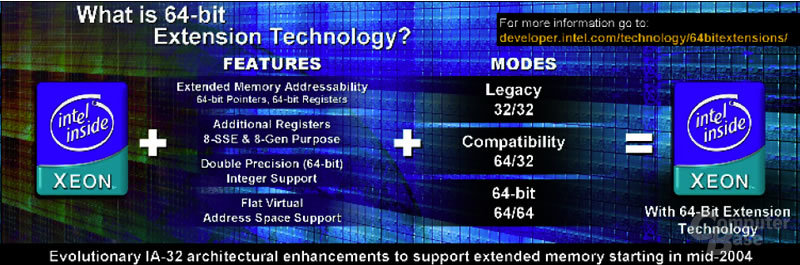

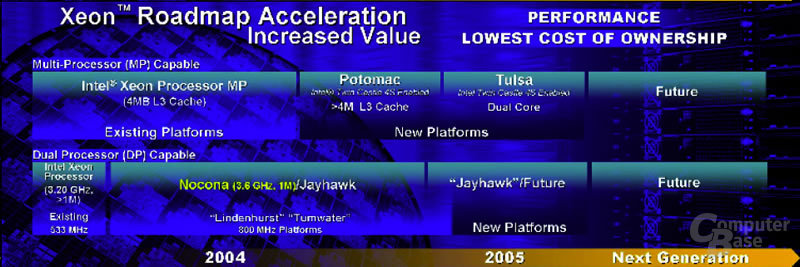

Bis dahin ist jedoch noch ein weiter weg und deshalb wird auch die Xeon-Familie noch mütterlich gepflegt. So stellt Intel auf den IDF einen Xeon 3.2 GHz mit einem größeren zwei MB Cache vor - bisher gab es nur ein 3,2 GHz Modell mit 1 MB Cache. Der Intel Xeon Prozessor der nächsten Generation mit Codenamen "Nocona" ist für die erste Hälfte des Jahres 2004 vorgesehen. Er wird mit 3.6 GHz und einem 800 MHz FSB sowie Unterstützung für DDR2, PCI Express und einer 64-Bit Speichererweiterung Technologie ausgeliefert, die zu AMDs AMD64 Erweiterung kompatibel sein wird. In greifbarer Nähe ist außerdem ein Multiprozessor-tauglicher Xeon MP mit insgesamt 4 MB L3 Cache, der auf den bestehenden FSB400 zu betreiben sein wird. Ende des Jahres wird dieser vom in 90nm gefertigten Potomac abgelöst werden. Tulsa und Jawhawl heißen die Nachfolger der Nachfolger.