DDR2 – Die Grundlagen: Alles wird (irgendwann) schneller!

2/4Technische Gegebenheiten

In der Einleitung schon kurz angerissen und jetzt noch etwas ausführlicher: Rein von der Optik her erkennt ein Laie den Unterschied kaum, ob er ein DDR1- oder DDR2-Module vor sich liegen hat. Eine kleine Auffälligkeit ist mit Sicherheit die Anzahl der Kontakte - 240 bei DDR2 gegenüber 184 bei DDR-Modulen. Und es gibt auch DDR2-Module mit 200 (SO-DIMM), 214 (Micro-DIMM) und 244 (Mini Registered DIMM) Kontakten. Die Speicherchips, die bisher nur in Ausnahmefällen im FBGA-Chips (Fine-Pitch Ball Grid Array) gefertigt wurden (und nicht mehr auf das so genannte TSOP (Thin Small Outline Package) setzten), sind nun fest in den Spezifikationen von DDR2 verankert. Die Speicherchips sehen also von außen erheblich kleiner aus - nur WLSCP besitzt noch kleinere Ausmaße.

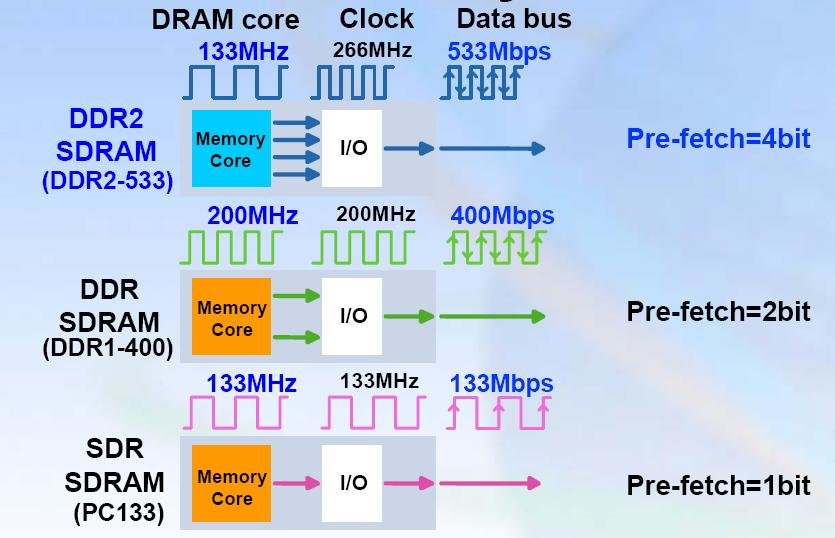

Die Änderungen beim neuen Speicher stecken also im Inneren, im Detail. Um dieses ein wenig verständlich zu machen, müsssen wir allerdings ein wenig ausholen. Beim altbekannten SDR-SDRAM, das SDR steht für Single Data Rate, takten Chip-Kern (er nimmt rund 90% des Speicher-Chips ein), I/O-Buffer (ein im Speicher-Chip integrierten Zwischenspeicher, rund 10% Platzbedarf) und externer Speicherbus mit der gleichen Frequenz. Stellt man sich nun eine sinusförmige Schwingung vor, werden Datenpakete nur bei einer aufsteigenden Kurve übertragen. Zustande kommt somit eine Speicherbandbreite von etwas über 1 GB/s - PC133-SDRAM war geboren (1 Bit * 133 MHz * 64 Bit (Bandbreite) = 1064 MB/s). Die Neuvorstellung von DDR-Speicher änderte im Prinzip nur das Folgende: In der bekannten Sinusschwingung werden nun sowohl in der steigenden als auch in der fallenden Kurve Daten übertragen - sprich „Double Data Rate“. Bei gleichen Ausgangsbedingungen werden Pro Takt nun 2 statt bisher 1 Bit übertragen (2 Bit * 133 MHz * 64 Bit (Bandbreite) = 2128 MB/s). Damit stieg die effektive Datenfrequenz am Speicherbus von 133 auf 266 MHz und lieferte so eine ungefähre Bandbreite von 2,1 GB/s - PC2100 als Standard war geboren.

Die nächste Evolutionsstufe kommt nun mit DDR2. Intern bleibt aber nach wie vor alles beim Alten: 133 MHz (und damit ein ganzes Stück hinter den Taktraten von DDR400 zurück). Beim DDR2-Speicher taktet der I/O-Buffer mit der zweifachen Frequenz des Chip-Kerns. Damit der Puffer-Speicher im Idealfall auch doppelt so viele Daten erhält, wird die Schnittstelle zwischen Chip-Kern und dem I/O-Buffer auf vier Leitungen, dem sogenannten „Prefetch of 4“, verbreitert. Beim DDR-Speicher war diese doppelt, beim SDRAM einfach angebunden. Danach folgt im Prinzip das gleiche Spiel wie beim DDR-Speicher: Weil der I/O-Buffer schon mit doppeltem Takt arbeitet und dieser durch Double Data Rate nochmals verdoppelt wird, bietet man letztendlich eine Bandbreite von rund 4,3 GB/s, was genau dem offiziellen Standard für die PC4300/DDR2-533-Module entspricht. Alles in Allem hat man nun eine vier Mal so hohe maximale Datenübertragungsrate wie ein damaliges SDR-SDRAM-Modul nach dem PC133-Standard, obwohl der Chip auch weiterhin mit 133 MHz läuft.

Auf gut Deutsch und die Theorie ein wenig vereinfachend: Um die gleiche maximale Übertragunsrate wie bisheriger DDR-Arbeitsspeicher zu erreichen, kann DDR2 intern mit der halben Frequenz betrieben werden. Der Vorteil wird dann auch recht schnell offensichtlich. Wegen des geringeren Taktes wird das Modul intern nicht so stark belastet, wodurch die verbauten Chips mit nur noch 1,8 Volt auskommen, was natürlich eine deutlich geringere Wärmentwicklung zur Folge hat. Da man intern beim neuen DDR2-Speicher aber im Vergleich zu DDR-RAM doppelt so breit anbindet, bleibt die theoretische Maximalbandbreite gleich. Die Timings sind beim neuen Speicher im Vergleich zum bisherigen allerdings (noch) als deutlich schlechter anzusehen und fressen so, durch den höheren Verschnitt bedingt, einen Teil des potentiellen Geschwindigkeitsgewinnes direkt wieder auf.

Timings und Terminierung

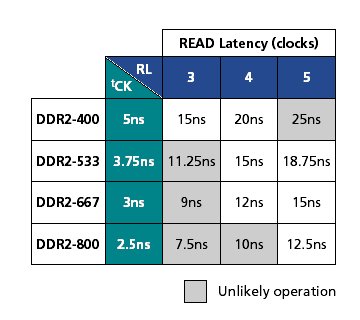

Denn neben der reinen Taktfrequenz des Speicher-Kerns ist die tatsächlich erreichte Bandbreite auch von der Latenzzeit abhängig. Die Latenz gibt dabei die Zahl der Takte an, die benötigt werden, um die Daten bereitzustellen. Da die Wahrscheinlichkeit, dass der I/O-Buffer von DDR2-Modulen bei Zugriffen immer über alle vier Pipelines versorgt wird, niedriger ist als bei DDR-RAM mit zwei Pipelines, sinkt die Effizienz von DDR2 etwas. Kombiniert mit den augenscheinlich relativ schlechten Timings, in Bezug auf auf aktuelle DDR400-Module, und die theoretisch gleiche Speicherbandbreite, werden DDR2-Speicherriegeln anfangs wohl um die 5-10 Prozent langsamer sein als ein vergleichbares Produkt auf Basis von DDR-SDRAM. Die Hersteller haben mittlerweile aber angefangen, neben Modulen mit Timings von 4-4-4 auch Module mit 3-3-3 anzubieten. Diese gibt es aber erst für DDR2-400, bei DDR2-533 sind solche Riegel noch Fehlanzeige.

Ein Dokument von Micron gibt sehr gute Aufschlüsse über die Situation mit den Timings, würde in dieser ausladenden Form aber den Rahmen des Artikels sprengen. Soviel sei gesagt: Typische Latenzzeiten liegen zwischen 12 und 20 ns. Durch diese Gegebenheiten sind derzeit keine anderen Timings als 3, 4 oder 5 möglich (siehe Bild). Wer jetzt dennoch mehr Interesse an den Timings, Latenzzeiten und mehr bekommen hat, der sollte einmal bei Lost Circuits vorbeischauen. Dort hat Michael Schuette, Sr. Application Engineer bei OCZ, den wohl umfangreichsten, aber auch hochtechnischen Artikel zu diesem Thema verfasst. Eines bleibt auch durch den kleinen Abriß - was die Timings anbelangt - am Ende zu vermerken: Der vermeintliche Nachteil der hohen Latenzen und augenscheinlich schlechten Timings wird sich mit steigenden Frequenzen in Luft auflösen. Und genau dafür ist DDR2 entwickelt worden.

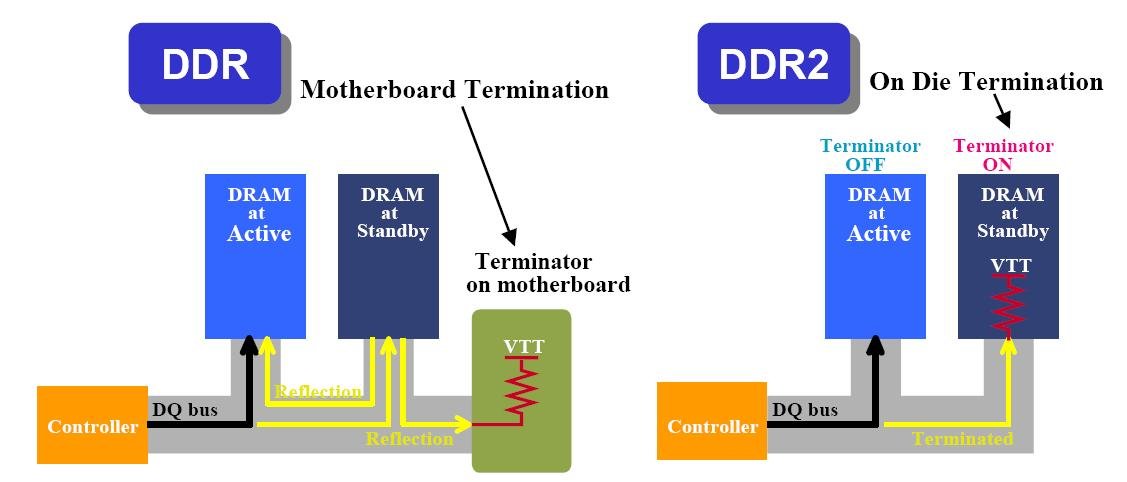

Ein Wort noch zum neuen Feature der Bus-Terminierung. DDR2-Speicher verfolgt einen neuen Weg, um Interferenzen zu vermeiden, welche zwangsweise die Transferraten des Moduls senken. Auf einem DDR2-Chip sitzen die Widerstände für die Terminierung direkt auf dem Speichermodul, die sogenannte „On-Die Termination“. Der Speicher-Controller sendet nun ein Signal auf den Bus aus, das alle inaktiven DDR2-Chips dazu veranlasst, auf Terminierung umzuschalten. Somit befindet sich nur das aktive Signal auf der Datenleitung, Interferenzen sind so gut wie ausgeschlossen. Bisher, also bei DDR-Speicher, liegt am Ende des Busses auf dem Mainboard ein geerdeter Widerstand, der die Störsignale an den I/O-Schnittstellen des Speichers abfängt. Hierbei entstehen auf dem Speichermodul aber Interferenzen, da jedes Signal auf seinem Datenbus von benachbarten Komponenten reflektiert wird. Je mehr Speicher nun also installiert ist, desto größer ist die Wahrscheinlichkeit einer Reflexion. Die neue Variante sorgt also dafür, dass ein aktives Signal störungsfrei übertragen wird, was folgerichtig zu einer unkomplizierteren Entwicklung und Herstellung von DDR2-Modulen führt.

Zusammengefasst noch einmal die wesentlichen Merkmale und Vorteile von DDR2 SDRAM:

- Herstellungsprozeß in 100 bis 130 nm

- FBGA-Chips (Fine-Pitch Ball Grid Array)

- daraus folgt: rund 50% kleinere Chips (126 mm² zu bisher 261 mm²)

- On Die Termination

- Modulgrößen von 128 MB bis 4 GB

- Vier Varianten: 200, 214, 240 und 244 Pins

- Höhere Geschwindigkeiten (400-800 MHz)

- Höhere Bandbreite (sh. Tabelle=)

- CAS Latency von 3, 4, 5

- geringe Spannung (1,8 Volt)

- deutlich geringerer Leistungsbedarf (247 mW zu bisher 527 mW)

| Chip-Klassifizierung | Modul-Klassifizierung | Frontside Bus | Speichergeschwindigkeit | Bandbreite pro Modul | Bandbreite Dual-Channel |

|---|---|---|---|---|---|

| DDR2-400 | PC2-3200 | 200 MHz | 400 MHz | 3,2 GB/s | 6,4 GB/s |

| DDR2-533 | PC2-4300 | 266 MHz | 533 MHz | 4,3 GB/s | 8,6 GB/s |

| DDR2-667 | PC2-5300 | 333 MHz | 667 MHz | 5,3 GB/s | 10,6 GB/s |

| DDR2-800 | PC2-6400 | 400 MHz | 800 MHz | 6,4 GB/s | 12,8 GB/s |