Die Grundlagen von PCI Express: Der ICE für die Peripherie?

2/3Der Bus

Der Bus (physikalischer Layer) ist in seiner maximalen Leitungslänge begrenzt. Bei PCI E x16 darf die Kupferleitung zwischen Sender und Empfänger maximal eine Länge von 50,8 cm aufweisen. Wählt man eine längere Leitung, kann es zu unterschiedlichen Signallaufzeiten zwischen den einzelnen Lanes kommen, was bei der Synchronisation fatale Folgen hätte, da der Empfänger nicht mehr gleichzeitig die Daten und Taktinformationen erhalten kann und demzufolge Datenmüll entsteht. Die Leitungen selbst müssen mit einem 100 Ohm starken Terminationswiderstand bestückt sein und die Differenzspannung zwischen zwei Signalleitungen darf maximal 1,2 Volt betragen. Zudem dürfen die Transmitterspannung von 0,8 Volt und die ankommende Spannung am Receiver von 0,175 Volt nicht unterschritten werden.

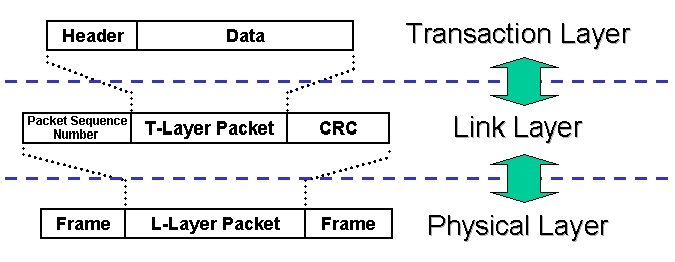

Das Transaction Layer verarbeitet in seiner Hauptaufgabe sämtliche Lese- und Schreibvorgänge sowie bestimmte Ereignisprozeduren und bildet die Verbindung zwischen dem physikalischen und dem Data Link Layer. Der Sinn dabei liegt in der Einsparung von unnötigen und mehrfachen Übertragungsvorgänge, indem über das Credit-Base-System zuerst geprüft wird, ob beim Empfänger genügend freie Puffer vorhanden sind. Bei Anforderung einer Empfangsbestätigung schaltet der Layer automatisch in den Split-Transfer-Mode, wo bis zum Erhalt der Bestätigung zusätzliche Übertragungen zu anderen Adressaten möglich sind. Bestehend aus einem Header und einem Datenstrang kann bei Bedarf auch eine 32 Bit lange Prüfsumme nachgesendet werden. Nach dem Transaction-Layer-Verfahren erhofft man sich eine effiziente Bandbreitennutzung, welche zudem in der Lage ist, über einen internen Switch die einzelnen Daten nach Traffic-Klassen zu sortieren. Dazu dienen im Transaction-Header die Bits 4 - 6 im ersten Byte, welche insgesamt acht verschiedene Service-Klassen kodieren können. Der Header selbst kann bis zu vier Doppelwörter (4 Bytes / 32 Bit) lang sein, wobei die Bits fünf und sechs des ersten Bytes (Byte 0) die länge des Headers angeben. Die Bits 0 bis 4 dienen zur Angabe des Transfermodi, z.B. 32/64 Bit I/O- oder Memory-Schreibvorgänge (Writes). Bit Nummer sieben legt fest, ob dem Header noch ein optionaler Anhang von einem Doppelwort folgt oder nicht. Der Anhang enthält einen CRC-Summe für die Fehlererkennung und kann somit für sehr hohe Datenintegrität sorgen. Über das 6. Bit im zweiten Byte kann dann ggf. eine Rückmeldung gegeben werden, bei einem Fehler die Daten erneut zu senden.

Anschließend übernimmt der Data-Link-Layer die Aufgabe, Daten vom Transaction-Layer für den physikalischen Layer aufzubereiten. Der Link erfolgt über eine Punkt-zu-Punkt-Verbindung zwischen den einzelnen Komponenten. Am Anfang der Datenpakete für den Transaction-Layer wird eine Identifikationsnummer oder auch Paketidentifikationummer zugfügt. Wird bei der Übertragung ein Fehler gemeldet, werden die Daten anschließend umgehend ein weiteres Mal versendet.

Unabhängig von allen Kontrollleitungen bietet der PCI Express-Bus optional die Möglichkeit eines integrierten SM-Bus', welcher in der Lage ist, System- und Power-Management-Aufgaben eigenständig zu steuern. Nebenher überträgt er auch Herstellerinformationen wie Gerätetyp und Seriennummern sowie bei Bedarf Suspend-Zustände und Protokolle von Gerätefehlern. Nicht zu vergessen ist die maximale Leistungsübertragung der Stromversorgung, die von 25 Watt bei AGP 8x um das dreifache auf 75 Watt erhöht wurde.