Intel: Große Fortschritte bei 65 nm

Mit feineren Strukturen wird alles besser? Noch im November letzten Jahres konnte Intel erste Erfolge bei der Fertigung in 65 nm feinen Strukturen verkünden. Man hatte einen voll funktionsfähigen 4 Mbit großen SRAM-Speicher gefertigt, bei dem jede 1-bit-Speicherzelle - bestehend aus sechs Transistoren - auf einer Fläche von 0,57 µm² Platz findet.

Bei 90-nm-Strukturen war hierfür noch ein µm² nötig; was im Vergleich zu den bis dato verfügbaren 130-nm-Halbleitern bereits einen deutlich gesenkten Raumbedarf bedeutete und somit mehr Transistoren auf einem Chip ermöglichte. So waren auch die 125 Mio. Transistoren des Intel Pentium 4 mit „Prescott“-Kern auf einer kleineren Fläche (112 mm² vs. 131 mm²) unterzubringen als die 55 Mio. des in 130 nm gefertigten „Northwood“-Pentium 4. Statt einer aufgrund der feineren Strukturen gesenkten Betriebsspannung und dadurch geringeren Verlustleistung hatte und hat der 90-nm-Pentium 4 jedoch mit hohen Verlustleistungen und hohen Temperaturen zu kämpfen - alles andere als eine gute Werbung für die Fertigung in 90 nm.

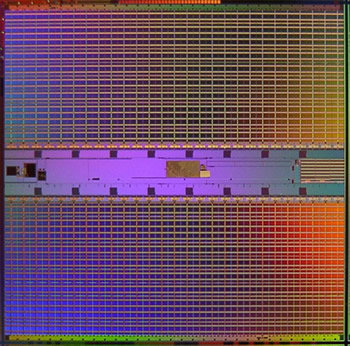

Entsprechend skeptisch schauen wir auf die Fertigung der nächsten Generation. Am heutigen Tage hat Intel nun weitere, vielversprechende Informationen zum P1264 getauften 65-nm-Prozess bekannt gegeben. Freute man sich im letzten Jahr noch über einen 4-Mbit-Chip, sind es nun intakte 70 Mbit, die mit über 500 Millionen Transistoren realisiert werden. Auf der Spitze eines Kugelschreibers ließen sich in etwa 10 Millionen Transistoren unterbringen.

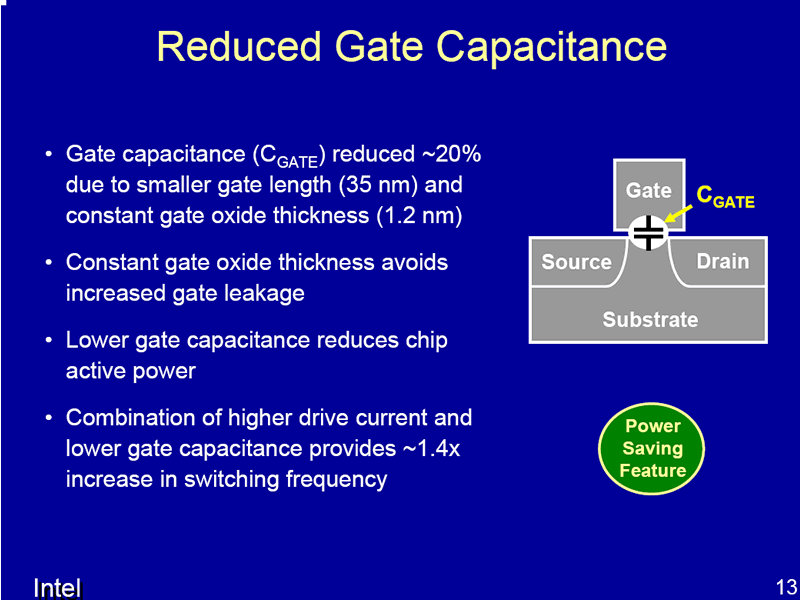

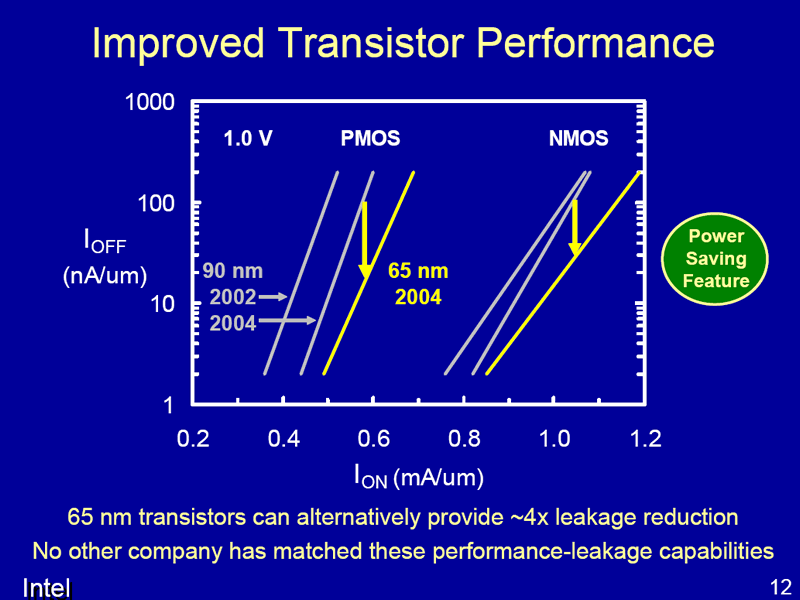

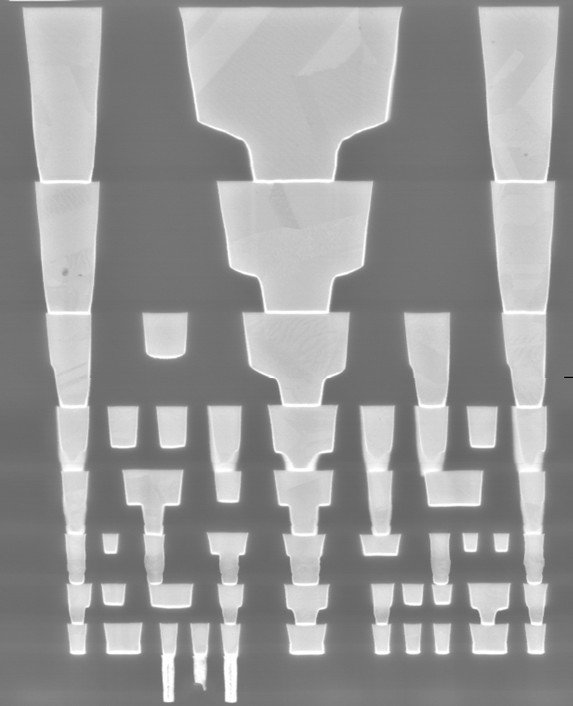

Wie stellt sich P1264 nun im Detail - soweit bekannt - dar? Kurz zusammengefasst, könnte es Intel damit gelingen, den Stromverbrauch seiner aktuellen Prozessoren - glaubt man den uns vorliegenden Materialien - deutlich zu senken und die Taktraten weiter anzuheben. Auch zum Herstellen von 65-nm-Strukturen setzt Intel wie angekündigt auf Lichtquellen mit einer Wellenlänge von 193 nm. Das Licht ist also „länger“ als die zu erstellenden Strukturen; dementsprechend muss sich Intel entsprechenden Tricks wie Optical Proximity Correction (OPC) oder alternating Phase Shift Masks (altPSM) bedienen. Die Breite der Transistor-Gates wurde von derzeitigen 50 nm (90-nm-Fertigung) auf nunmehr 35 nm verringert; die Dicke der Isolierschicht zwischen Gate und Source/Drain blieb dagegen mit 1,2 nm unverändert. Dadurch sollen sich die ungewünschten Kondensator-Effekte um 20 Prozent reduzieren. Sie haben linearen Einfluss auf den Stromverbrauch (Leistungsaufnahme = Kapazität aller Gates x Taktfrequenz x Betriebsspannung²) des Prozessors. Eine Taktsteigerung von 40 Prozent soll so möglich werden. Auch beim gestreckten Silizium (Strained Silicon) hat Intel weitere Verbesserungen vorgenommen. Bei konstanter Leakage, also konstantem Strom bei nicht leitenden Transistor, lässt sich der mögliche Source-Drain-Strom (Ion) um 10 bis 15 Prozent steigern. Soll dagegen der gleiche Source-Drain-Strom durchgeleitet werden, ist dies ganz und gar durch ein Viertel der bisherigen Leakage zu erreichen. Vielversprechende Zahlen wie wir meinen. Um der durch 65 nm höheren Transistordichte Herr zu werden und die Transistoren untereinander verbinden zu können, hat Intel die Anzahl der Verdrahtungsebenen von sieben (90 nm) auf nunmehr acht erhöht. Das Isolationsmaterial (Low-k carbon doped oxide dielectric) zwischen den Schichten wurde ebenfalls verbessert und soll zu einem stromsparenden Prozessor beitragen.

Sollte Intel etwa alle Probleme der 90-nm-Fertigungstechnologie mit der nächsten Fertigungsstufe aus der Welt geschafft haben? Über die zu erwartende Verlustleistung kommender Prozessoren möchten wir an dieser Stelle nicht spekulieren, da es einen 1:1 auf 65 nm umgesetzten Pentium 4 „Prescott“ ohne neue Features sicher nicht geben wird. Um Missverständnissen vorzubeugen, sollte man sich jedoch nicht auf einen um 75 Prozent niedrigeren Verbrauchen freuen, da Leakage nicht alles ist und die Transistoren den Strom häufig zu anderen Transistoren durchschalten müssen. Auf mindestens 20 Prozent könnte man sich jedoch freuen, wenn das derzeitige 90-nm-Silizium auf 65 nm umgesetzt werden würde.

Zu guter Letzt hat Intel bei den auf 300-mm-Wafern hergestellten 70-Mbit-SRAM-Chips so genannte „Sleep Transistors“ verbaut, wodurch große Teile der Speicherzelle, die z.B. beim Prozessorcache zum Einsatz kommen, bei Nichtbenutzung ohne zeitliche Verzögerung aktiviert und deaktiviert werden. Der Stromverbrauch der nicht genutzten Speicherzellen soll sich dabei mehr als dritteln.

Intel möchte noch im kommenden Jahr auf 65-nm-Strukturen umstellen; wann genau, wurde derzeit noch nicht bekannt gegeben. Allerdings sollte man sich wohl eher auf ein Erscheinen Ende des kommenden Jahres einstellen. Derzeitiges 65-nm-Versuchssilizium wurde im D1D in Hillsboro, Oregon, gefertigt. Dort werden auch die ersten 65-nm-Prozessoren vom Band laufen. Im Jahre 2006 werden, wie bereits berichtet, Fab 12 in Arizona und Fab 24(-2) in Irland folgen.