Transmeta: Lizenzabkommen und Roadmap

Nachdem Ende März dieses Jahres bereits NEC im Rahmen einer Allianz auf diverse Technologien zurückgreifen und diese auch in eigenen Halbleiterprodukten mit 90, 65 und 45 nm Strukturbreite einsetzten darf, konnte sich nun auch Fujitsu für die „LongRun2“-Technologie der kleinen Prozessorschmeide begeistern.

Die LongRun2-Technologien von Transmeta adressieren die wachsenden Probleme in der Halbleiterindustrie in Bezug auf eine übermäßige Chip-Erwärmung und den Leckstrom bei Transistoren. Sie sind eine Sammlung von Techniken, die den Betrieb von Halbleiter-Komponenten durch unter anderem Verringerung der Chip-Gesamtleistung, der Standby-Leistung und Burn-in-Leistung optimieren sollen. Die LongRun2-Technologien basieren auf der ersten Generation der LongRun Power Management-Technologie von Transmeta, die die Möglichkeit bot, Prozessortaktung und -Spannung zur Senkung des Energieverbrauchs hundermal pro Sekunde dynamisch anzupassen. Der Workload - also die zu verrichtende Arbeit - entscheidet dabei, wie schnell der Prozessor taktet. LongRun2 erweitert diesen Ansatz um die dynamische Anpassung der Verlustleistung und Schwellenspannung der Transistoren; soll also die Leckströme aktiv reduzieren. Im Standby-Betrieb ist von 2 mW gegenüber 144 mW die Rede.

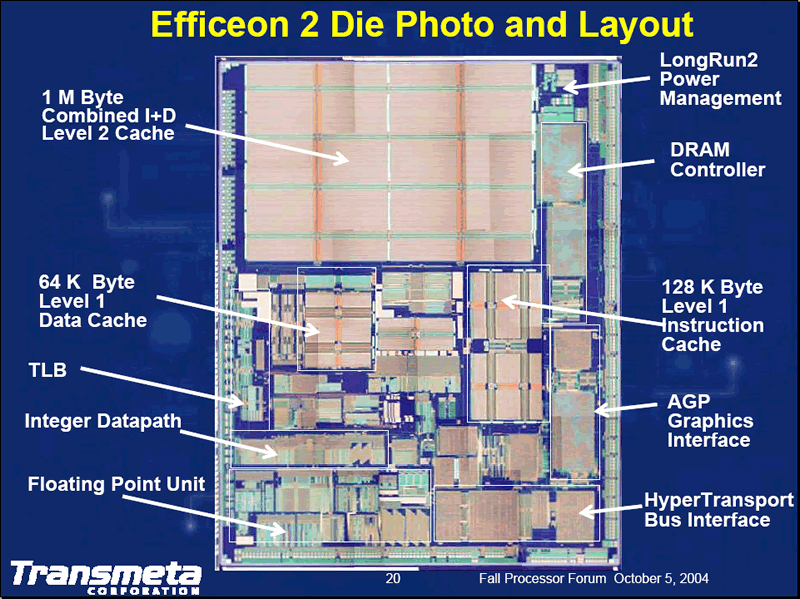

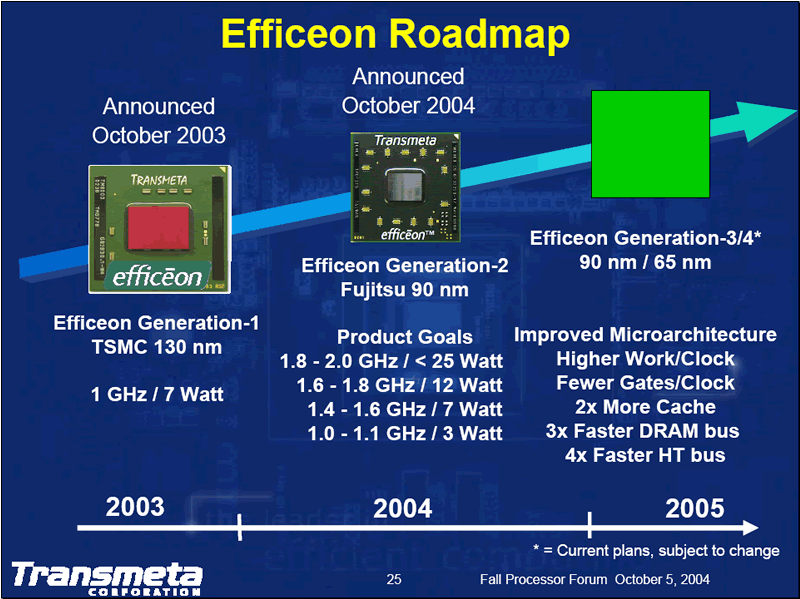

Im Rahmen einer Lizenzvereinbahrung darf Fujitsu nun LongRun2 bei seinen aktuellen und zukünftigen Produkten einsetzen. Transmeta selbst hat LongRun 2 erstmalig mit seiner Efficeon-Produktfamilie im Oktober letzten Jahres vorgestellt. Bei allen bisher ausgelieferten Efficeons ist diese Technik - da noch nicht ausreichend validiert - jedoch hardwareseitig deaktiviert, so dass hier also nur LongRun der ersten Generation zur Verfügung steht. Auch der in 90 nm gefertigte Efficeon der zweiten Generation, der TM8800, der im Oktober dieses Jahrs vorgestellt wurde, muss noch darauf verzichten. Dies trifft im Fall des 90 nm-Produkts übrigens auch auf die angekündigte SSE3-Erweiterung zu, die erst mit einer neuen Revision des TM8800 zur Verfügung stehen wird. Um die neue Revision dann die beiden lange angekündigten Features beinhalten wird, ist zwar unklar, aber nicht unwahrscheinlich. So gab Transmeta bekannt, dass die ersten TM8800 mit LongRun2-Support noch in diesem Jahr bemustert werden sollen.

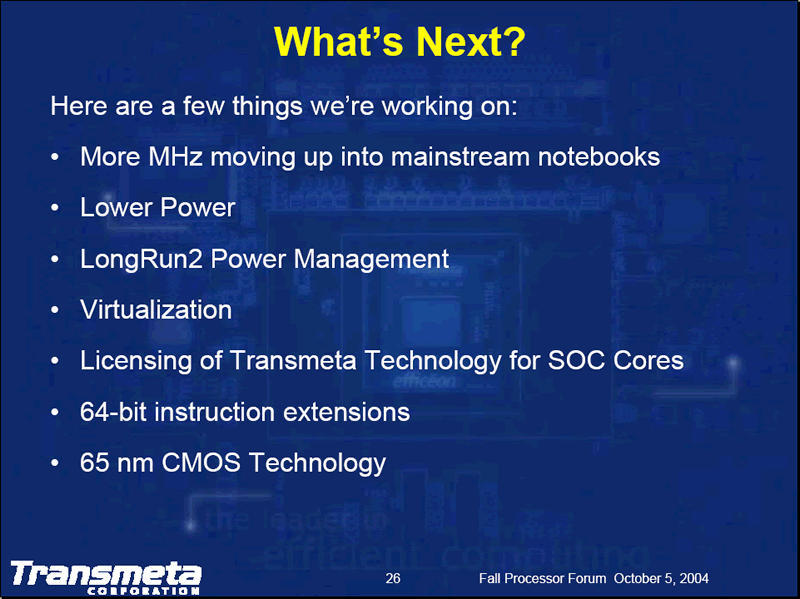

Für die Zukunft hat Transmeta, übrigens bereits Anfang Oktober, erste Zielsetzungen für die Entwicklung des Efficeon der dritten Generation genannt. Dieses soll mit einem 2 MB großen Cache, einem dreimal schnelleren Speicherbus (etwa Support für Dual Channel DDR2-533?) und einem viermal schnelleren HyperTransport-Bus. Letzteres dürfte erreicht werden, indem der aktuell 400 MHz schnelle und 8 bit breite Bus auf 800 MHz und 16 bit aufgebort wird, wodurch die theoretische Bandbreite von 1,6 GB/s auf 6,4 GB/s steigt und damit auf einem Level mit dem Athlon 64 im Sockel 754 liegt. Darüber hinaus sollen neben Verbesserungen an der Mikroarchitektur auch die Pro-Takt-Leistung gesteigert und die Anzahl der pro Takt schaltenden Transistoren gesenkt werden. Bekannterweise kann im Rahmen von CMOS, bestehend aus p-Kanal-(PMOS)- und n-Kanal-(NMOS)-Feldeffekttransistoren, idealerweise nur bei einem Schaltvorgang ein Strom fließen. Desto weniger Transistoren aktiv sind, desto geringer ist somit auch der Stromverbrauch der ganzen CPU. In der Realitiät hat man leider noch mit parasitäten Leckströmen zu kämpfen, die derzeit insbesondere dem Pentium 4 mit „Prescott“-Kern zu schaffen machen. Allerdings versprüht der größte Halbleiterhersteller der Welt für seinen 65 nm-Prozess schon jetzt Euphorie, die Leakage um den Faktor vier gesenkt zu haben.

Übrigens sind bei Transmeta auch eine 64 bit-Erweiterung und Virtualisierungstechnologien wie Intels Vanderpool oder AMDs Pacifica, welche den (gleichzeitigen) Betrieb mehrerer Betriebssysteme ermöglicht, ebenfalls in der Planungsphase.