IDF: Intel nennt Details zur neuen Architektur

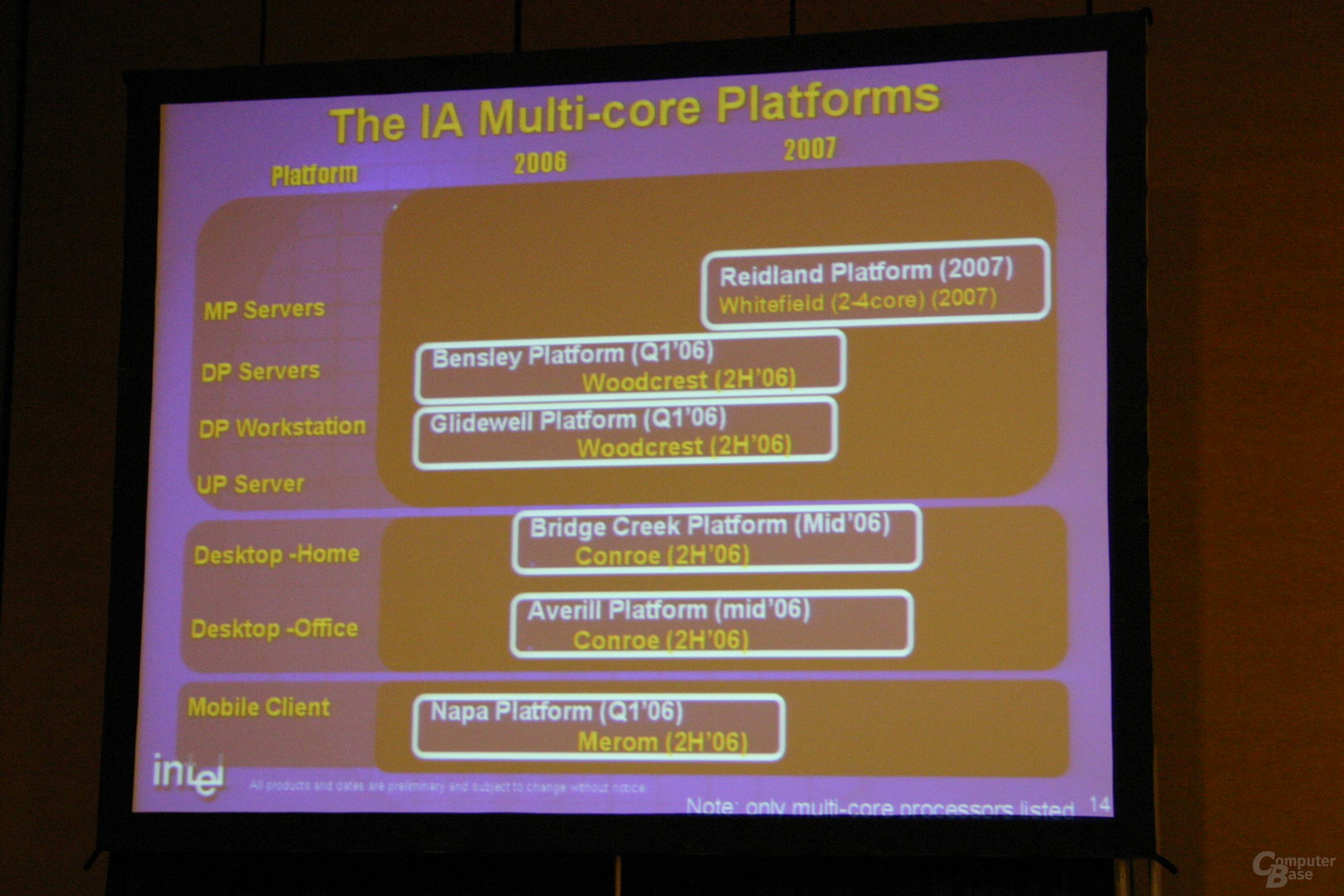

Im Rahmen des Intel Developer Forum Fall 2005 hat Intel wie erwartet erste Details zu seiner neuer Mikroarchitektur bekannt gegeben, die im zweiten Halbjahr 2006 in den ersten Produkten im Mobile-, Desktop- und Server-Bereich zum Einsatz kommen wird.

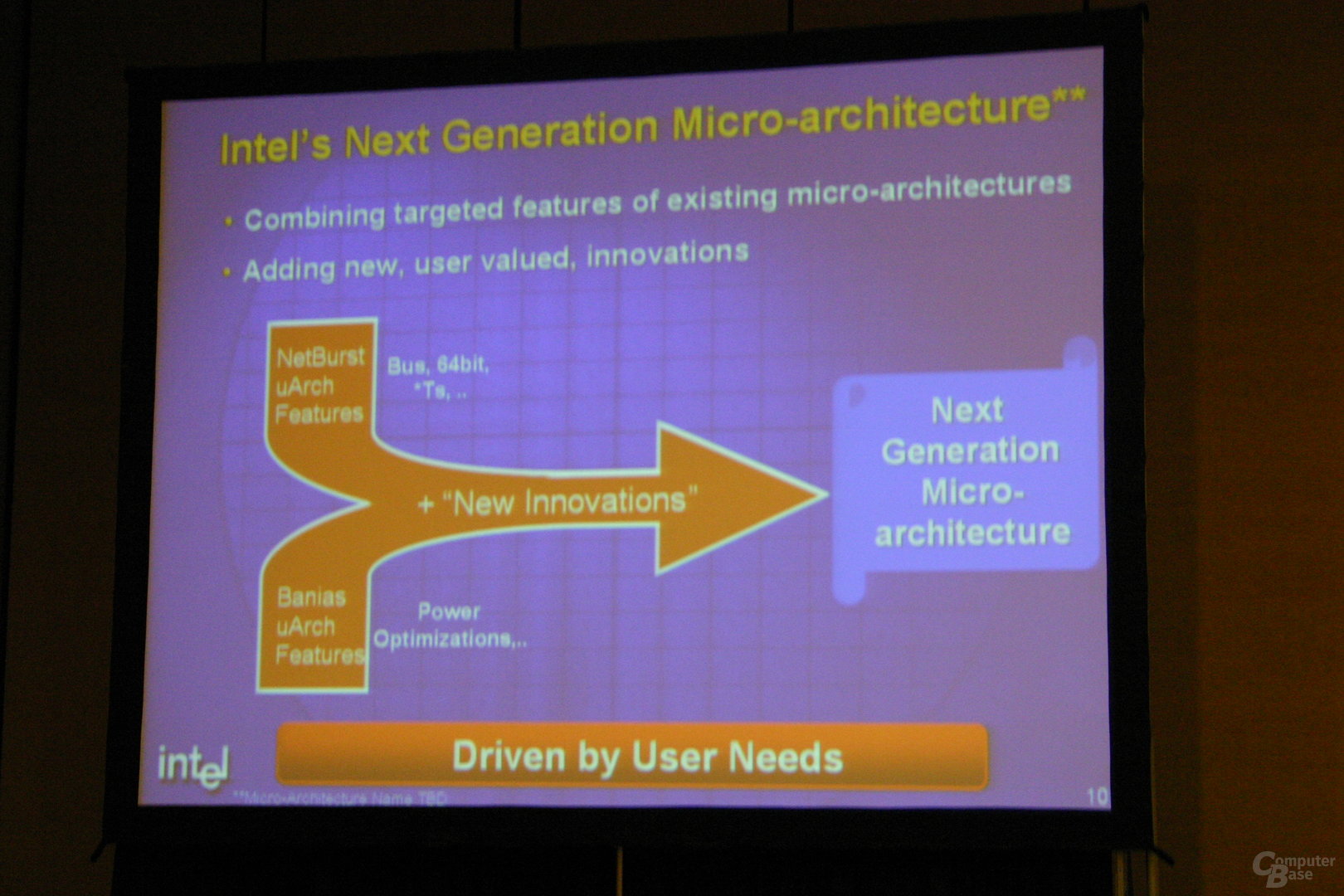

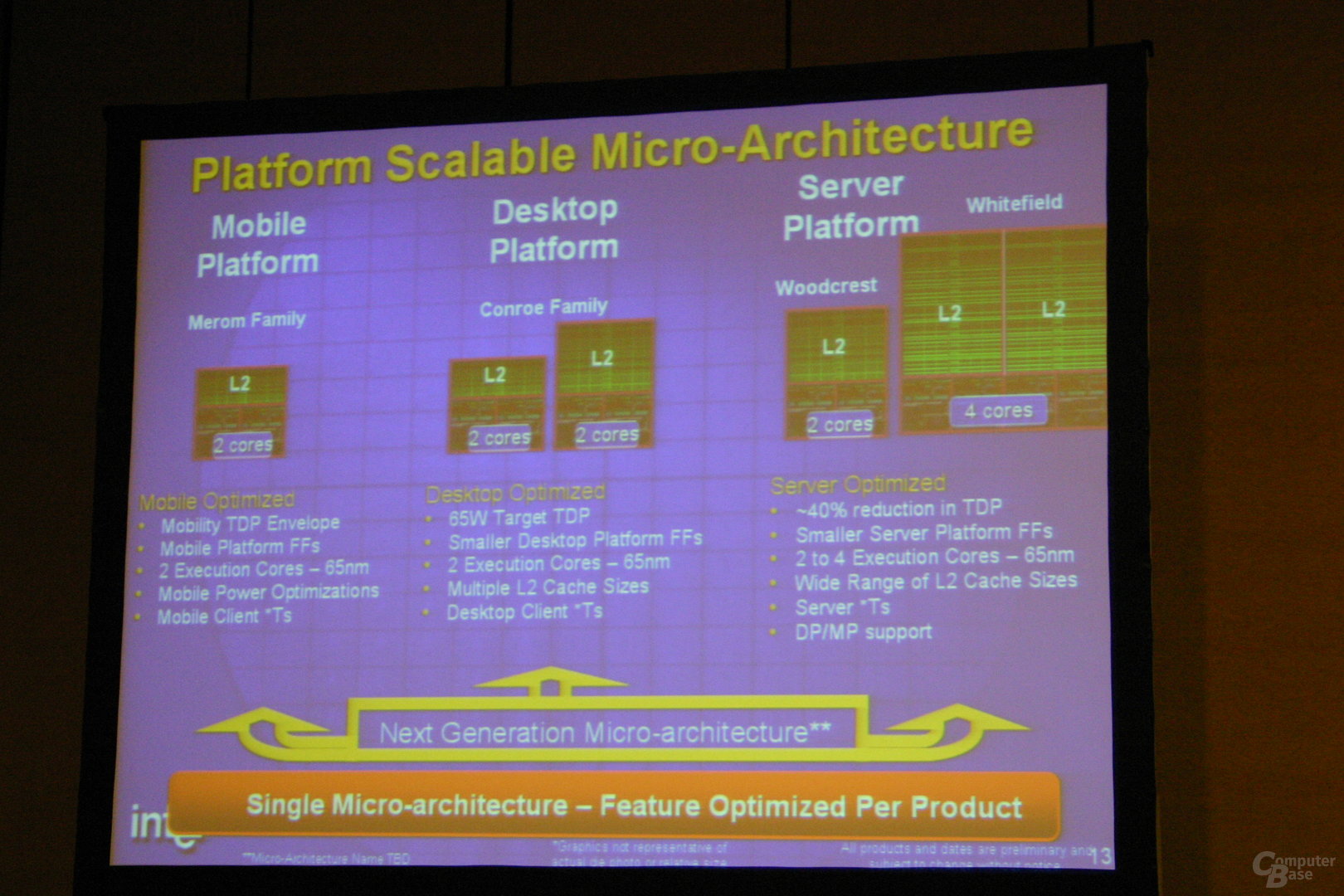

Mit der neuen Architektur, die derzeit noch keinen eigenen Codenamen erhalten hat, möchte Intel die Vorteile der aktuell eingesetzten Architekturen vereinen und eine gemeinsame Basis für alle Produktbereiche – sei es Desktop, Mobile oder Server – schaffen.

Von NetBurst, der beim Pentium 4 oder Pentium D eingesetzten Architektur, kommen der bewährte Frontside-Bus, die 64-Bit-Technologie und die bekannten *T-Features wie VT (Vanderpool) und LT (LaGrande). Der Pentium M wird sich mit seinen Stromsparfeatures in der neuen Architektur wieder finden. Genau genommen scheint in die neue Architektur – soweit bekannt – deutlich mehr vom Pentium M als vom Pentium 4 eingeflossen zu sein, denn Features wie VT oder LT werden Anfang 2006 in der neuen Napa-Plattform ebenso verfügbar sein.

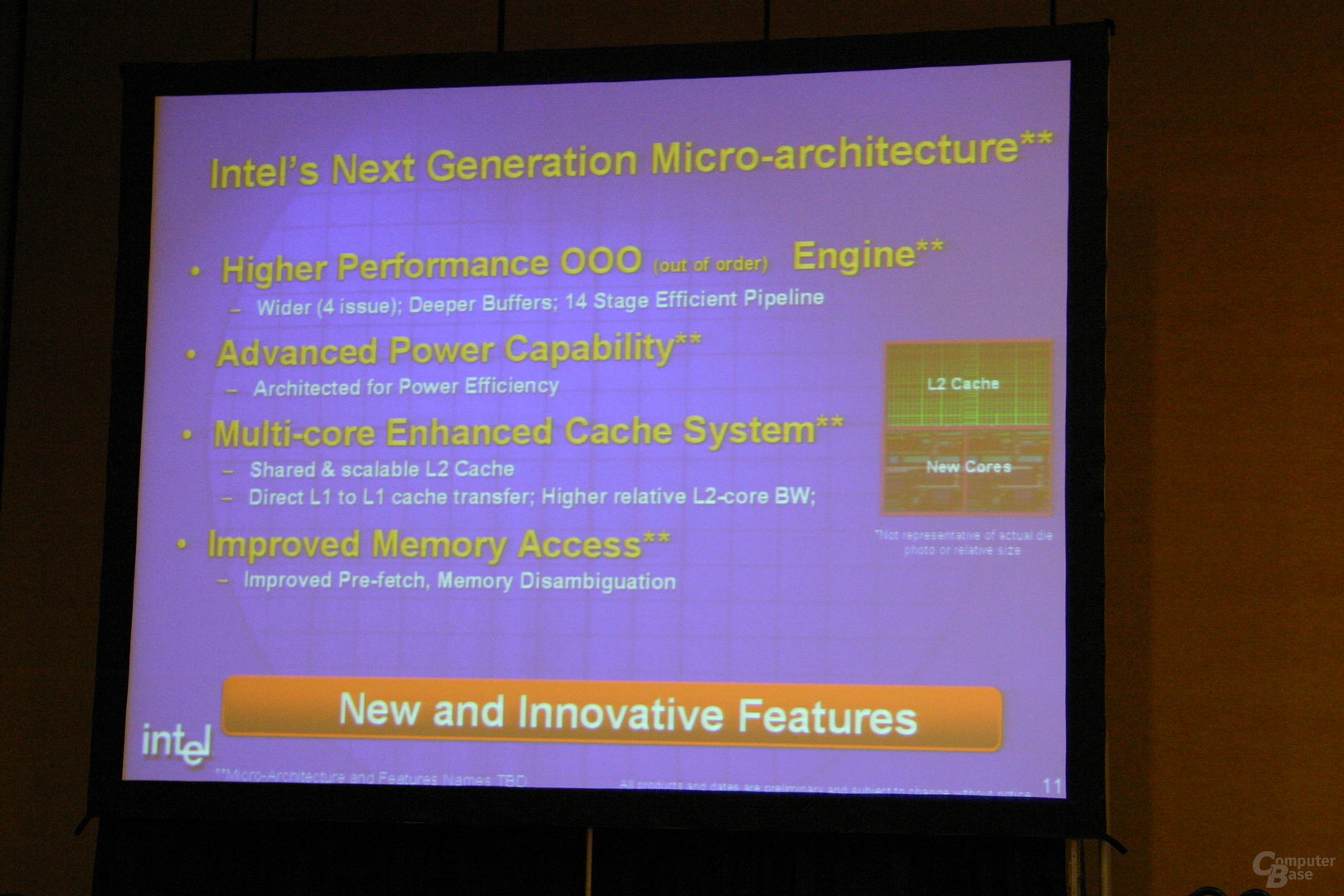

Die neue Architektur kommt mit einer 14 Stages langen Pipeline daher und ist damit – laut Intel selbst – etwas länger als die des Pentium M, deren Pipeline-Länge niemals offiziell bekannt gegeben wurde. Während mit der neuen Architektur eine Instruktion nach 14 Taktzyklen den Prozessor durchlaufen hat, sind beim aktuellen Pentium 4/Pentium D mit Prescott/Smithfield zum Abschluss eines Befehls 31 Zyklen nötig.

In Sachen Cache hat man sich ebenfalls vom kommenden Dual-Core-Pentium M „Yonah“ inspirieren lassen. Wie dieser, werden die Prozessoren auf Basis der neuen Architektur einen großen, gemeinsamen Cache bieten, auf den zwei Prozessorkerne gemeinsam zugreifen können. Jeder Prozessorkern besitzt einen eigenen L1-Cache, wobei Inhalte untereinander ausgetauscht werden können.

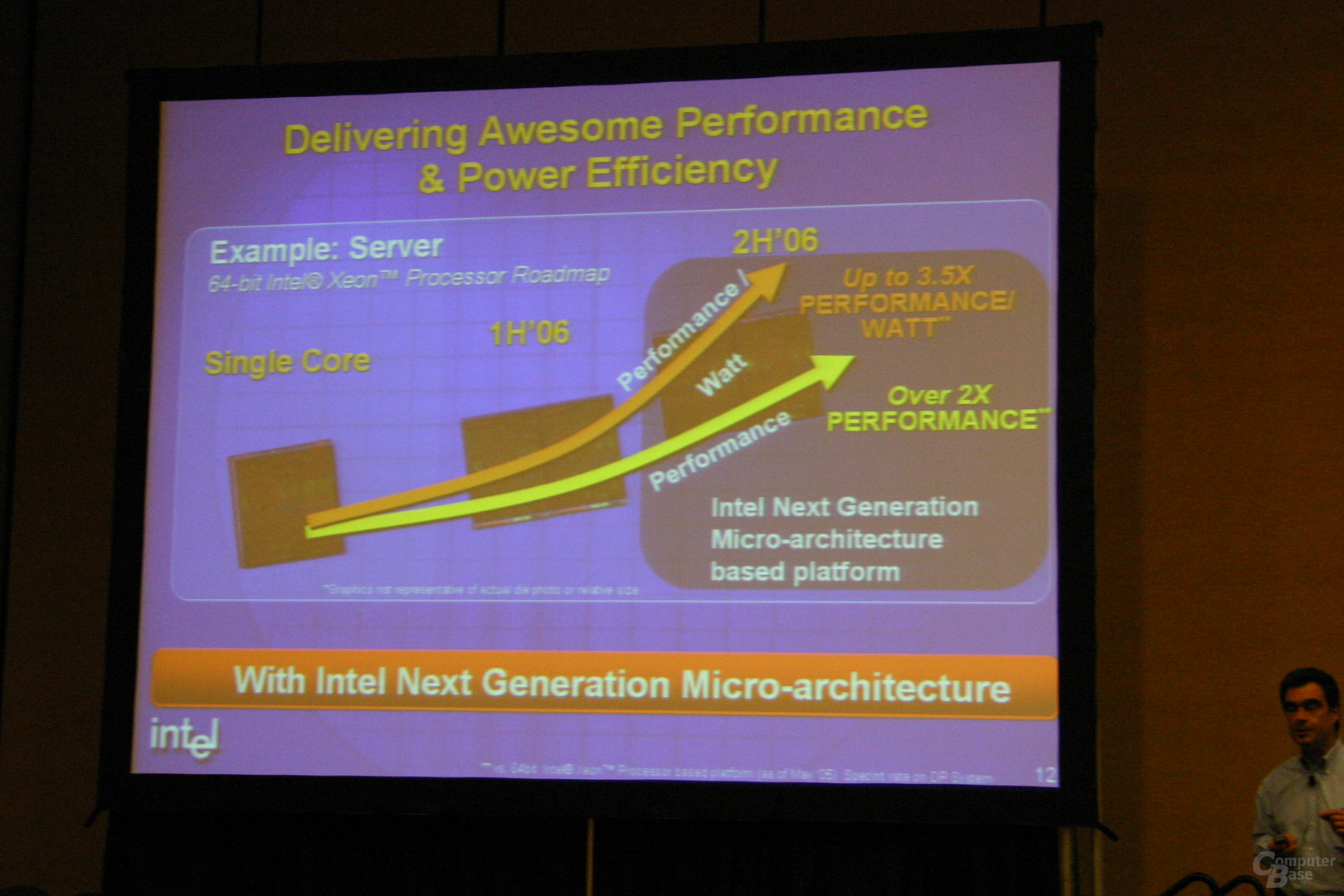

Konkrete Ausprägungen der neuen Architektur stellte Intel ebenfalls vor: Im Notebook-Segment darf der Merom mit einem 2 MB großen L2-Cache seine Stärken ausspielen. Er wird als Low Voltage-Variante mit einer Thermal Design Power von 5 Watt daher kommen. Der Merom läuft auf der Napa-Plattform im Sockel 479. Im Desktop ist der Conroe mit 65 nm und 2 oder 4 MB Cache zusammen mit dem Broadwater-Chipsatz anzutreffen. Die Server-Modelle mit 80 Watt TDP starten mit 4 MB L2-Cache (Woodcrest, Xeon DP), werden in Form des Whitefield (Dual Woodcrest) jedoch bis zu 16 MB Cache zur Verfügung haben.