Intels „Core Solo“ und „Core Duo“: Ein Neuanfang?

Einleitung

Rund 13 Jahre sind vergangen, seit im Frühjahr 1993 das erste Mal ein Silizium-Baby unter dem Namen „Pentium“ das Licht der Welt erblickte und die alte Namensgebung – bestehend aus der Kombination von Generation und Architektur – abgelöst wurde. Eine neue Ära brach an. Und was für eine! Mit der Zeit hat sich der Name „Pentium“ etabliert wie kaum ein anderer. Zu Recht lässt sich behaupten, dass „Pentium“ eine ähnlich starke Assoziation zur Firma Intel hervorruft, wie es bei „Windows“ und Microsoft der Fall ist.

Es bedarf schon einer gehörigen Portion Mut und Selbstbewußtsein sich von so einem starken Markennamen zu trennen, der dazu beigetraten hat, dass Intel Studien zufolge auf Platz fünf der weltweit stärksten Marken liegt und seit Jahren „für Innovation und Qualität“ steht – auch wenn Intel diesem Ruf gerade in letzter Zeit nicht immer gerecht geworden ist. Nicht zuletzt durch aggressive Marketing-Politik aus eigenem Budget, ein gewichtiger Teil der „Intel inside“-Kampagne, und PC-Herstellern wie z.B. Dell wurde Pentium dennoch zu einem Gütesiegel eines qualitativ guten PCs oder Notebooks geformt.

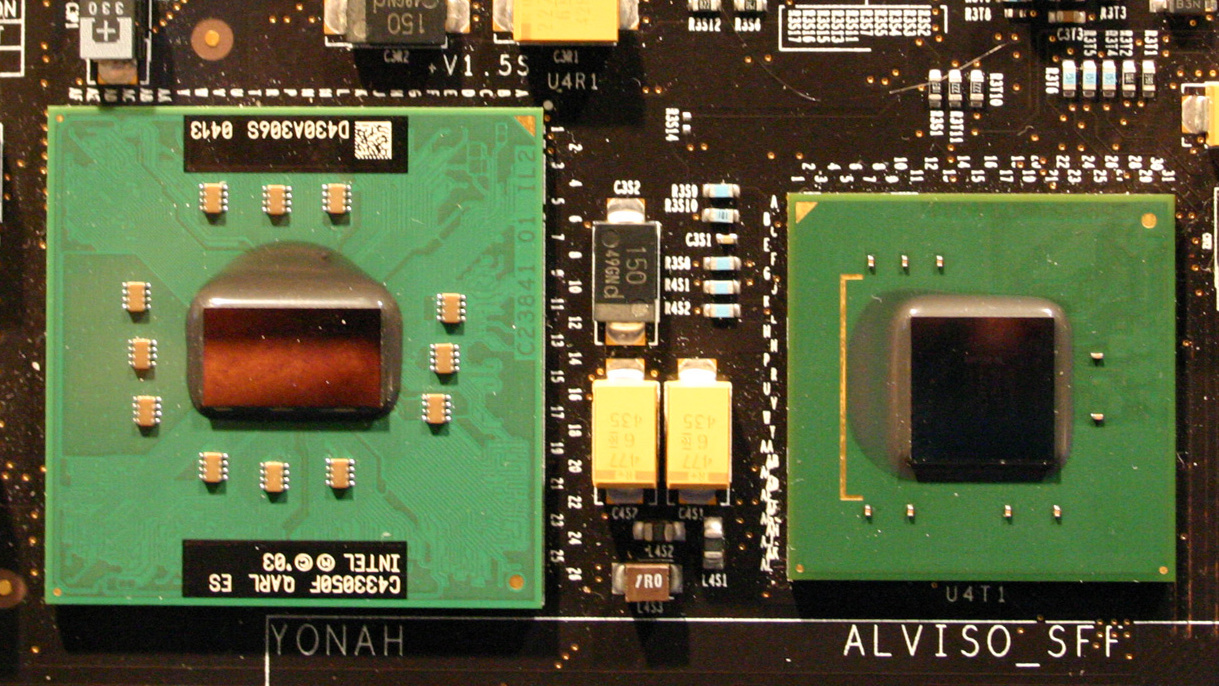

Und dies soll nun vorbei sein? Es scheint so, denn unter dem Namen „Core Solo“ und „Core Duo“ erscheinen erstmals seit dem Sorgenkind „Itanium“ für Server oder der Value-Linie „Celeron“ neue Prozessoren für den Massenmarkt, welche nicht mehr auf den Namen Pentium (in diesem Fall Pentium M) hören. Zunächst wird es nur den mobilen Sektor treffen, doch Mitte 2006 wird auch die Desktop-Linie aller Voraussicht nach dasselbe Schicksal ereilen. Doch immer der Reihe nach.