Neues zu Intels Workstation-Plänen

Wie in der Vergangenheit schon öfter berichtet, wird Intel im Zuge der Einführung der neuen Prozessoren mit den Codenamen „Conroe“, „Merom“ und „Woodcrest“ im 3. Quartal dieses Jahres eine komplett neue Prozessor-Generation ins Rennen schicken.

Nun sind weitere (Rand-)Informationen aufgetaucht, welche über das bisher bekannte hinausgehen. So soll der kommende Core-Duo-Prozessor für den Desktop auf Basis des Conroe-Kerns (E4x00, E6x00) nicht nur die aktuellen Pentium-D/EE-Serien ablösen, sondern auch in Uni-Prozessor-Workstation- und -Server-Systemen seinen Platz finden. Als Basis für die Server-Systeme (Kaylo-Plattform) mit Core-Duo-Unterstützung dient eine weiterentwickelte Version des E7230 (Mukilteo)-Chipsatzes, welche auf den Namen Mukilteo-2/P hört. Die genaue Produktbezeichnung ist dabei noch nicht bekannt. Für Workstation-Systeme (Wyloway-Plattform) ist der bereits für den aktuellen Pentium 4/D/EE erhältliche i975X-Chipsatz angedacht.

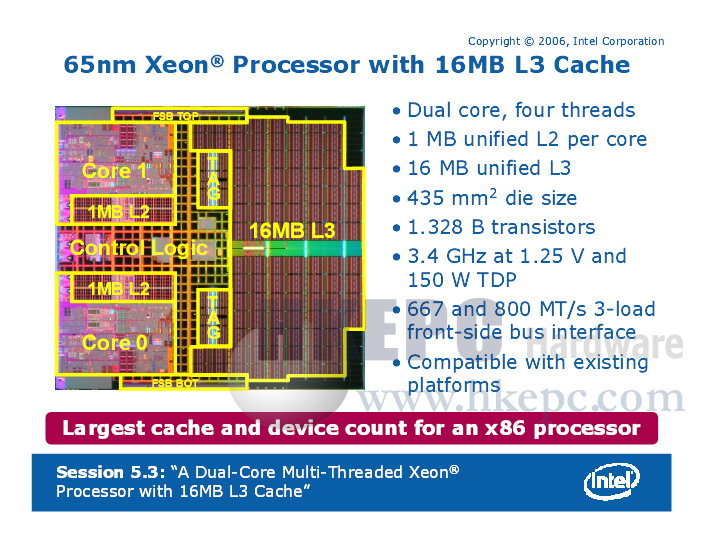

Die kürzlich aufgetauchte Quad-Core-Variante „Clovertown“ wird neben dem Einsatz in Dual-Prozessor-Servern mit 5000P (Blackford) auch in Dual-Prozessor-Workstations mit 5000X (Greencreek) zum Einsatz kommen. Der unter dem Codenamen „Tigerton“ geführte Quad-Core-Prozessor für Multi-Prozessor-Systeme scheint im Gegenzug von Anfang 2007 auf das zweite Halbjahr 2007 geschoben worden zu sein. Der mit 1,3 Milliarden Transistoren und 435 mm² Chip-Size zweitschwerste Prozessor von Intel (Itanium „Montecito“ 1,7 Mrd) unter dem Codenamen „Tulsa“ wird somit als letztes Glied der Kette die aktuelle Netburst-Architektur behalten.

Der in 65 nm gefertigte Dual-Core „Tulsa“ mit Intels Hyperthreading-Technologie ermöglicht dem Xeon MP die gleichzeitige Ausführung von insgesamt vier Threads. Er verfügt neben 1 MByte L2-Cache pro Kern auch über einen 16 MByte großen, gemeinsamen L3-Cache. Die Taktfrequenz beträgt dabei bis zu 3,4 GHz bei einem 800 MHz schnellen Frontside-Bus.

Mit dem Quad-Core „Tigerton“ wird sich Intel aller Voraussicht nach vom bisher üblichen Frontside-Bus trennen und mit CSI (Common System Interface) ein Hyper-Transport ähnliches Interface sowie womöglich auch einen integrierten Memory-Controller wie bei AMDs K8-Architektur (Athlon 64) verwenden.

Mit Dank an Simon Knappe

für das Einsenden dieser Meldung.