IDF: Intels neue Architektur heißt „Core“

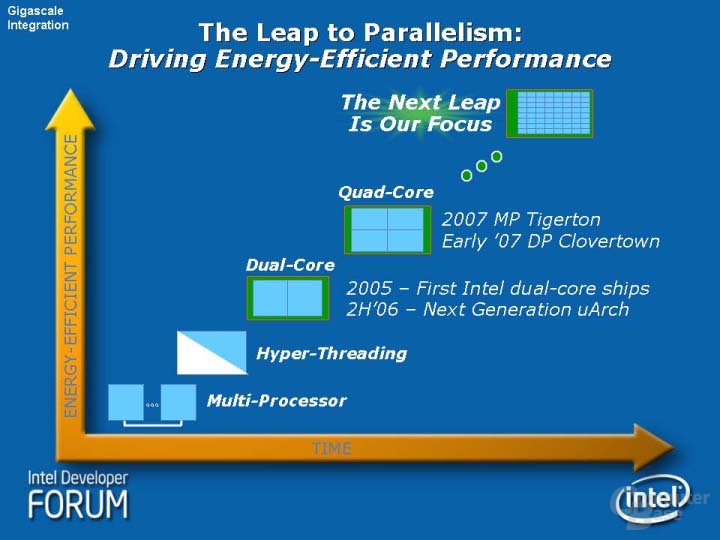

Im Rahmen seines Developer Forum Spring 2006 gab Intel heute Details ihrer neuen Mikroarchitektur (Next Generation Microarchitecture) bekannt. Diese hört nun auf den offiziellen Namen „Core-Mikroarchitektur“ und bildet die Grundlage für Server-, Desktop- und mobile Prozessoren mit Multikern-Technologie, die später in diesem Jahr vorgestellt werden.

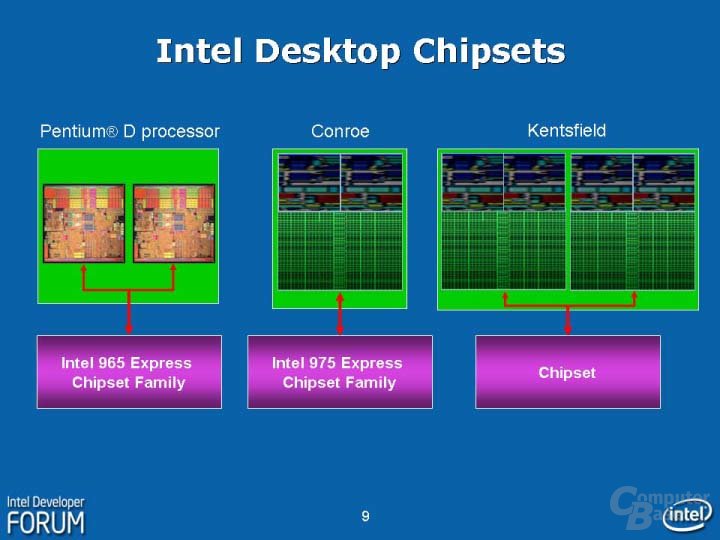

Die ersten Intel Core Mikroarchitektur Produkte mit den Codenamen Conroe (Desktop), Merom (Mobile) und Woodcrest (Server, Xeon DP) werden auf Basis der 65nm-Herstellungstechnologie produziert werden und sollen den Weg für die Entwicklung von leiseren kleineren Notebooks und Desktop-Computern in modernen Designs sowie neuen Servern ebnen, die Strom- und Gebäudekosten sparen. Die Core-Mikroarchitektur verfügt über Ausstattungsmerkmale wie verbesserte Sicherheit (La Grande), Virtualisierung (Vanderpool) und Manageability (iAMT), die Endanwendern und Unternehmen zu Gute kommen sollen.

Justin Rattner, Intel Senior Fellow und Chief Technology Officer, erklärte, dass Intels Core-Mikroarchitektur die Voraussetzungen dafür liefere, eine höhere Leistung bei geringerem Energieverbrauch zu erzielen, wie dies beim Core-Duo-Prozessor der Fall sei. Er folgt den Stromsparansatz, der zunächst in der Pentium-M-Mikroarchitektur (Codename Banias) realisiert wurde. Dieser wurde ausgebaut und verfügt nun über zahlreiche neue Technologien sowie einige (wenige) Pentium 4-Prozessortechnologien wie etwa die SSE-Befehlssätze und die 64-Bit-Erweiterung EM64T. Ansonsten spiegelt sich in der neuen Architektur nur wenig vom Pentium 4 wieder.

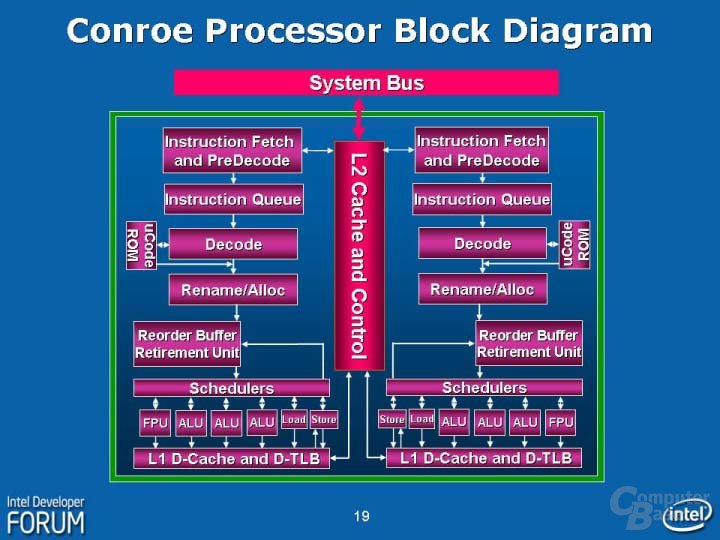

- So wurde die Länge der Out-of-Order-Execution-Pipeline drastisch verkürzt und ist mit 14 Stufen im Vergleich zu der des Pentium 4 „Prescott“ mit 31 Stages weniger als halb so lang. Außerdem ist die Core-Architektur 4-fach-skalar und erlaubt damit jedem Kern bis zu vier Befehle (bisher drei) gleichzeitig zu beenden. Die neuen Prozessoren führen damit mehr Befehle pro Taktzyklus aus. Intel fasst diese Eigenschaft unter der Bezeichnung „Wide Dynamic Execution“ zusammen.

- Intel Intelligent Power Capability dagegen beinhaltet Funktionen, die den Stromverbrauch weiter senken, indem sie auf intelligente Art und Weise einzelne logische Subsysteme des Prozessors nur dann einschaltet, wenn diese benötigt werden. Bei den Pentium M-Prozessoren vergangener Tage konnten beispielsweise Teile des L2-Caches deaktiviert werden. Wie weit der Gedanke mit der Core-Architektur getrieben wurde, hat der Halbleiterriese noch nicht bekanntgegeben.

- Wie der aktuelle Notebook-Prozessor Core Duo (Codename Yonah) beinhaltet auch die neue Architektur einen gemeinsam genutzten L2 Cache zu Senkung des Strombedarfs durch Minimieren von Datenverkehr zum Speicher und steigert die Leistung, indem ein Kern den gesamten Cache dynamisch nutzen kann, wenn der andere Kern untätig ist. Das ganze hört auf die Bezeichnung Advanced Smart Cache.

- Intel Smart Memory Access ist ein weiteres Merkmal, das die Systemleistung verbessern soll, indem die Latenzzeit des Speichers optimal genutzt und dadurch die Bandbreite des Memory Subsystems optimiert wird.

- Mit Advanced Digital Media Boost werden alle 128-Bit SSE-, SSE2- und SSE3-Befehle nun innerhalb eines einzigen Taktzyklus ausgeführt. Praktisch bedeutet dies eine Verdopplung der Ausführungsgeschwindigkeit dieser Befehle, die häufig in multimedialen und grafischen Anwendungen zum Einsatz kommen. Die Unterstützung von SSE4 wurde von Intel noch nicht offiziell bestätigt.

In seiner Rede zeigte Rattner, wie der Conroe bei rund 40 Prozent mehr Leistung rund 40 Prozent weniger Strom (TDP: 64 Watt) verglichen mit Intels derzeitigem Pentium D 950 (TDP: 130 Watt) verbraucht. Bei einer Live-Demo von Office 12 war Conroe noch schneller: nach 11,4 Sekunden konnte er seine Arbeit beendet, der Pentium D musste dagegen 28,7 Sekunden rechnend verbringen.

Rattner zeigte zudem Leistungsgewinne im Enterprise- und Mobile-Bereich auf. So soll der Server-Vertreter der neuen Architektur „Woodcrest“ (ein Dual-Core-Prozessor mit 4 MB Cache) im Vergleich zur aktuellen Dual-Core-Ausführung des Xeon DP mit 2,8 GHz (Codename Paxville DP) 80 Prozent mehr Performance bei einem um 35 Prozent gesenkten Verbrauch bieten.

Der Notebook-Chip Merom wird im Vergleich zum aktuellen Dual-Core-Chip „Yonah“, der bereits unter der Marke Core Duo im Handel erhältlich ist, bei in etwa gleichem Verbrauch nur 20 Prozent mehr Leistung bieten. Hier zeigt sich einmal mehr, wie sehr sich die neue Architektur an die der Pentium M-Prozessoren anlehnt – kein Wunder, wurden beide doch in Haifa, Israel, entwickelt.

Intel geht davon aus, dass die Auslieferung von Prozessoren auf Basis der Core-Mikroarchitektur im dritten Quartal 2006 beginnen wird.