Intel Core 2 Duo E6700 und E6600 im Test: Von Zeichen und Wundern

2/20Technische Daten und Features

Intels neue, beim Core 2 Duo/Extreme eingesetzte Prozessorarchitektur unterscheidet sich außerordentlich stark von dem, was uns beim Pentium 4 und dessen Dual-Core-Version Pentium D vertraut ist. Im Folgenden wird auf die neue Architektur nur sehr oberflächlich eingegangen, da zu diesem Zeitpunkt die Performance im Vordergrund stehen soll. Eine detaillierte Abhandlung der Core-Architektur wird in einem gesonderten Artikel erfolgen.

| Merkmale | Core 2 Duo Core 2 Extreme |

Pentium D 9xx, Pentium Extreme Edition 9x5 |

Pentium D 8xx, Pentium Extreme Edition 840 |

Pentium 4 6xx, Pentium 4 Extreme Edition 3,73 |

|---|---|---|---|---|

| Logo |  |

|

|

|

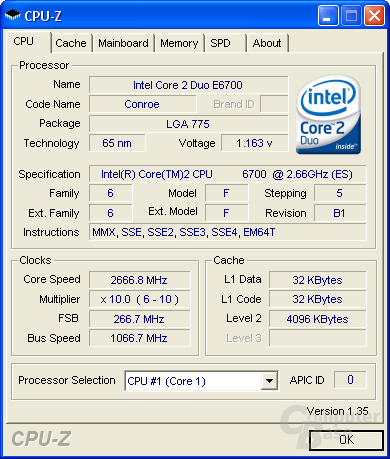

| Codename | Conroe Allendale* |

Presler | Smithfield | Prescott 2M |

| Taktrate oder Modellnummer (Takt in GHz) |

E6300 (1,86)* E6400 (2,13)* E6600 (2,4) E6700 (2,66) X6800 (2,93) |

920 (2,8) 930 (3,0) 940 (3,2) 950 (3,4) 960 (3,6) XE955 (3,46) XE965 (3,73) |

820 (2,8) 830 (3,0) 840 (3,2) EE840 (3,2) |

630 (3,0) 640 (3,2) 650 (3,4) 660 (3,6) 670 (3,8) EE 3733 MHz |

| Fertigung | 65 nm | 65 nm | 90 nm | 90 nm |

| Sockel | Sockel 775 | Sockel 775 | Sockel 775 | Sockel 775 |

| Dual-Core | ✓ | ✓ | ✓ | X |

| Multithreading | X | ✓ (Nur XE) | ✓ (Nur XE) | ✓ |

| Frontside-Bus | 1066 MHz QDR | 800 MHz QDR 1066 MHz QDR |

800 MHz QDR | 800 MHz QDR 1066 MHz QDR |

| Frontside-Bus-Last | 1 | 2 | 2 | 1 |

| Peripherieinterface | Externe Controller | Externe Controller | Externe Controller | Externe Controller |

| Speichercontroller | Externe Controller | Externe Controller | Externe Controller | Externe Controller |

| Transistoren | 167 Mio.* 291 Mio. |

376 Mio. | 230 Mio. | 169 Mio. |

| Chipgröße | 111 mm²* 143 mm² |

162 mm² | 206 mm² | 135 mm² |

| L1-Execution-Cache | 2x32 kB | 2x12.000 µ-Ops | 2x12.000 µ-Ops | 12.000 µ-Ops |

| L1-Daten-Cache | 2x32 kB | 2x16 kB | 2x16 kB | 16 kB |

| L2-Cache | 1x2048 kB* 1x4096 kB |

2x2048 kB | 2x1024 kB | 2048kB |

| L2-Anbindung | 256 Bit | 256 Bit | 256 Bit | 256 Bit |

| L2-Modus | L1 inclusive | L1 inclusive | L1 inclusive | L1 inclusive |

| Cache insgesamt | 2048 kB* 4096 kB |

4096 kB | 2048 kB | 1024 kB |

| Merkmale | Athlon 64 X2 Athlon 64 FX-62 |

Athlon 64 Sempron 64 |

Athlon 64 X2 Athlon 64 FX-60 |

Athlon 64 Athlon 64 FX |

|---|---|---|---|---|

| Codename | Windsor (1 MB/512 kB) | Orleans (512 kB) Manila (256 kB/128kB) |

Manchester (1 MB) Toledo (2 MB) |

Venice (512 kB) San Diego (1 MB) |

| Logo |  |

|

|

|

| Taktrate oder Modellnummer (Takt in GHz) |

3800+ (2,0, 2x 512 kB) 4000+ (2,0, 2x 1MB) 4200+ (2,2, 2x 512 kB) 4400+ (2,2, 2x 1MB) 4600+ (2,4, 2x 512 kB) 4800+ (2,4, 2x 1MB) 5000+ (2,6, 2x 512 kB) FX-62 (2,8, 2x 1MB) |

Athlon 64 3800+ (2,4 GHz 512kB) 3500+ (2,2 GHz, 512kB) 3200+ (2,0 GHz, 512kB) Sempron 64 3600+ (2,0 GHz, 256kB) 3500+ (2,0 GHz, 128kB) 3400+ (1,8 GHz, 256kB) 3200+ (1,8 GHz, 128kB) 3000+ (1,6 GHz, 256kB) 2800+ (1,6 GHz,128kB) |

3800+ (2,0) 4200+ (2,2) 4400+ (2,2) 4600+ (2,4) 4800+ (2,4) FX-60 (2,6) |

3000+ (1,8) 3200+ (2,0) 3500+ (2,2) 3700+ (2,2) 3800+ (2,4) 4000+ (2,4) FX-55 (2,6) FX-57 (2,8) |

| Fertigung | 90 nm | 90 nm | 90 nm | 90 nm |

| Sockel | Sockel AM2 (940) | Sockel AM2 (940) | Sockel 939 | Sockel 939 |

| Dual-Core | ✓ | X | ✓ | X |

| Multithreading | X | X | X | X |

| Frontside-Bus | entfällt | entfällt | entfällt | entfällt |

| Frontside-Bus-Last | entfällt | entfällt | entfällt | entfällt |

| Peripherieinterface | 8 GB/s HyperTransport | 8 GB/s HyperTransport 6,4 GB/s HyperTransport |

8 GB/s HyperTransport | 8 GB/s HyperTransport |

| Speichercontroller | integriert für DDR2-800 |

integriert für DDR2-667 |

integriert für DDR-400 |

integriert für DDR-400 |

| Transistoren | 153,8 Mio. (2x512 kB) 227,4 Mio. (2x 1MB) |

kA (128 kB) 81,1 Mio (256 kB) 81.1 Mio (512 kB) |

154 Mio. (2x512 kB) 233,2 Mio. (2x1 MB) |

68,5 Mio. (512 kB) 114 Mio. (1 MB) |

| Chipgröße | 183 mm² (2x512 kB) 230 mm² (2x 1MB) |

kA (128 kB) 103 mm² (256 kB) 103mm² (512 kB) |

147 mm² (2x512 kB) 199 mm² (2x 1MB) |

83,5 mm² (512 kB) 115 mm² (1MB) |

| L1-Execution-Cache | 2x64 kB | 64 kB | 2x64 kB | 64 kB |

| L1-Daten-Cache | 2x64 kB | 64 kB | 2x64 kB | 64 kB |

| L2-Cache | 2x512 kB 2x1024kB |

128 kB 256kB 512kB |

2x512 kB 2x1024kB |

512kB 1024kB |

| L2-Anbindung | 128 Bit | 128 Bit | 128 Bit | 128 Bit |

| L2-Modus | L1 exclusive | L1 exclusive | L1 exclusive | L1 exclusive |

| Cache insgesamt | 1280 kB 2304 kB |

256 384kB 640 kB |

1280 kB 2304 kB |

640 kB 1152 kB |

| Merkmale | Core 2 Duo Core 2 Extreme |

Pentium D 9xx, Pentium Extreme Edition 9x5 |

Pentium D 8xx, Pentium Extreme Edition 840 |

Pentium 4 6xx, Pentium 4 Extreme Edition 3,73 |

|---|---|---|---|---|

| Logo |  |

|

|

|

| Energiesparfunktion | C1E, Enhanced SpeedStep (EIST) |

Ab C1-Stepping 9x0 (C1E, EIST) 965 (C1E) |

C1E, Enhanced SpeedStep (EIST) (XE nicht) |

C1E, Enhanced SpeedStep (EIST) (XE nicht) |

| Date Execution Prevention (NX-Bit) |

✓ | ✓ | ✓ | ✓ |

| 64-Bit-Technologie | ✓ (EM64T) | ✓ (EM64T) | ✓ (EM64T) | ✓ (EM64T) |

| Virtualisierungs- Technologie |

✓ (Vanderpool) | ✓ (Vanderpool) | X | ✓ (Vanderpool) Nur P4 672, 662 |

| CPU-Architektur | 14-stufige Pipeline (Core) |

31-stufige Pipeline (Netburst) |

31-stufige Pipeline (Netburst) |

31-stufige Pipeline (Netburst) |

| Befehlssätze | MMX SSE SSE2 SSE3 +16 weitere |

MMX SSE SSE2 SSE3 |

MMX SSE SSE2 SSE3 |

MMX SSE SSE2 SSE3 |

| Merkmale | Athlon 64 X2 Athlon 64 FX-62 |

Athlon 64 Sempron 64 |

Athlon 64 X2 Athlon 64 FX-60 |

Athlon 64 Athlon 64 FX |

|---|---|---|---|---|

| Logo |  |

|

|

|

| Energiesparfunktion | Cool'n'Quiet | Cool'n'Quiet | Cool'n'Quiet | Cool'n'Quiet |

| Date Execution Prevention (NX-Bit) |

✓ | ✓ | ✓ | ✓ |

| 64-Bit-Technologie | ✓ (AMD64) | ✓ (AMD64) | ✓ (AMD64) | ✓ (AMD64) |

| Virtualisierungs- Technologie |

✓ (Pacifica) | ✓ (Pacifica) (Sempron nicht) |

X | X |

| CPU-Architektur | 17-stufige (FPU) 12-stufige (ALU) Pipeline |

17-stufige (FPU) 12-stufige (ALU) Pipeline |

17-stufige (FPU) 12-stufige (ALU) Pipeline |

17-stufige (FPU) 12-stufige (ALU) Pipeline |

| Befehlssätze | MMX 3DNow! 3DNow!+ SSE SSE2 SSE3 |

MMX 3DNow! 3DNow!+ SSE SSE2 SSE3 |

MMX 3DNow! 3DNow!+ SSE SSE2 SSE3 |

MMX 3DNow! 3DNow!+ SSE SSE2 SSE3 |

Auch wenn die Core-Mikroarchitektur Gegenstand eines gesonderten Artikels werden soll, darf ein kurzer Überblick über die fünf Eckpfeiler nicht fehlen:

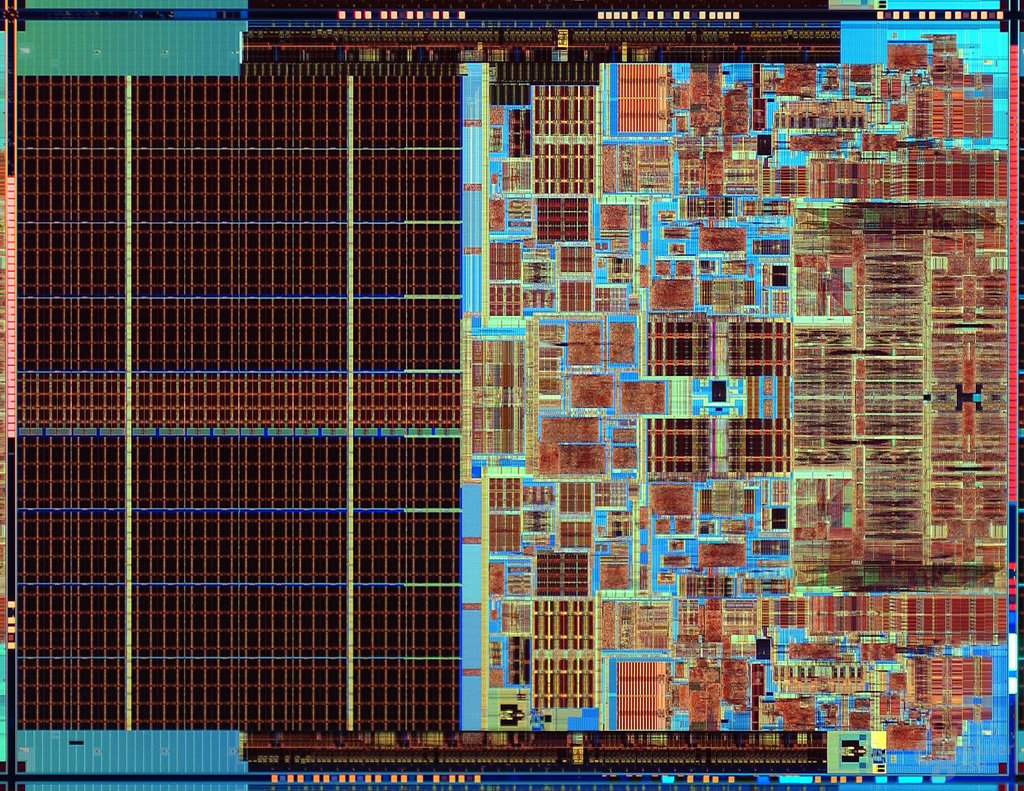

- Die Länge der Out-of-Order-Execution-Pipeline wurde drastisch verkürzt und ist mit 14 Stufen im Vergleich zu der des Pentium 4 „Prescott“ mit 31 Stages weniger als halb so lang. Außerdem ist die Core-Architektur 4-fach-skalar und erlaubt damit jedem Kern bis zu vier Befehle (bisher drei) gleichzeitig zu beenden. Die neuen Prozessoren führen damit mehr Befehle pro Taktzyklus aus. Intel fasst diese Eigenschaft unter der Bezeichnung „Wide Dynamic Execution“ zusammen.

- „Intel Intelligent Power Capability“ dagegen beinhaltet Funktionen, die den Stromverbrauch weiter senken, indem sie auf intelligente Art und Weise einzelne logische Subsysteme des Prozessors nur dann einschaltet, wenn diese benötigt werden. Bei den Pentium M-Prozessoren vergangener Tage konnten beispielsweise Teile des L2-Caches deaktiviert werden. Wie weit der Gedanke mit der Core-Architektur getrieben wurde, hat der Halbleiterriese noch nicht bekanntgegeben.

- Wie der aktuelle Notebook-Prozessor Core Duo (Codename „Yonah“) beinhaltet auch die neue Architektur einen gemeinsam genutzten L2-Cache zur Senkung des Strombedarfs durch Minimieren von Datenverkehr zum Speicher und steigert die Leistung, indem ein Kern den gesamten Cache dynamisch nutzen kann, wenn der andere Kern untätig ist. Das Ganze hört auf die Bezeichnung „Advanced Smart Cache“.

- „Intel Smart Memory Access“ ist ein weiteres Merkmal, das die Systemleistung verbessern soll, indem die Latenzzeit des Speichers optimal genutzt und dadurch die Bandbreite des Memory Subsystems optimiert wird.

- Mit „Advanced Digital Media Boost“ werden alle 128 Bit SSE-, SSE2- und SSE3-Befehle nun innerhalb eines einzigen Taktzyklus ausgeführt. Praktisch bedeutet dies eine Verdopplung der Ausführungsgeschwindigkeit dieser Befehle, die häufig in multimedialen und grafischen Anwendungen zum Einsatz kommen. Darüber hinaus bietet die neue Architektur 16 neue Befehle, die unter der Bezeichnung Merom New Instructions entwickelt wurden. Es wurde spekuliert, dass diese den Namen SSE4 erhalten werden. Dem ist jedoch nicht so. Der Prozessorhersteller verzichtet zum jetzigen Zeitpunkt auf eine gesonderte Vermarktung.

Aufgrund der neuen Architektur und Änderung an der Stromversorgung werden für Core 2 Duo und Core 2 Extreme bis auf wenige Ausnahmen neue Mainboards benötigt. Diesem Thema werden wir uns auf der folgenden Seite widmen. Anschließend folgen die Performance-Messungen.