Intel Core 2 Extreme X6800 im Test: Sau schnell!

Vorwort

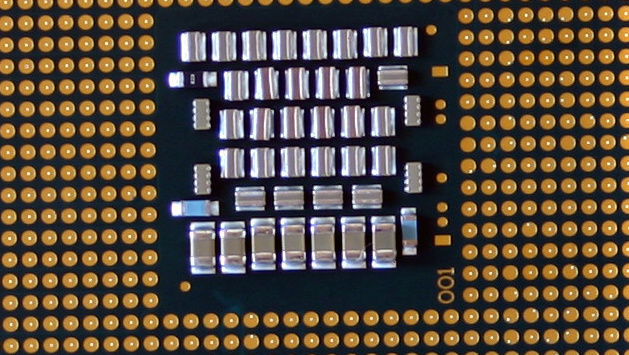

Am 27. Juli 2006 startet der Verkauf der Intel Core 2 Duo und Core 2 Extreme Prozessoren. Sie basieren auf der neuen Core-Mikroarchitektur die Gutes der Netburst-Architektur des Pentium 4 und der Banias-Architektur des Pentium M ineinander vereint.

Die neuen „Core 2 Duo“- und „Core 2 Extreme“-Prozessoren wurden unter dem Codenamen „Conroe“ entwickelt und haben unter diesem bereits in der Vergangenheit für viel Aufsehen gesorgt. Bereits im August 2005 standen – der Gerüchteküche nach – lauffähige Muster im A0-Stepping zur Verfügung. Noch im selben Monat präsentierte Intel im Rahmen des Intel Developer Forum Fall 2005 erste Eckdaten (Übersicht) zu seiner – damals noch namenlosen – Core-Mikroarchitektur und versprach eine deutliche Reduktion im Stromverbrauch und eine drastische Steigerung der Performance pro Watt.

Schon damals war klar, dass die Core-Architektur ein sehr enger Verwandter und stark weiterentwickelter Ableger der für Notebooks entwickelten „Pentium M“-Prozessoren ist und diesem – so die Schätzungen – bei gleichem Prozessortakt um bis zu 33 Prozent davon zieht. Im Laufe der Zeit folgten viele weitere Meldungen und Einblicke in die neue Core-Mikroarchitektur. Schließlich im Juni hatten wir die Gelegenheit einem Core 2 Duo E6700 mit 2,66 GHz Prozessortakt auf einem von Intel bereitgestellten System mit ausgewählten Anwendungen auf den Zahn zu fühlen.

Inzwischen stehen uns Testmuster des Core 2 Duo E6700 und der neuen Extreme Edition Core 2 Extreme X6800 zur Verfügung. Unsere Berichterstattung zu diesen neuen Boliden möchten wir in mehrere Abschnitte unterteilen.

Der bisher kaum in Erscheinung getretene Core 2 X6800 wird im Rahmen dieses Artikels behandelt. Benchmarks des Core 2 Duo E6600 (2,40 GHz) und Core 2 Duo E6700 (2,66 GHz) werden, ebenso wie die technische Vorstellung der neuen Architektur, im Rahmen gesonderter Berichte durchgeführt.

Lesezeichen

Aufgrund der Komplexität des Themas „Prozessoren“ ist es uns leider nicht möglich auf sämtliche Feinheiten wiederholt einzugehen. An dieser Stelle soll dabei auf interessante themenverwandte Veröffentlichungen hingewiesen werden.

- GPU-Leistung in Abhängigkeit der CPU

- Core 2 Duo E6700 Testdrive

- AMD Athlon 64 X2 5000+ Sockel AM2

- Intel Pentium Extreme Edition 965

- Athlon 64 FX-60 vs. Pentium XE 955

- Wohnzimmer-PCs: Intels Viiv startet durch

- Intels „Core Solo“ und „Core Duo“

- Grafikkartentreiber für Dual Core von ATi und nVidia

- Intel kündigt neue Prozessorarchitektur für zweites Halbjahr 2006 an

- Pentium D 840 und Extreme Edition 840

- Intel: Große Fortschritte bei 65 nm