IDF: Intel kündigt SSE4 für Penryn an

Intel hat Pläne für über 50 neue SSE4-Befehle bekannt gegeben. Sie sollen dazu dienen, die Leistungspotentiale von Intels zukünftiger Silizium-Herstellung im 45-Nanometer-Prozess, Codename Penryn, besser auszuschöpfen und Leistungsfähigkeit sowie Funktionen der Intel-Architektur weiter auszubauen.

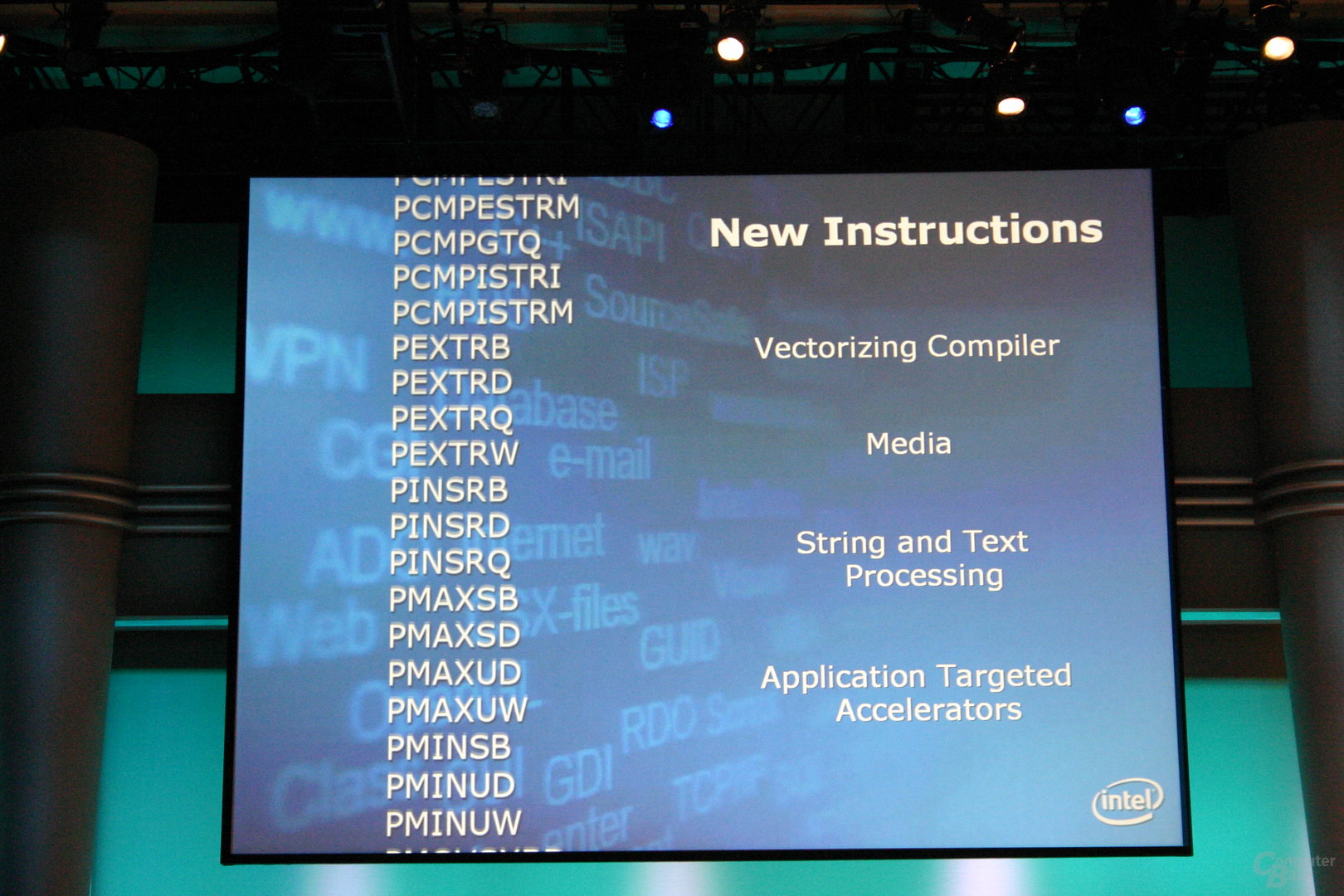

Die ersten Produkte mit SSE4-Befehlssatz werden in der zweiten Jahreshälfte 2007 mit der Einführung des 45nm-Fertigungsprozesses verfügbar sein, die darüber hinaus weitere Neuerungen für die Core-Architektur mitbringen werden. Die 50 neuen Single-Instruction-Multple-Data-(SIMD)-Befehle decken unter anderem die Bereiche Grafik, Video-Codierung und -Verarbeitung, 3D-Darstellung, Spiele, Web- und Anwendungsserver ab. Daneben gibt es Befehle, die eigentlich nicht unter den SIMD-Gedanken fallen, aber dennoch von vielen Entwicklern gewünscht wurden. Hierzu gehören Befehle für die Text-Verarbeitung, CRC-Überprüfung oder das Zählen von 1-Bits innerhalb einer Zahl (wird für Hamming-Distanz benötigt). Intel teilt daher den neuen Befehlssatz in die Bereiche SSE4 Vectorizing Compiler and Media Accelerators, SSE4 Efficient Accelerated String and Text Processing und Application Targeted Accelerators ein.

Die zwölf neuen Befehle (32 unter Berücksichtigung verschiedener Adressierungsarten), die mit Core 2 Duo eingeführt wurden, haben unterdessen einen offiziellen Namen erhalten, nachdem sie Intel bisher keines Wortes gewürdigt hat: Supplemental SSE3 (SSSE3). Sie werden bisher jedoch kaum eingesetzt. Neben dem synthetischen Benchmarks SiSoft Sandra wird Supplemental SSE3 Anfang 2007 auch in einem Video-Codec zum Encoden eingesetzt werden. In welchem, dass wollte Intel noch nicht verraten.

In einem Whitepaper hält Intel weitere Details zu allen neuen SSE4-Instruktionen bereit. Der Download ist kostenlos und öffentlich möglich.