IDF: Intel zeigt Prototypen mit 80 Kernen

Im Rahmen des Tera-Scale-Forschungsprojekt erkundet Intel Mittel und Wege hunderte von Prozessoren auf einem Chip unterzubringen. Im Rahmen des Intel Developer Forum Fall 2006 konnte Justin Rattner, Intel Senior Fellow und Chief Technology Officer, drei Bedeutende Neuentwicklungen präsentieren.

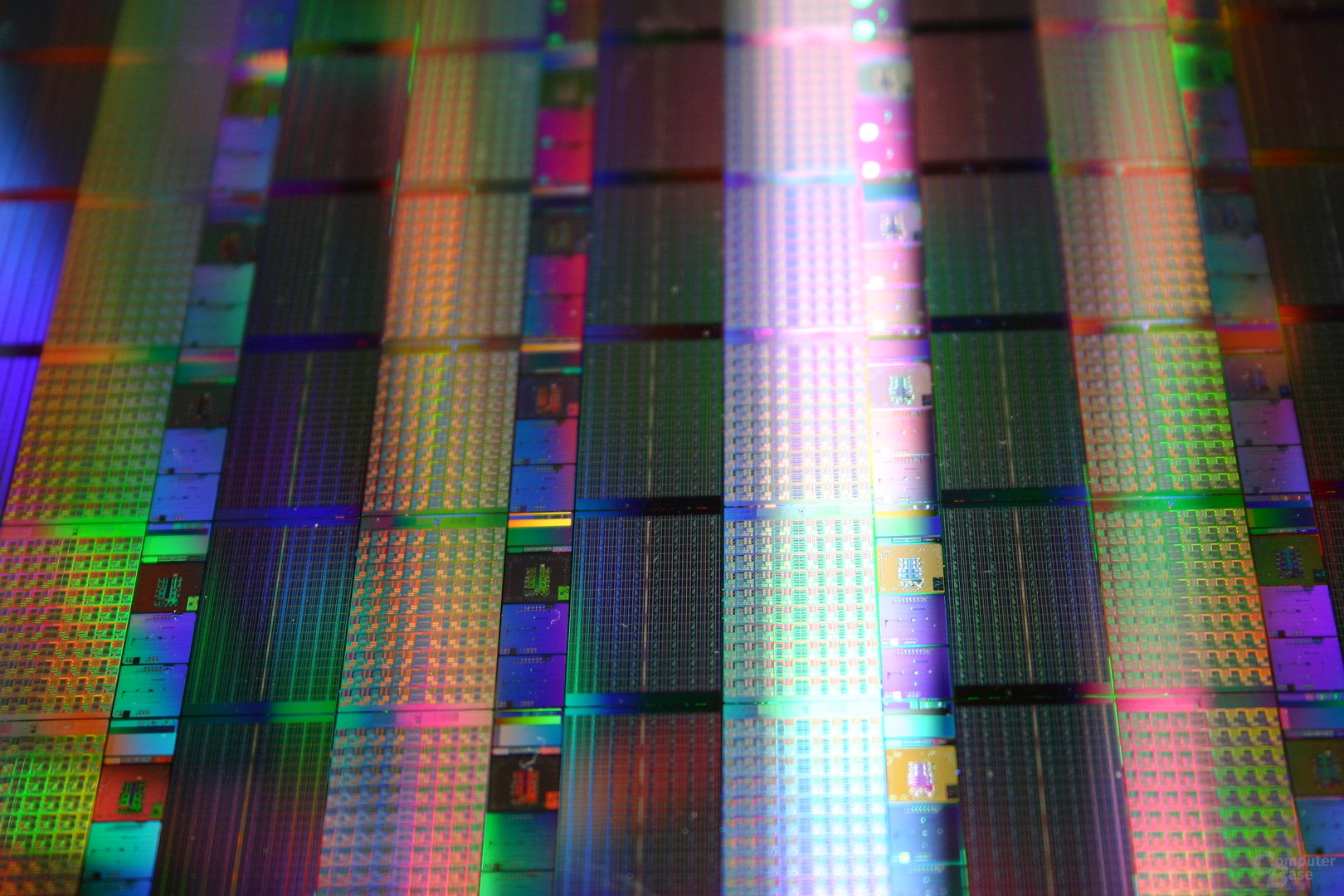

So stellte er erste Details eines Prozessor-Prototypen vor, der in den Teraflop-Bereich vorstößt. Dieser Prototyp ist der erste programmierbare Teraflop-Prozessor der Welt. Er verfügt über 80 einfache Einheiten (Cores) und ist mit 3,1 GHz getaktet. Zumindest ist das die Taktfrequenz die aufgrund von Softwaresimulation erwartet werden darf. Denn wie Rattner im Gespräch mitteilte, sind die Wafer mit diesen 80-Core-Prototypen erst letzte Woche eingetroffen. Die einzelnen Prozessoren wurden bisher weder aus dem Wafer ausgeschnitten, noch in eine Package verpackt. Dies wird in den kommenden Wochen passieren. Das Ziel dieses Versuchs-Prozessors ist es, Strategien für die Verbindung der einzelnen Prozessor-Elemente untereinander zu entwickeln, wenn Terabytes an Daten zwischen ihnen transportiert werden – von Core zu Core und von den Cores zu dem Speicher.

„Zusammen mit unseren aktuellen Durchbrüchen in der Silizium-Photonik adressieren diese experimentellen Chips die drei wichtigsten Anforderungen für Rechenleistung im Tera-Bereich – eine Leistungsfähigkeit von Billionen Operationen pro Sekunde, eine Speicherbandbreite von Terabytes pro Sekunde sowie eine I/O-Kapazität, die sich in Terabit pro Sekunde bemisst“, sagte Rattner. „Auch wenn die kommerzielle Anwendung dieser Technologien noch Jahre in der Zukunft liegt – es ist ein erster Schritt hin zu PCs und Servern mit Leistungen im Tera-Bereich.“

Existierende Prozessor-Designs bestehen aus hunderten Millionen von Transistoren. Das Design des neuen Teraflop-Chips besteht im Gegensatz dazu aus 80 Einheiten („tiles“), die in einer blockförmigen 8x10-Matrix angeordnet sind. Jede Einheit besteht aus einem kleinen Rechenkern (Core) und einem Router. Der Rechenkern enthält einem einfachen Befehlssatz, der Fließkomma-Daten verarbeiten kann, jedoch nicht zur Intel Architecture kompatibel ist. Der Router lenkt die Datenströme zwischen den Kernen und dem Speicher über das im Chip integrierte Netzwerk.

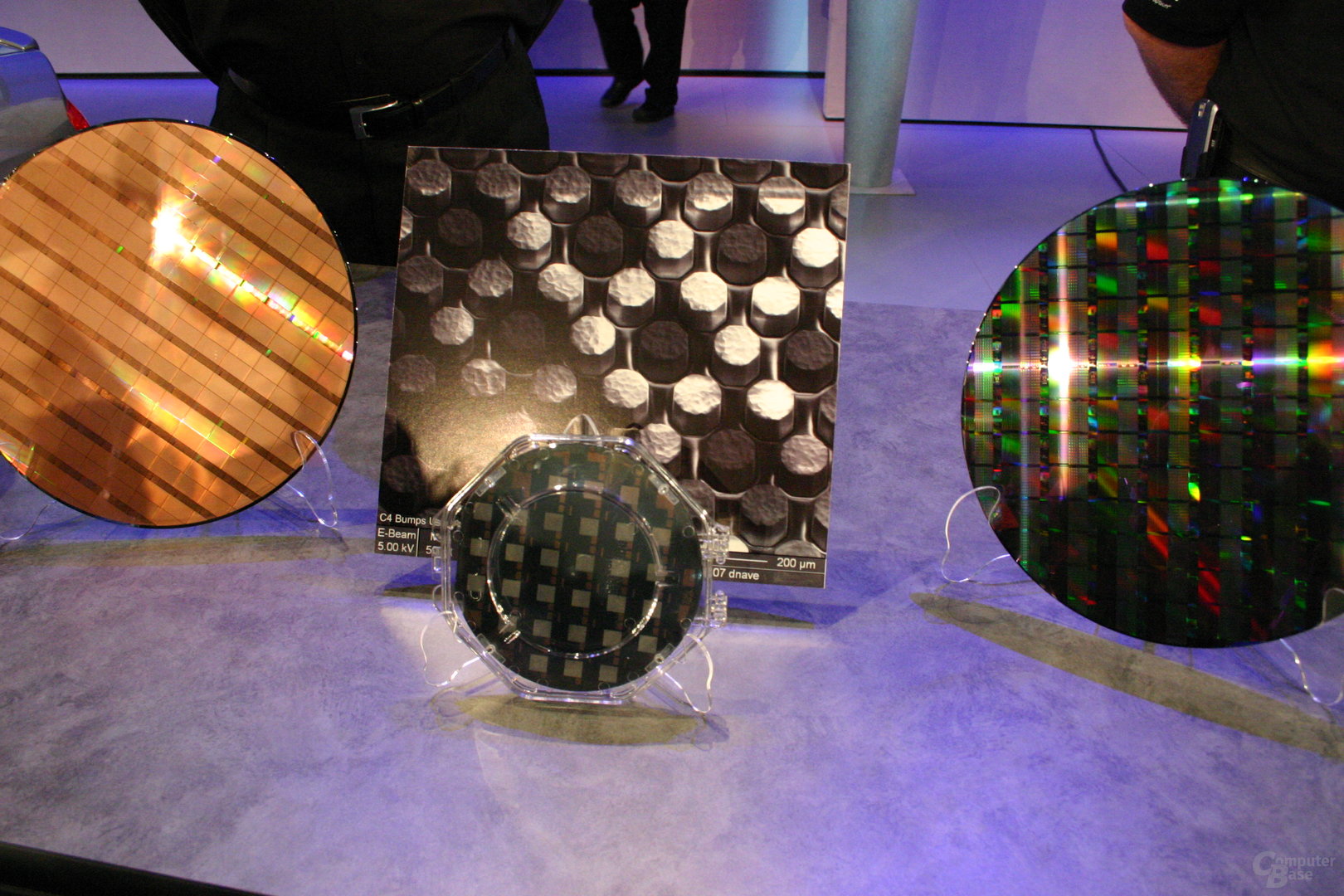

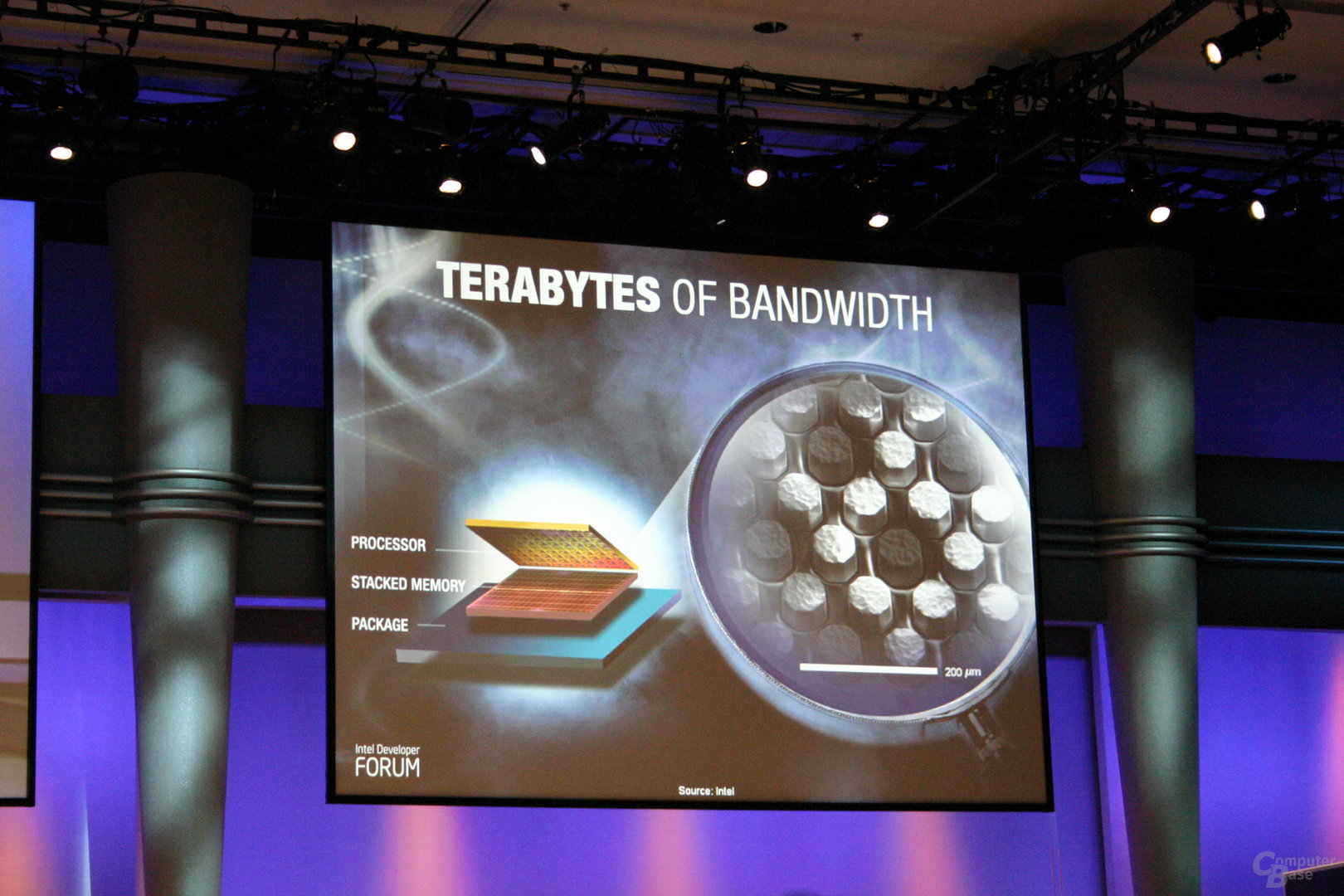

Die zweite maßgebliche Neuentwicklung ist ein SRAM-Speicherchip (SRAM: Static Random Access Memory – statisches RAM) mit einer Kapazität von 20 MB, der sich oberhalb der Prozessoreinheiten befindet (stacked) und über Tausende von Interconnects den Speicher mit den Prozessorkernen verbindet. Damit ergibt sich eine Übertragungsbandbreite von mehr als einem Terabyte pro Sekunde zwischen Speicher und den Prozessoreinheiten.

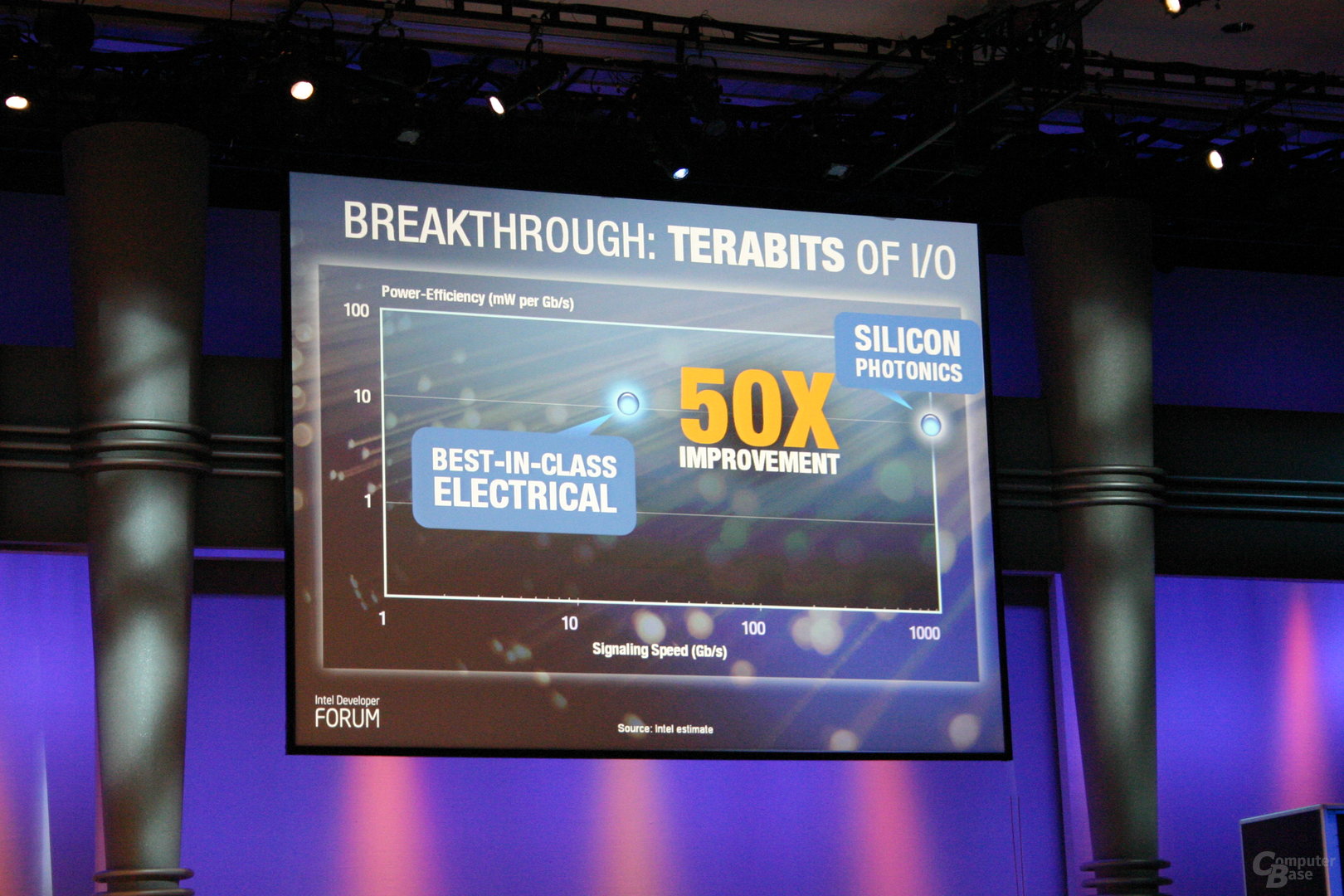

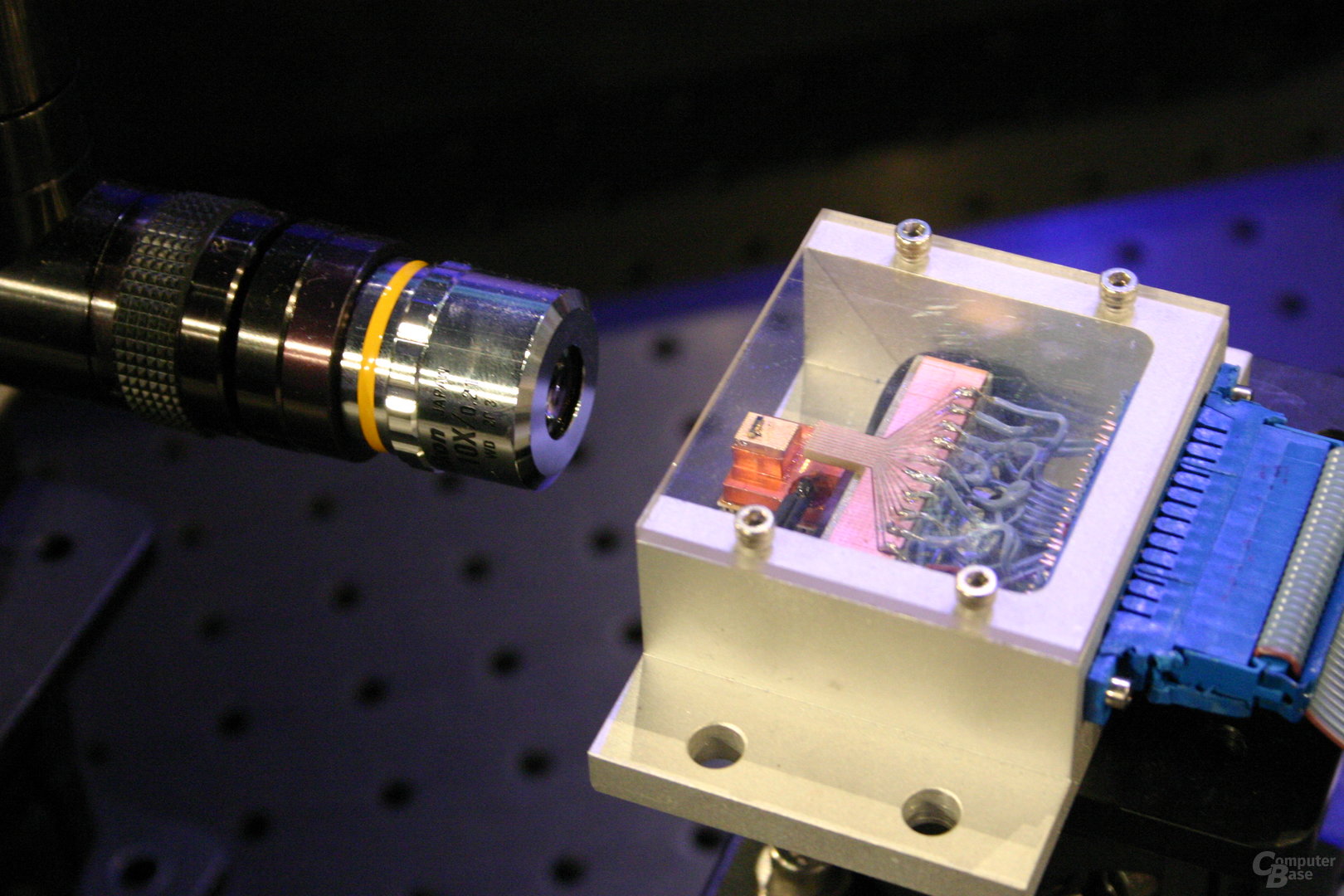

Rattner führte außerdem eine dritte Innovation vor: den kürzlich vorgestellten Hybrid-Silizium-Laser. Dieser Laser-Chip wurde gemeinsam mit Forschern der University of California in Santa Barbara entwickelt. Mit dieser Technologie könnten bis zu mehr als hundert hybrider Silizium-Laser zusammen mit anderen photonischen Silizium-Komponenten auf einem einzigen Silizium-Chip untergebracht werden. Dies könnte eine optische Verbindung ermöglichen, die in einem Geschwindigkeitsbereich von mehreren Terabit pro Sekunde arbeitet. Damit können mehrere Terabyte an Daten zwischen Chips in Computern, zwischen einzelnen Rechnern oder zwischen Servern in Rechenzentren transportiert werden.