IBM: Mit Vakuum zu schnelleren Chips

IBM hat gestern einen technologischen Durchbruch in der Chipherstellung bekannt gegeben. Dem Unternehmen ist es gelungen, einen Prozess aus der Natur nachzubilden und dadurch Billionen kleiner „Luftlöcher“ (Airgaps) auf den Verdrahtungsebenen des Chips (Interconnect-Layers) zu erzeugen.

Im IBM Labor haben Forscher mit dieser Technologie, die als natürlicher Prozess Meeresmuscheln, Schneeflocken oder Zahnschmelz entstehen lässt, bereits bewiesen, dass die elektronischen Signale auf den Chips im Vergleich zu konventionellen Chiptechniken entweder 35 Prozent schneller fließen können oder 15 Prozent weniger Strom verbrauchen.

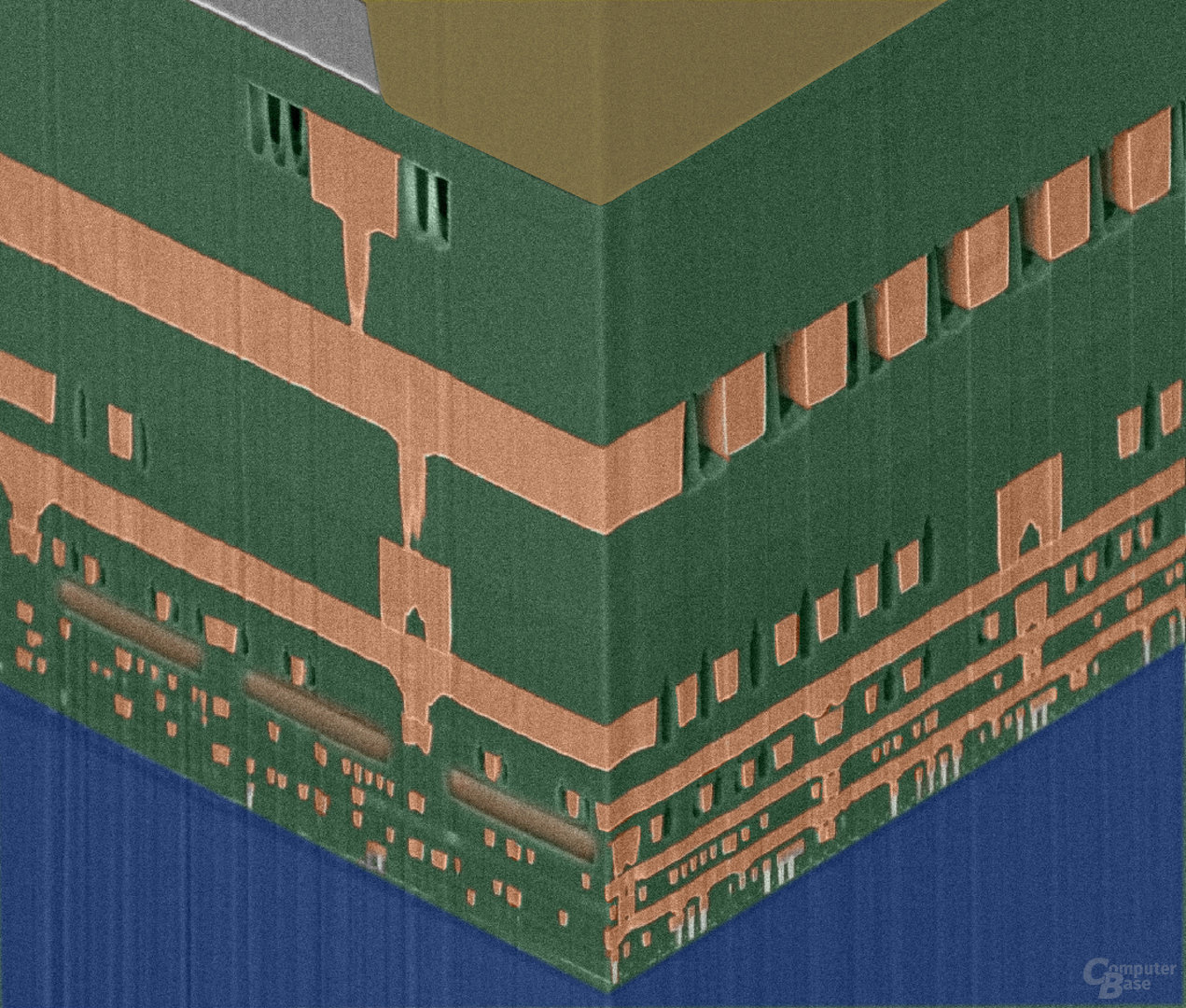

Das von IBM patentierte Selbstanordnungsverfahren (self-assembly process) bringt eine Herstellungsmethode der Nanotechnologie zum ersten Mal in ein kommerzielles Produktionsumfeld. Dieser technologische Fortschritt ermöglicht unter Anwendung konventioneller Herstellungstechnologien eine Leistungsverbesserung der integrierten Schaltkreise, die zwei Generationen des Moorschen Gesetzes, also ca. 48 Monate, entspricht. Diese neue Form der Isolation wird von Wissenschaftlern oft als „Luftloch“ bezeichnet, was eigentlich eine falsche Bezeichnung ist, da die Vakuumlöcher frei von Luft sind. Die von IBM entwickelte Technik lässt ein isolierendes Vakuum zwischen den Kupferdrähten auf den höher gelegenen Verdrahtungsebenen eines Computerchip entstehen, wodurch die elektrischen Signale schneller fließen beziehungsweise dabei weniger Strom verbrauchen.

Ein Vakuum gilt mit einer relativen Dieelektrizitätskonstante von 1 als der beste Isolator, der im Bereich der Leitungskapazität bekannt ist. Bisher gibt es kein besseres Low-k-Material. Dies ist von Bedeutung, wenn zwei Leiter, in diesem Fall die Kupferleitungen auf einem Chip, sich aufgrund ihrer elektrischen Felder beeinflussen und parasitäre Kapazitäten erzeugen. Kapazitäten speichern elektrische Ladungen, die bei einem Schaltungsprozess umgeladen werden müssen. Die Chips werden dadurch verlangsamt.

Die Kupferleitungen auf den Interconnect-Layern werden mit einem Vakuum (Airgap)

gegeneinander isoliert. Besser geht es nach dem aktuellen Physik-Verständnis nicht.

Auf der untersten Ebene sind die Transistoren.

Um die Transistoren des Chips miteinander zu verbinden, verwendet IBM bei seinem 65 nm-Lithographieherstellungsprozess insgesamt zehn darüber liegende Lagen (AMD nutzt elf). In diesen laufen unterschiedliche (Kupfer-)Leitungen mit unterschiedlichen Signalen, die sich ungewollt beeinflussen/ausbremsen. Insbesondere, wenn Signale längere Strecken (global connects) zurücklegen, wächst das Problem mit weiter schrumpfenden Chips (global vs. local delays divergieren auseinander) – das gleichmäßige Verteilen von Signalen wird zum Problem.

Auch Isolatoren mit verbesserter Isolierungskapazität kamen bereits zum Einsatz, doch diese wurden dünn und zerbrechlich – mechanisch instabil -, da die Chipstrukturen immer kleiner und kleiner wurden. Zudem können ihre Isolierungseigenschaften nicht mit denen eines Vakuums verglichen werden. Während man auf den Interconnect-Layers auf der Suche nach besseren Low-K-Materialen ist, geht es dagegen beim Transistor darum, mit High-k-Materialen möglichst hohe Inversionskapazitäten unter dem Gate-Oxid zu erhalten (und damit für schnellere Transistoren mit weniger Leckströmen zu sorgen).

Das Selbstanordnungsverfahren ist bereits in den neuesten IBM Fertigungslinien in East Fishkill, New York, integriert und wird voraussichtlich im Jahr 2009 komplett in die IBM Halbleiterfertigungslinie eingebunden werden. Die Chips werden zunächst in IBM-Server-Produktlinien eingesetzt. Anschließend wird die Technologie auch für Chips angewandt, die IBM für andere Unternehmen fertigt, womit sie später womöglich auch Partnern wie AMD oder Toshiba zur Verfügung steht. Die neue Technologie kann in allen Standard-CMOS-Produktionslinien ohne Unterbrechung oder Anschaffung neuer Geräte eingesetzt werden.

Zur weiteren Klärung hat IBM einige Videos veröffentlicht:

- Das Prinzip der Airgaps

- IBM Senior Vice President John Kelly über Airgaps

- IBM Fellow Dan Edelstein über Airgaps (1)

- IBM Fellow Dan Edelstein über Airgaps (1)

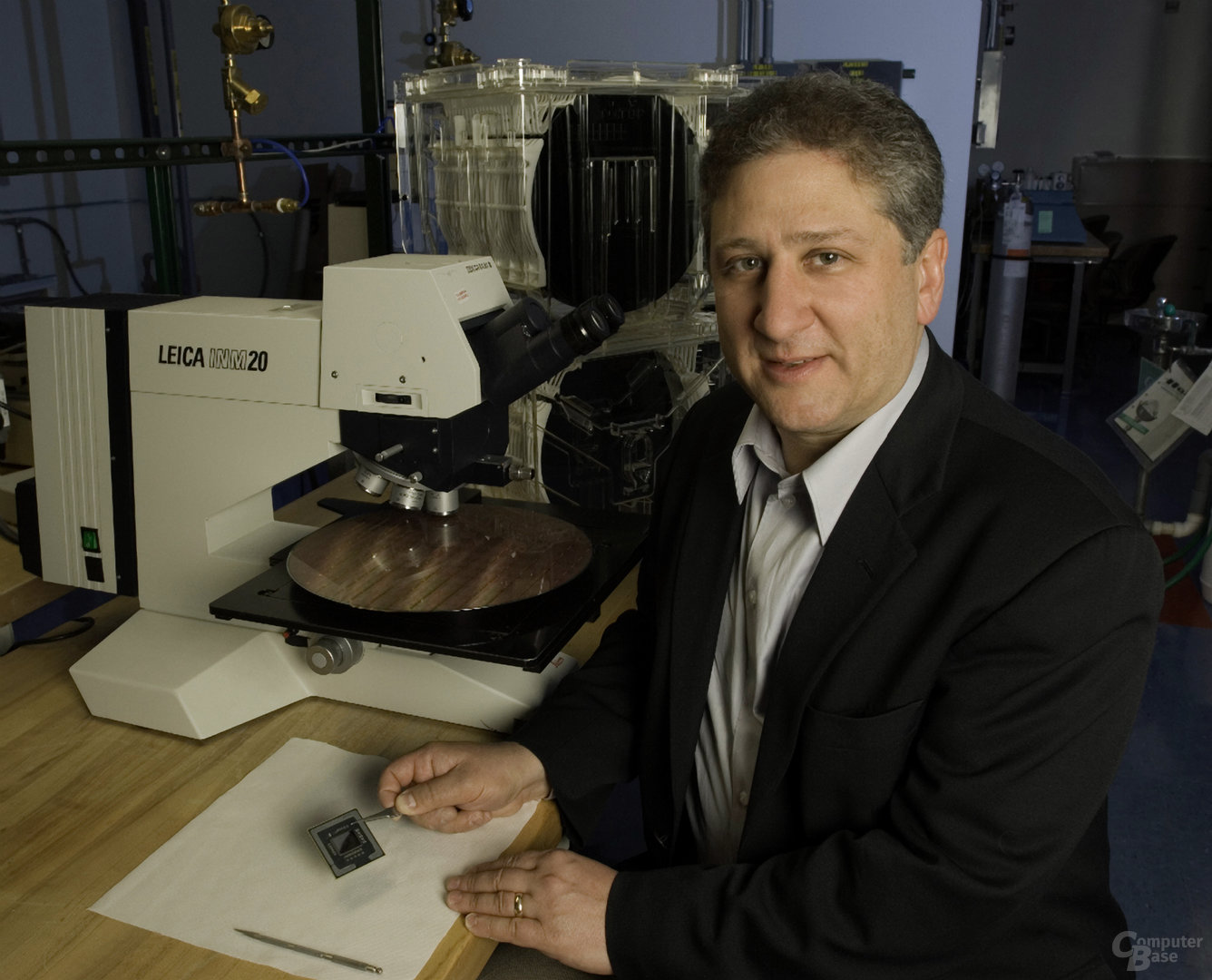

IBM Fellow Dan Edelstein zeigt einen Power 6-Prototypen,

der unter Einsatz von Airgaps hergestellt wurde.