Tile64: Mit 64 Kernen gegen Intel und Co.

Das MIT (Massachusetts Institute of Technology) hat einmal mehr für Aufsehen gesorgt: Ein unter Leitung von Dr. Anant Agarwal an der Universität seit 1996 entwickelter Multicore-Chip soll Intels Prozessoren bei weitem in den Schatten stellen. Hierfür sollen anfangs 64 und später sogar 120 Prozessorkerne sorgen.

Tilera, eine von Dr. Agarwal 2004 gegründete Firma, hat diese Woche ihre Entwicklung offiziell als Produkt vorgestellt. Der Prozessor trägt passend zu seinen Designprinzipien den Namen Tile64. Verglichen mit einem Dual-Core-„Intel Xeon“-Prozessor soll er zehn Mal so schnell und 30 Mal so effizient arbeiten – damit beansprucht er die Performancekrone für sich. Zu dieser wird es vermutlich jedoch nur in Spezialanwendungen reichen.

Die Entwicklung des Tile64 hat 1996 unter dem Codenamen „Raw“ am MIT Laboratory for Computer Science begonnen. Ziel war es, einen Mikroprozessor zu entwickeln, der seine rohe, engl. raw, Hardware dem Compiler zugänglich machen kann ([...] is called Raw because it exposed the raw hardware on a chip – including the wires – to the software compiler. [...]). Nach diesem Prinzip ist bereits 2003 ein Chip mit insgesamt 16 Prozessorkernen entstanden, der mit 120 Mio. Transistoren bei einem 0,15-µm-Fertigungsprozess von IBM die seinerzeit verfügbaren Chips Pentium 4 (Northwood 130 nm: 55 Mio. Transistoren) und Athlon XP (Thoroughbred: 37,2 Mio. Transistoren, Barton: 54,3 Mio. Transistoren) in den Schatten stellte, der dafür mit 225 MHz gegenüber 2 GHz (Intel sogar 3 GHz) im MHz-Rennen jedoch das Nachsehen hatte.

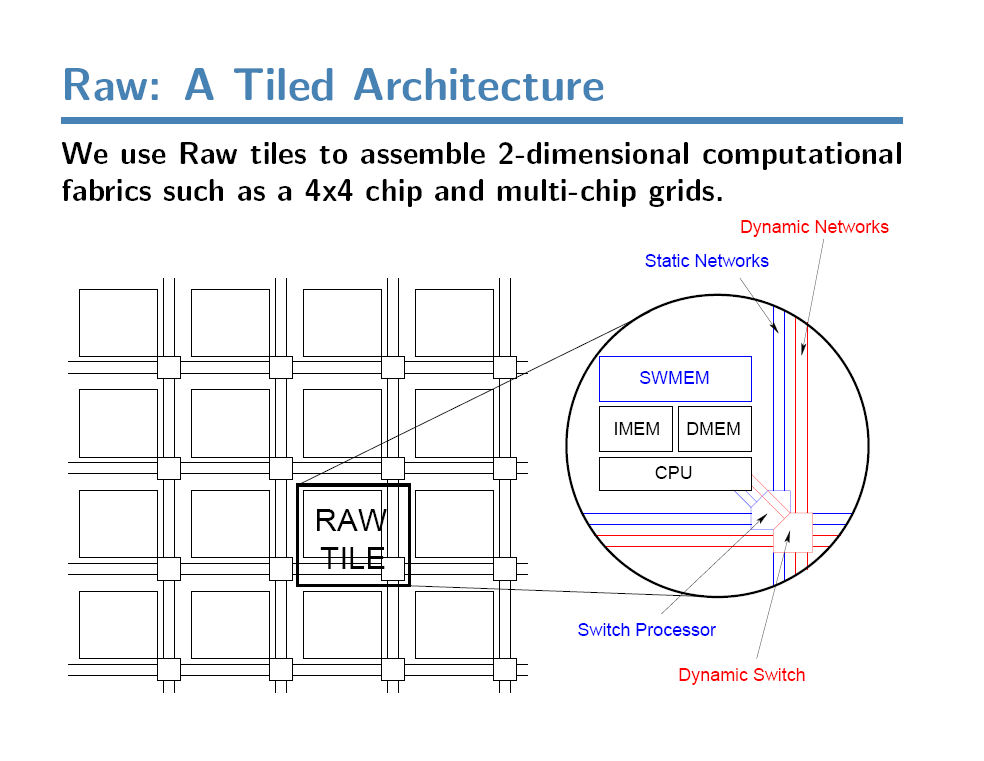

Dem Entwicklungsansatz folgend, können bei Raw die Verbindungen zwischen den einzelnen Kernen per Software gesteuert werden. Dadurch kann zur Programmkompilierung festgelegt werden, welche Rechenknoten wie miteinander verschaltet werden müssen. Mit dem Programmstart passt sich der Prozessor entsprechend an. Der Vorgang scheint vergleichbar mit dem Mapping-Prozess einer Schaltung in einem FPGA, wird im Gegensatz dazu aber nur bis zum Prozessorlevel und nicht dem Logiklevel aufgelöst.

Während sich Tilera über Details des Tile64 noch ausschweigt, kann aufgrund der zahlreichen Publikationen zum Raw-Prozessor davon ausgegangen werden, dass jeder der 64 Kerne die RISC-Architektur (Designansatz) und die MIPS-Microarchitektur (Programmiermodell) implementiert; genauer gesagt den MIPS-I-Befehlssatz des 64-Bit-Prozessors MIPS R4000.

Damit ist klar: Ein Microsoft Windows lässt sich auf Tile64 nicht betreiben, doch das war auch nie die Intention des Chips, denn der IA32-Markt wird ohnehin uneinnehmbar von Intel und AMD dominiert und Startups wie Transmeta haben es schwer Fuß zu fassen oder Probleme wie VIA, Chips auf ähnlichem Performance-Niveau zu bauen. VIA hat sich deshalb in den Nischenmarkt der Low Power Intel Architecture (LPIA) zurückgezogen, den Intel im nächsten Jahr mit Silverthorne und AMD 2009 mit Bobcat aufmischen möchten. Um diesem Kampf zu entrinnen, wählt man besser ein komplett anderes Marktsegment, oder noch sicherer, eine komplett andere Microarchitektur.

Verglichen mit Raw scheint es über die Jahre im nun vorgestellten Tile64 nur Veränderungen im Detail gegeben zu haben. Der ursprünglich 32 kB große L1-Daten- und der 32 kB große L2-Instruction-Cache fallen mit jeweils 8 kB nun wesentlich kleiner aus. Der L2-Cache ist mit 64 kB jedoch unverändert groß. Verglichen mit Quad-Core-Prozessoren wie dem Core 2 Quad und seinem insgesamt 8 MB großen L2-Cache scheint das zwar wenig zu sein, aufgrund der besonderen Cachearchitektur kann Tile64 jedoch mithalten. So besitzt jeder der 64 Kerne, vier Mal mehr als noch bei Raw, diese Menge an Cache. Der L2-Cache ist darüber hinaus so gebaut, dass er über den gesamten Chip hinweg kohärent arbeitet und so von jedem Kern wie ein großer gemeinsamer angesprochen werden kann. Und so sind 64 kB * 64 Kerne mit insgesamt 5 MB L2-Cache schon eine andere Hausnummer.

Ob der in 90 nm gefertigte Tile64 wie Raw eine insgesamt 8-stufige, 1-fachskalare In-Order-Pipeline besitzt, ist nicht klar. Wenn dem so ist, dann wurde vielleicht auch die Floating-Point-Einheit mit ihrer 4-stufigen Pipeline übernommen, mit der FP-Instruktionen in insgesamt 11 Takten, so unsere Vermutung, verarbeitet werden können. Zum Vergleich: Bei Intels Core Mikroarchitektur handelt es sich um eine 14-stufige, 4-fach skalare (4 Instruktionen pro Takt werden verarbeitet) Out-of-Order-Pipeline. Raw besaß je eine ALU, MUL und FPU und könnte diese Menge an Tile64 vererbt haben.

Das Kernstück der kompletten Tile/Raw-Architektur ist die Art und Weise, wie die insgesamt 64 Kerne miteinander verdrahtet wurden. Tilera hat sich für eine Mesh-(Netz)-Struktur entschieden, die man selbst iMesh – intelligent Mesh – nennt und wie sie in ähnlicher Form auch bei Intels 80-Core-Prozessor Polaris zum Einsatz kommt. Jeder Rechenkern wird über einen eigenen Router an das Mesh angeschlossen; ein Block bestehend aus Prozessor, Router und Cache wird als Kachel, engl. tile, bezeichnet. Daher rührt der Name des Prozessors.

Intel setzt bei Polaris auf einen 5-Port-Router, der die vier umliegenden Rechenknoten und als fünftes den Cachespeicher miteinander verbinden soll. Diese Verbindungen sind für ein- und ausgehende Signale jeweils 32 Bit breit. Bei Polaris besitzt jeder Router, wenn er mit 4 GHz taktet, insgesamt eine Bandbreite von 80 GB/s pro Richtung. Beim 4-Port-Router des Raw sind es 32 Bit breite Busse, von den jeweils vier zur Verfügung stehen. An die benachbarten Knoten ist man daher mit 128 Bit (pro Richtung) angebunden. Beim Tile64 kommen ebenfalls 4-Port-Router zum Einsatz, allerdings ist jeder benachbarte Router nun mit fünf 32-Bit-Anbindungen pro Richtung angebunden. Das ergibt eine Bandbreite pro Konten und Richtung von 4-Ports x 32 Bit x 5 Anbindungen x 600 MHz / 8 Bit = 48 GB/s. Taktet der Chip mit 1 GHz, sind es 80 GB/s. Da alle 64 Router eines Tile64 mit ihren Nachbarn kommunizieren können, ergibt sich mit 64 Kerne * 48 GB/s je nach Prozessortakt eine kumulierte Bandbreite zwischen 3 und 5 TB/s.

Inwiefern das ausreicht, um die versprochene Performance zu erreichen, muss abgewartet werden. Die in der Berechnung benutzten Taktraten entsprechen zumindest denen, die Tilera für den Tile64 in Aussicht stellt. Dabei soll jeder der 64 Kerne nur 300 mWatt verbrauchen. Der ganze Chip begnügt sich mit 19,2 Watt, so dass die Behauptung, 30 Mal so effizient wie ein Intel Xeon zu sein, nicht komplett aus der Luft gegriffen ist.

Abgerundet wird das Tile64-Paket mit vier auf dem Chip integrierten DDR2-Speichercontrollern, zwei 10-Gigabit-Ethernet-Schnittstellen (MAC oder PHY), zwei PCI-Express-Controllern Gen 1 mit vier Lanes (MAC oder PHY) und zwei 1-Gigabit-Ethernet-Schnittstellen (MAC). Die Kommunikation mit der Außenwelt scheint damit ähnlich umfangreich wie beim Sun Niagara 2 (UltraSparc T2) sichergestellt zu sein.

Zur Programmierung stehen ein eigener C-Compiler, eine auf Eclipse basierte Programmierumgebung und Support für SMP Linux ab Kernel 2.6 zur Verfügung. Die Kerne lassen sich dabei auch so partitionieren, dass auf ihnen voneinander abgeschottete Betriebssysteme/Anwendungen parallel laufen.

Und wofür das Ganze? Tile64 konkurriert nicht mit klassischen Prozessoren, sondern wird derzeit im Bereich der Netzwerkapplikationen positioniert (wie im übrigen auch Intels Tolapai) und verspricht z. B. HD-Videoencoding mittels H.264 bei 720p und 30 Bildern pro Sekunde für zwei parallele Datenstreams. Speziell hierfür hat Tilera eine PCI-Express-x4-„Netzwerkkarte“ mit bis zu zwölf Gigabit-Ethernet-Ports vorgestellt, die den Namen TILExpress-64 Card trägt und den Tile64 ausreizen soll. Der Prozessor soll auch einzeln verfügbar sein. Bei der Abnahme von 10.000 Stück werden pro Stück 435 US-Dollar fällig.

Tilera hat in Aussicht gestellt, auch Modelle mit 36 und 120 Kernen anzubieten. Weitere Informationen hält die Unternehmenswebseite und noch wesentlich mehr Material die des MIT bereit.