Intel Core 2 Extreme QX9650 im Test: Mit Penryn auf und davon

2/27Überblick

In der Übersicht stellen wir den neuen Core 2 Extreme QX9650 seinen Vorgängern und parallel laufenden Modellen gegenüber. Genauere technische Details zur Architektur und zum Fertigungsprozess folgen auf den kommenden Seiten.

| Merkmale | Core 2 Extreme (Quad-Core) |

Core 2 Quad, Core 2 Extreme (Quad-Core) |

Core 2 Duo, Core 2 Extreme (Dual-Core) |

Core 2 Duo (Dual-Core) |

|---|---|---|---|---|

| Logo |  |

|

|

|

| Codename | Yorkfield (2x Wolfdale) |

Kentsfield (2x Conroe) |

Conroe | Allendale |

| Taktrate oder Modellnummer (Takt in GHz) |

QX9650 (3,00) | Q6600 (2,40) QX6700 (2,66) QX6800 (2,93) QX6850 (3,00)1 |

E6300 (1,86)3 E6320 (1,86) E6400 (2,13)3 E6420 (2,13) E6540 (2,33) E6550 (2,33)1, 4 E6600 (2,4) E6700 (2,66) E6750 (2,66)1, 4 X6800 (2,93) E6850 (3,00)1, 4 |

E4300 (1,80)2, 5 E4400 (2,00)2, 5 E4500 (2,20)2, 5 E4600 (2,40)2, 5 E6300 (1,86) E6400 (2,13) |

| Fertigung | 45 nm | 65 nm | 65 nm | 65 nm |

| Sockel | Sockel 775 | Sockel 775 | Sockel 775 | Sockel 775 |

| Kerne | 4 (MCP) | 4 (MCP) | 2 | 2 |

| Multithreading | X | X | X | X |

| Frontside-Bus | 1333 MHz QDR | 1066 MHz QDR 1333 MHz QDR0 |

1066 MHz QDR 1333 MHz QDR0 |

800 MHz QDR0 1066 MHz QDR |

| Frontside-Bus-Last | 2 | 2 | 1 | 1 |

| Peripherieinterface | Extern | Extern | Extern | Extern |

| Speichercontroller | Extern | Extern | Extern | Extern |

| Transistoren | 2x410 Mio. | 2x291 Mio. | 291 Mio. | 167 Mio. |

| Chipgröße | 2x107 mm² | 2x143 mm² | 143 mm² | 111 mm² |

| L1-Execution-Cache | 2x2x32 kB | 2x2x32 kB | 2x32 kB | 2x32 kB |

| L1-Daten-Cache | 2x2x32 kB | 2x2x32 kB | 2x32 kB | 2x32 kB |

| L2-Cache | 2x6144 kB | 2x4096 kB | 1x2048 kB0 1x4096 kB |

1x2048 kB |

| L2-Anbindung | 256 Bit | 256 Bit | 256 Bit | 256 Bit |

| L2-Modus | L1 inclusive | L1 inclusive | L1 inclusive | L1 inclusive |

| Cache insgesamt | 2x6144 kB | 2x4096 kB | 2048 kB0 4096 kB |

2048 kB |

| Energiesparfunktion | C1E, Enhanced SpeedStep (EIST) |

C1E, Enhanced SpeedStep (EIST) |

C1E, Enhanced SpeedStep (EIST) |

C1E, Enhanced SpeedStep (EIST) |

| Date Execution Prevention (NX-Bit) |

✓ | ✓ | ✓ | ✓ |

| 64-Bit-Technologie | ✓ (EM64T) | ✓ (EM64T) | ✓ (EM64T) | ✓ (EM64T) |

| Virtualisierungs- Technologie |

✓ (Vanderpool) | ✓ (Vanderpool) | ✓ (Vanderpool) | ✓ (Vanderpool)0 |

| CPU-Architektur | 14-stufige Pipeline (Core) |

14-stufige Pipeline (Core) |

14-stufige Pipeline (Core) |

14-stufige Pipeline (Core) |

| Befehlssätze | MMX SSE SSE2 SSE3 SSSE3 SSE4.1 VT |

MMX SSE SSE2 SSE3 SSSE3 VT |

MMX SSE SSE2 SSE3 SSSE3 VT TXT |

MMX SSE SSE2 SSE3 SSSE3 VT |

| 0 Nur bei ausgesuchten Modellen 1 Besitzt einen 1333 MHz schnellen Frontside-Bus 2 Besitzt einen 800 MHz schnellen Frontside-Bus 3 Besitzt 2 MB L2 Cache (Im Silizium sind 4 MB vorhanden, 2 MB sind deaktiviert) 4 Unterstützt Trusted Execution Technology (TXT, ehemals La Grande) 5 Unterstützt keine Virtualisierungstechnologie (VT, ehemals Vanderpool) |

||||

Der Core 2 Extreme QX9650 basiert auf der Penryn-Mikroarchitektur. Hierbei handelt es sich um eine Weiterentwicklung der Core Mikroarchitektur (NGMA, Merom-Mikroarchitektur). Im Rahmen des Tick-Tock-Modells handelt es um ein „Tick“, die als Pioniere einer neuen Fertigungstechnologie (45 nm) dienen und wenig aufwendige Verbesserungen an einer bestehenden Architektur beinhalten. Obwohl die neuen Produkte bis zu 45 Prozent schneller sind – dazu später mehr –, nimmt man dies nicht zum Anlass, um bereits auf „Core 3“ als Produktnamen zu setzen. Diesen Schritt hebt man sich wohl für die wirklich gravierenden Architekturverbesserungen/-änderungen auf, die mit Nehalem, dem nächsten „Tock“ anstehen.

Wurde die „Merom“ Generation noch in Israel entwickelt, findet die Entwicklung von „Penryn“ hauptsächlich in Folsom, Santa Clara und Costa Rica statt. Das Designteam umfasst ca. 150 Mitarbeiter, während das komplette Team aus rund 400 Mitarbeitern besteht. Die beiden Nachfolge-Generationen „Nehalem“ (Tock, 2008) und „Westmere“ (Tick, 2009) werden derzeit in Oregon entwickelt. Die Entwicklung der über übernächsten Generation „Sandy Bridge“ (Tock, 2010) findet hingegen wieder in den Intel Entwicklungsstätten von Isreal statt.

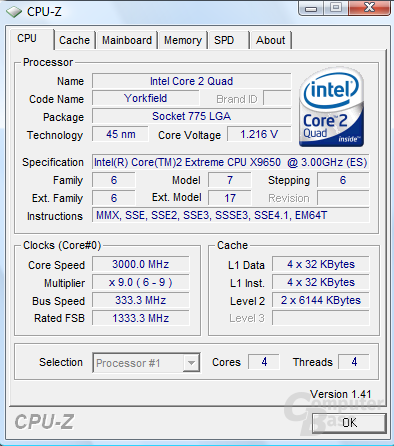

Einen groben Überblick über die neuen Eigenschaften des Intel Core 2 Extreme QX9650 liefert bereits das kleine Tool CPU-Z. Der Prozessor mit dem neuen „Yorkfield“-Kern und einer Thermal Design Power von 130 Watt wird bereits im Stepping „C0“ (Stepping 6) ausgeliefert und der L2-Cache wie erwartet eine Größe von 2x 6 MB. Die Spannung rangiert mit knapp über 1,21 Volt etwa 0,1 – 0,15 Volt unter den bisherigen Core 2 Duo/Extreme Modellen mit 3,0 GHz.

Zu den unterstützten Befehlsätzen gehören erstmals die Streaming SIMD Extensions (SSE) in der Version 4.1. Kein Unterschied besteht in der Ansteuerung des Prozessors mit einem Systemtakt von 333 MHz, welcher wie üblich einen Quad-Pumped-Bus von 1.333 MHz bedeutet. Wie bei den anderen Extreme-Editions von Intel ist auch beim neuen QX9650 der Multiplikator nach oben hin offen. Standardmäßig steht er jedoch auf 9 und erzeugt somit im normalem Zustand die 3,0 GHz Taktfrequenz. Auf Änderungen des Multiplikators und des eingestellten Frontside-Bus kommen wir später im Abschnitt „Übertakten“ zu sprechen.

Ursprünglich sah die Revisions-Planung einen Rhythmus von A0 -> A1 -> B0 -> B1 vor, wovon letztere die finale Revision werden sollte. Im Zuge der letzten Monate hat man sich jedoch gegen die Revision B1 entschieden und stattdessen an der Revision C0 gearbeitet. Dabei gilt: Bei einer Änderung des Buchstaben werden nicht nur die Metallschichten, sondern auch die Siliziumschichten neu erstellt. Ändert sich nur die Zahl, bleibt das Silizium ohne Änderungen. Prinzipiell ist es somit möglich, vorab entsprechend viele Siliziumschichten zu produzieren, um dann mit neueren Metallschichten noch den Produktionsprozess und damit auch das Stepping zu verändern. Offenbar ließ der Zeitplan Intel genug Spielraum, um auch die Silizium-Schichten in letzter Instanz zu verbessern.