IBM, AMD & Co. ab 2009 mit 32-nm-Prozess

Wie IBM nun gemeinsam mit seinen Entwicklungspartnern AMD, Chartered Semiconductor Manufacturing, Freescale, Infineon und Samsung bekannt gab, haben die Unternehmen eine innovative Methode zur schnellen Implementierung ihres 32-nm-Prozesses mit High-K-Dielektrika, Metal Gates und Silicon-On-Insulator-Technologie (SOI) entwickelt.

Basierend auf einem so genannten „High-K Gate-First“-Prozess soll die neue Methode einen einfacheren und schnelleren Weg zum Wechsel auf 32nm und „High-K/Metal Gate“-Technologie eröffnen. Im Rahmen der Siliziumplanartechnologie wird das Gate standardmäßig als erstes platziert (Gate-First). Anhand der Gate-Position können Source und Drain ohne weiteres korrekt platziert werden (self-alignment). Das Problem: die Dotierung der Source/Drain-Gebiete erfolgt bei Temperaturen, die zwar dem bisher genutzten Polysilizium-Gate nichts aus machen, einem Metal Gate jedoch Probleme bereiten. Intel musste deshalb bei seiner im Penryn/Yorkfield eingesetzten 45-nm-Technologie (P1266) auf eine Gate-Last Herstellung umschwenken. IBM ist es anscheinend gelungen, dieses Problem zu umgehen.

Die Bandbreite entsprechender 32-nm-Produkte soll von Chips für mobile Geräte bis hin zu ausgewachsenen Server-Prozessoren, wie zum Beispiel jenen aus IBMs Power-Serie, reichen. Verläuft alles nach Plan, soll der 32-nm-Prozess ab der zweiten Jahreshälfte 2009 einsatzbereit sein. Konkurrent Intel plant ebenfalls für Ende 2009 den Wechsel auf 32nm.

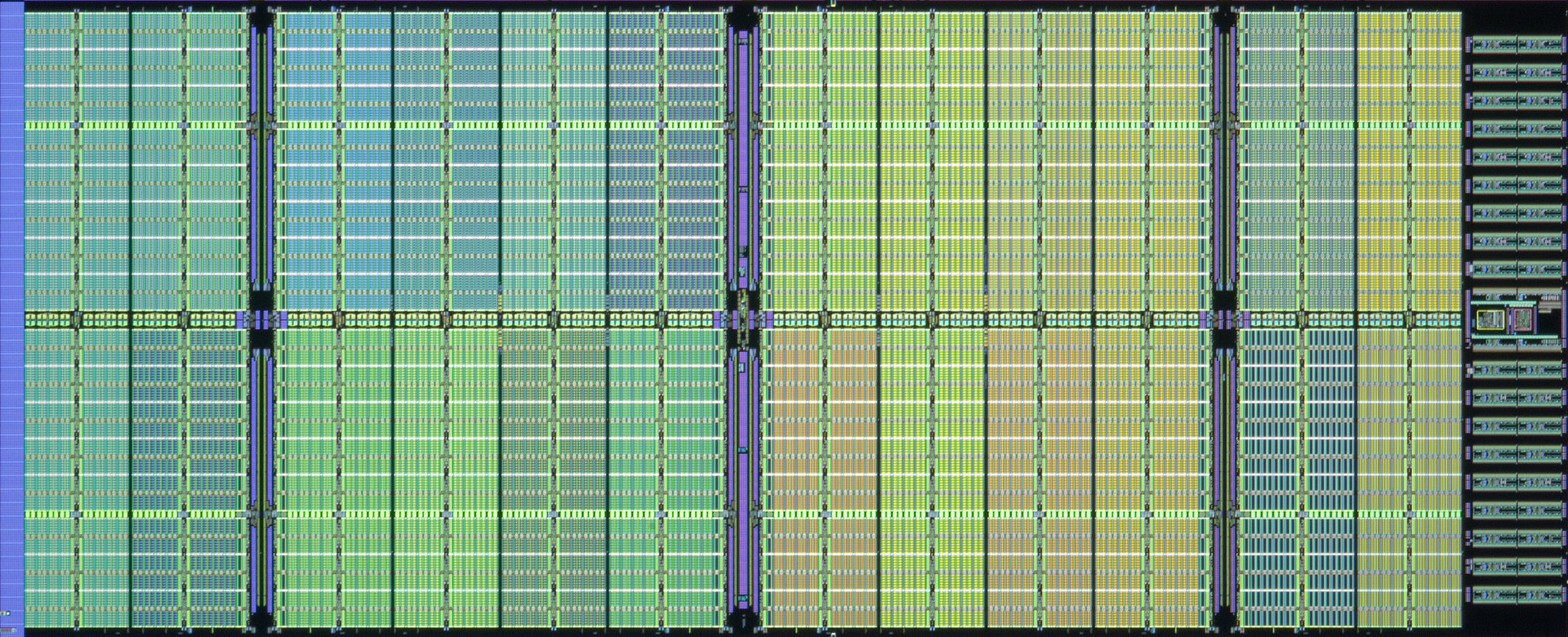

32-nm-SRAM-Testchip mit High-K/Metal Gate und SOI von IBM

Gegenüber der vorherigen Technologiegeneration in 45 nm Strukturbreite, die im Januar vorgestellt wurde und erst im kommenden Jahr in der Fertigung Einzug halten soll, soll der Schrumpffaktor der Chips bei bis zu 50 Prozent – dem Idealwert – liegen. Durch die „High-K/Metal Gate“-Technologie erhofft man sich im Betrieb rund 45 Prozent Energieeinsparung. Außerdem wird IBM auf Airgap vertrauen (Vakuums auf den Interconnect-Layers), mit dem das RC-Delay erheblich reduziert werden kann.

Für die Performance von Prozessoren soll dies Luft für Steigerungen um bis zu 30 Prozent bieten. Als Demonstrationsobjekt für den 32-nm-Prozess diente, wie üblich, eine im neuen Prozess gefertigte SRAM-Zelle. Deren Größe liegt dank der neuen Fertigungstechnologie unterhalb von 0,15 µm². Zum Vergleich: Intel hat bei seinem 32-nm-Prozess (P1268) 0,182 µm² wesentlich größere Zellen präsentiert.