IBM stellt Prozessormonster mit 20 Cores vor

Abseits der bekannten Prozessorarchitekturen von AMD und Intel hat IBM im Rahmen der Vorstellung der neuen „System z10“ Großrechner-(Mainframe)-Produktfamilie einmal mehr ein Prozessormonster geschaffen, das alles bisher Dagewesene in den Schatten stellt.

Zwischen den allgemein bekannten Servern, die üblicher Weise auf x86-Architektur (AMD/Intel) setzen, vereinzelt jedoch auch mit SPARC (Sun) oder Power (IBM) ausgestattet sind, und den in den Medien immer wieder gerne behandelten Supercomputern, die wissenschaftliche Simulationen durchführen, befindet sich in der Mitte die Gruppe der Großrechner (Mainframes), die hauptsächlich von der IBM System/360-Architektur abgedeckt werden. Auch IBM Power sowie Intel EPIC (Itanium) zielen auf diese „Mission Critical“-Märkte ab.

Bei Großrechnern läuft die komplette Unternehmenskommunikation zusammen. Vor dem Aufkommen der PCs dienten sie als Terminal Server; heute werden sie hauptsächlich für datenintensive Aufgaben (mit viel Input/Output) wie Datenverarbeitung, Ordner Entry, Logistik, Finanzprogramme und Customer Relationship Management (CRM) eingesetzt. Es sind die Art von Servern, die z.B. bei der Lufthansa das komplette Buchungssystem (derzeit HP Superdome mit Itanium 2) tragen. Ausfälle werden hier nicht geduldet. Dementsprechend können bei allen Großrechnern im laufenden Betrieb Festplatte, Arbeitsspeicher und selbst Prozessoren getauscht werden. Redundanz und Ausfallsicherheit werden groß geschrieben – die Schlagworte lauten Reliability, Availability und Serviceability (RAS).

Soweit zur Einordnung der im Folgenden vorgestellten z10 Prozessoreinheit. Es sei darauf hingewiesen, dass Intel mit seiner Itanium-Familie auf den selben Markt abzielt, nur mit dem feinen Unterschied, dass der derzeit schnellste Itanium (9150M) günstiger ist, als das beim z10 eingesetzte Prozessorgehäuse (Package) allein.

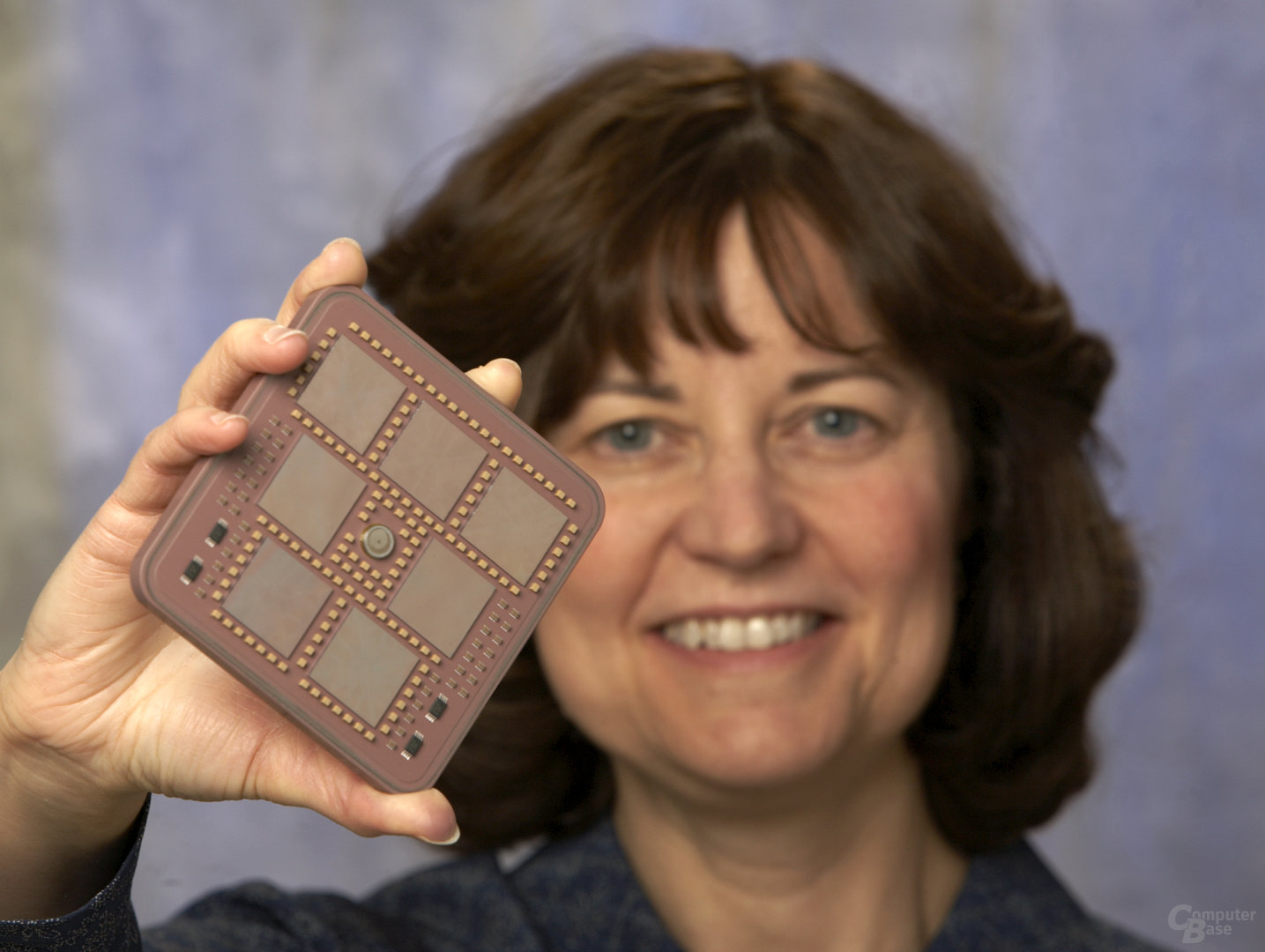

Das z10 ist in so genannte Books unterteilt (vergleichbar mit einem Blade). Jedes Book besitzt einen Prozessorsockel, verfügt über Arbeitsspeicher, entsprechende Peripherie und Kühlung. Der Prozessorsockel - ein Wunderwerk moderner Technik – besteht aus 7356 LGA-Kontakten (vgl. AMD Sockel F 1207 bzw. Intel Sockel T 775 Kontaktflächen) und ist das mechanische Gegenstück zum Prozessorpackage, dem Multi-Chip Module (MCM), auf dem IBM 20 Prozessorkerne untergebracht hat. Das MCM hat eine Größe von 96 x 96 mm, besteht aus 103 Verdrahtungslayern (Glass Ceramic Layers) und beherbergt fünf Prozessor- und zwei Cachechips (Storage Control, SC), die in der Summe beeindruckende 8 Mrd. Transistoren auf die Waage bringen.

Jeder der fünf Prozessorchips auf dem MCM basiert auf einem monolithischen (nativen) Quad-Core, der aus 994 Mio. Transistoren (465,1 mm²) besteht und in 65 nm mit 10-Interconnect-Layers gefertigt wird. Jeder Kern (Processing Unit, PU) taktet mit 4,4 GHz und implementiert die z/Architecture (CISC) und arbeitet 2-fach-skalar In-Order. Die PUs unterstützten 894 Befehle; 668 von ihnen wurden komplett in Hardware (wahrscheinlich ohne Microcode) umgesetzt. Mit dem z10 sind 50 neue Befehle hinzugekommen. Die Prozessoren wurden zwar in Zusammenarbeit mit dem IBM Power6-Team entwickelt und ähneln sich daher in den Execution und Floating Point Units, der Core Pipeline, der In-Order-Ausführung und anderen Bereichen. Sie unterschieden sich jedoch grundlegend in der implementieren Architektur. Schließlich verfolgt Power den Ansatz von RISC.

Jede PU besitzt erstmalig eine Decimal Floating Point Unit (HDFU) und unterstützt damit die im neuen IEEE754r-Standard beschriebene Dezimal-Floating-Point-Arithmetic, die von Banken gefordert wurde. Augenscheinlich handelt es sich hierbei weltweit um den ersten Prozessor, der diesen Standard implementiert. Jeder Core hat einen 192 kB großen L1-Cache (128 kB Data, 64 kB Instruction) und einen 3 MB großen L1.5-Cache. Auf einem Prozessorchip sind somit 12 MB (4x3 MB) Cache vorhanden. Ebenfalls Teil des 994 Mio. Transistoren starken Chips sind insgesamt zwei Coprozessoren (COP) für beschleunigte Datenkompression und Kryptographie.

Die fünf Prozessorchips auf einem MCM stellen somit insgesamt 20 Rechenkerne und 60 MB L1.5-Cache. Doch es gibt noch mehr: Das MCM hat zwei Storage Control Chips die jeweils 1,6 Mrd. Transistoren (458,3 mm²) besitzen und einen jeweils 24 MB großen L2-Cache zur Verfügung stellen. Mit insgesamt 48 MB L2-Cache stellt es Intels Itanium in den Schatten und wird nur von einem alten Power5-Kollegen aus selbem Hause überboten. Bei all diesen Eckdaten verwundert es nicht weiter, dass jedes MCM-Modul mittels Wasserkühlung auf akzeptablen Temperaturen gehalten wird.

IBM gibt an, dass ein z10-System mit insgesamt 64 Prozessoren (4 Books zu 3x20 und 1x17 PUs) die Leistung von insgesamt 1500 x86-Servern aufbringt und dabei 85 Prozent weniger Strom und 85 Prozent weniger Fläche belegt. Preise liegen uns nicht vor. Der minimale Speicherausbau liegt bei 16 GB; maximal sind 1,5 TB möglich. Auch der Stromverbrauch kann sich sehen lassen: zwischen 10 und 27,5 kW werden hier fällig. Der z10 lässt AMD und Intel wie Amateure erscheinen und zeigt eindrucksvoll, was möglich ist, wenn Geld keine Rolle spielt.

Und nein, Windows wird vom z10 nicht unterstützt.

Bereits der 2007 vorgestellte Power6 hat Support für Floating Point Dezimal Arithmetic geboten.