SSE-Nachfolger heißt AVX und ist 256 Bit breit

AMDs sehr frühzeitige Ankündigung von SSE5 hat Intel zu einer überraschenden Bekanntgabe der geplanten Instruction-Set-Erweiterung für Sandy Bridge (ehemals Gesher) verleitet. Das Ganze trägt den Namen AVX und soll (Ende) 2010 Einzug halten.

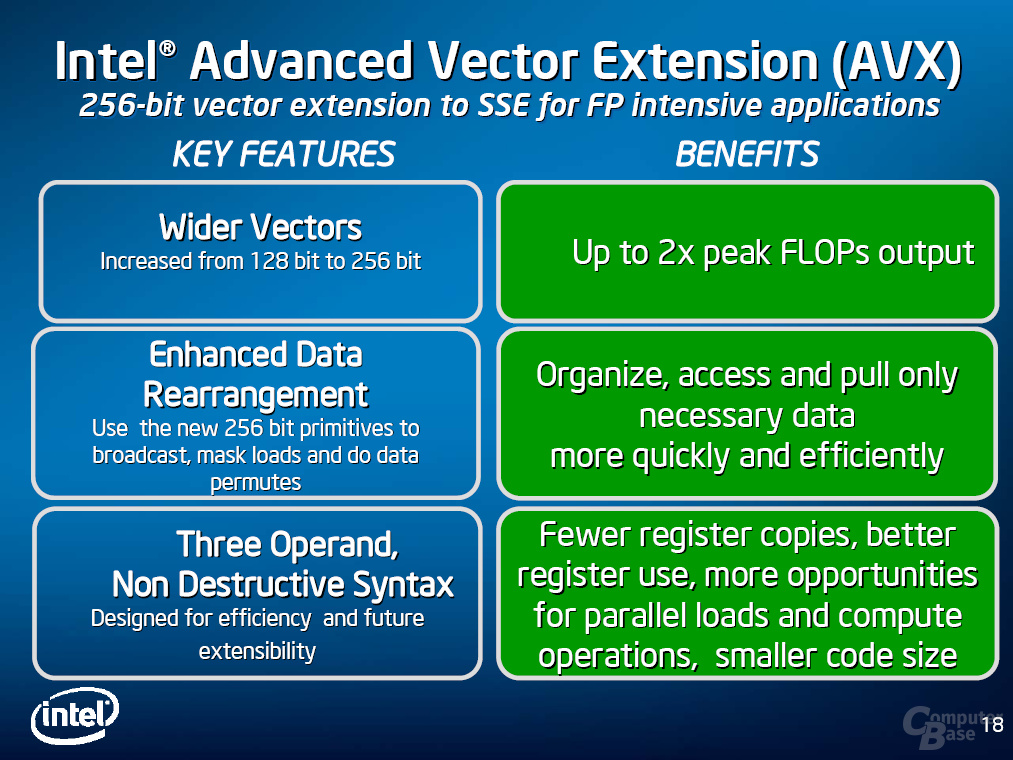

AVX steht für Advanced Vector Extension. Diese neuen Befehle arbeiten auf 256-Bit-Operanden und sind im Vergleich zu SSE damit doppelt so breit. Durch diese Verdopplung kann der SSE-Nachfolger insbesondere bei Gleitkommaoperationen (Floating Point) punkten: Bei einfacher Genauigkeit (Single Precision, SP, 32 Bit) wird mit einem Befehl die selbe Operation vier mal parallel ausgeführt (Single Instruction Multiple Date). Mit AVX können mit einem Befehl (z. B. einem Addiere) acht Ergebnisse gleichzeitig berechnet werden. Unter Verwendung von doppelter Genauigkeit (Double Precision, DP, 64 Bit) wurde der Durchsatz von zwei auf vier gesteigert.

Interessant ist auch, dass Intel mit AVX von dem bisherigen 2-Address-System abweicht. Eine der zwei Datenquellen (Source) und Datenziel (Destination) müssen nicht länger ein und das selbe Register bzw. die selbe Speicheradresse sein. Wie bei RISC-Architekturen üblich, ist AVX triadisch, bekommt also drei Operanden (Direktoperand, Speicheradresse oder Register) übergeben. Besonders Algorithmen, die ein und das selbe Quellregister mehrmals zur Berechnung verwenden, sollten hiervon profitieren. Schließlich wird mit AVX keine der zwei Quellen bei der Operation konsumiert.

AMDs SSE5 wird zusammen mit dem Bulldozer-Kern an den Start gehen. Dieser Prozessor kommt unter anderem im Sandtiger-Chip zum Einsatz, der nach einer Aktualisierung der Roadmap nun ebenfalls 2010 erwartet wird. Ob SSE5 und AVX langfristig parallel existieren werden, oder AMD durch seine frühe Ankündigung bereits wichtige Kunden vom eigenen ISA überzeugen (und damit von AVX abhalten) konnte, muss die Zukunft zeigen.

Intel plant Anfang April 2008 im Rahmen des IDF in Shanghai die Befehlsliste von AVX bekannt zu geben.