TLB-Bug im Intel Core i7! – Oder doch nicht?

Seit dem frühen Montag Morgen stiftet eine Meldung im Internet mehr Verwirrung, als dass sie Klarheiten schafft. Dabei ist unter anderem die Rede von einem TLB-Bug, der noch schlimmere Züge annehmen soll, als dies beim ersten Phenom-Prozessor der Fall war. Wir haben bei Intel nachgefragt.

Der Grund für die voreiligen Berichterstattungen so manches Online-Mediums war ein Eintrag in einem Specifications Update zu den Core i7. Wie üblich sind die Aussagen in diesem Dokument sehr kurz gehalten, seit Jahren beinhalten sie auch eine Liste der Errata, der Fehler in den Prozessoren. Dabei geht es meist um Probleme, die unter sehr bestimmten Gegebenheiten auftreten können, was in der Praxis aber fast nie der Fall ist. Datiert ist dieses Dokument auf den 12. November 2008, also bereits fünf Tage vor den 17. November 2008, an dem der Intel Core i7 offiziell vorgestellt wurde. Auch wurde das Dokument bereits von diversen Seiten genauer betrachtet, wie nicht zuletzt ein Bericht von heise online vom besagten Tage beweist. Dieser Punkt sorgt insofern für zusätzliche Verwirrung, weil in dubiosen englisch-sprachigen Foren und selbst bei einigen Internet-Präsenzen das Dokument als völlig neu verkauft wird.

Da jedoch der Name „TLB“ in dieser Errata-Liste von Intel auftaucht, ist die (Online-)Welt aufgeschreckt und fühlt sich sogleich an das Phenom-Desaster des letzten Jahres erinnert. Ein Fehler in der Speicherverwaltung des Prozessors sorgte damals dafür, dass theoretisch Datenverluste auftreten konnten. Traditionell wird in einem Prozessor jede angeforderte virtuelle Adresse zuerst durch die „Memory Management Unit“ (MMU) in eine physische Adresse umgerechnet, bevor sie auf den Adressbus geschrieben wird. Die MMU verfügt über speziellen Cache-Speicher, den Translation Lookaside Buffer (TLB), welcher jeweils die letzten Adressübersetzungen in Form einer Tabelle abspeichert. Dabei wird die virtuelle (logische) Adresse in mehreren Arbeitsschritten zu einer meist baumartig organisierten Seitentabelle zur physischen Adresse umgerechnet. Dieser zeitintensive Vorgang wird aus Performancegründen im TLB gepuffert. Der TLB kann eine begrenzte Menge dieser Einträge halten und dadurch die Ausführung von Speicherzugriffen deutlich beschleunigen. Durch den Fehler „298“ in diesem Bereich sah sich AMD gezwungen, Teile davon komplett zu deaktivieren – der sogenannte TLB-Fix war geboren. Auch wenn dieser Fehler laut AMD in der Praxis nie auftrat, hatte der Fix fatale Folgen für den ersten Vier-Kern-Prozessor von AMD, vor allem auch im Bereich der Desktop-Prozessoren: massive Performanceeinbrüche. Die Server-CPUs wurden gar auf Eis gelegt und eine Auslieferung erst mit dem neuen B3-Stepping gestartet.

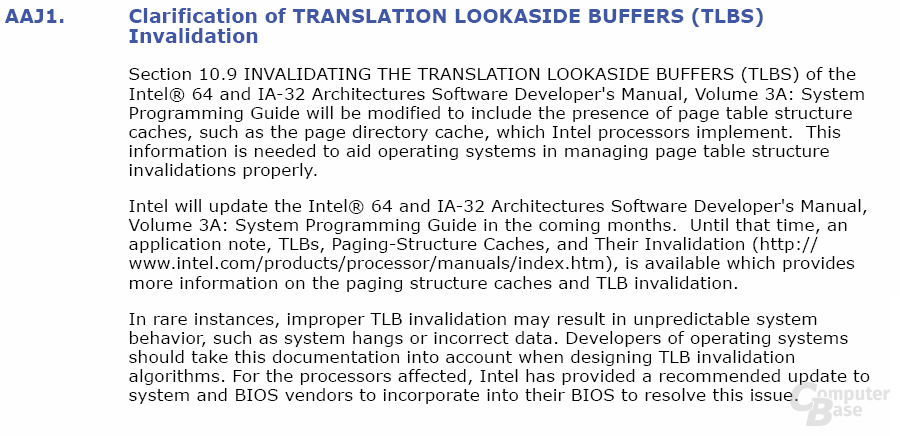

In den Specifications Updates von Intel ist auf dem Papier von ähnlichen Problemen zu lesen, die AMD vor einem Jahr mit dem „Barcelona“ hatte. Dabei spricht Intel davon, dass in seltenen Fällen die unsachgemäße Annullierung von TLB-Einträgen zu einem unvorhersehbaren Verhalten des PCs führt, was zu Systeminstabilitäten und Datenverlusten führen kann. Weiter besagt jenes Dokument in einer separaten Erklärung zu dem ersten Errata in dem Dokument aber auch, dass der Effekt nur auftreten kann, wenn eine Software selbst Einträge im TLB annulliert. In diesem Punkt liegt der Hund jedoch auch begraben. Bereits seit der Pentium-6- respektive Pentium-Pro-Familie wird auf Dinge dieser Art und Probleme mit dem TLB hingewiesen (Intel 64 and IA-32 Architectures Software Developer's Manual Volume 3A: System Programming Guide, 8,90 MB PDF-Dokument). Auch die Core 2 Duo hatten diese Art der „TLB Invalidation“, was Intel in vielen technischen Dokumenten, die auf der Internetseite bereitstehen, näher erklärt. Genau dieses Vorgehen der älteren Core-Prozessoren empfiehlt der Prozessorriese aktuell auch beim Core i7.

Eine bereits am Vormittag angefragte Stellungnahme zu diesem Thema von Intel blieb bis zum späten Abend aus. Die Kollegen der Presseabteilung in Deutschland müssten sich erst mit den Technikern, Ingenieuren und Pressevertretern in den USA in Verbindung setzen, um weitere, vor allem genauere Informationen zu erhalten, so Intel Deutschland gegenüber ComputerBase. Ob der Core i7 derzeit also vielleicht bereits zu langsam arbeitet, oder andererseits wie damals bei AMD noch künstlich eingebremst werden muss, oder letztendlich wie beim Core 2 Duo und den älteren Prozessoren einfach gar nichts passiert, wird die Antwort von Intel zeigen.

Während Intel Deutschland noch keine Informationen herausgegeben hat, haben die Kollegen vom TechReport ein Statement vom Intel-PR-Manager Dan Snyder. Demnach seien die Probleme angeblich bereits vor dem Start des Core i7 mit einem BIOS-Update behoben. Schuld an der Verwirrung ist die teilweise veraltete Beschreibung, die bereits in den letzten Jahren bei jedem Prozessor immer wieder mitgenommen wurde. Dies haben auch wir bereits gestern beim Begutachten mehrerer Dokumente festgestellt. Bei so gut wie allen Prozessoren von Intel ist jener TLB-Bug gleich als erstes aufgeführt (Beispiel Celeron-200-Serie, Seite 53, PDF-Dokument). Deshalb lautet das Statement wie folgt:

The "AAJ1 Clarification of TRANSLATION LOOKASIDE BUFFERS" document is a SPEC CLARIFICATION, and is simply a pointer to a previous document written in April 2007.

SPEC CLARIFICATION AAJ1 was initially added due to an issue on the Intel® Core 2 Duo processor which was previously corrected with a BIOS update; this issue does not impact the Nehalem Family of CPUs. There are errata on the Intel Core i7 processor that relate to the TLB. These all relate to improper translations or error reporting, and all of those that impact functionality have been fixed via BIOS updates prior to Core i7 launch.

Intel PR Manager Dan Snyder

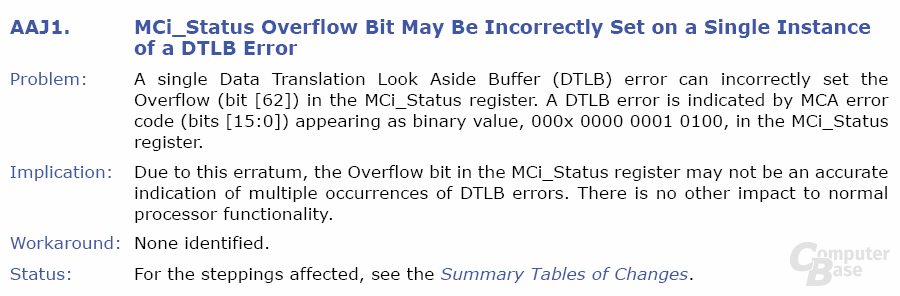

Nach einem längeren Telefonat mit Intel Deutschland am Dienstag Nachmittag konnte der Hersteller gegenüber ComputerBase noch einige Dinge klarstellen. Dabei ging es nicht nur um den einen Fehler, der seit (vor-)gestern richtig publik gemacht wurde, sondern auch um die anderen Errata, die sich um den Translation Lookaside Buffer drehen, was bereits ein findiger Boardie aus Forum von Planet3DNow! beim Stöbern durch die bereitgestellten Dokumente festgestellt hatten. Der Core i7 hat nämlich nicht nur einen (TLB-)Bug, sondern derer gleich vier: AAJ1, AAJ42, AAJ54 und AAJ59. Der erste Fehler und seit zwei Tagen massiv in der Presse vertretene Bug ist in erster Linie schlichtweg ein Hinweis für Softwareentwickler und Programmierer und hat für den Kunden laut Intel keine Relevanz. Die drei weiteren Probleme sollen angeblich bereits alle mit einem entsprechenden BIOS gefixed worden sein.

Auf die Frage hin, ob alle BIOS-Programmierer der unterschiedlichen Boardpartner den Fix jedoch bereits umgesetzt haben, geht Intel einfach davon aus, dass dies bereits geschehen ist, da man eng mit allen Firmen zusammenarbeite. Dennoch könnten bei den frühen Testsamples und entsprechenden Beta-BIOS-Versionen kleinere Abweichungen aufgetreten sein. Davon ist mitunter sogar Intels eigenes Board betroffen gewesen. Dies könnte unter anderem auch die diversen neuen BIOS-Versionen beim Test des Core i7 bei uns erklären, als wir uns nach einem kleineren Test für eine Platine von Asus und gegen das Referenzboard von Intel entschieden. Dort kamen in vier Wochen nicht weniger als fünf neue BIOS-Versionen auf den Markt, im Test war das Mainboard von Asus gegenüber dem Intel SmackOver aber gerade einmal ein Prozent schneller – egal bei welchem BIOS. Aktuell ist das BIOS beim Asus P6T nur noch eine Version gegenüber der von uns getesteten Version fortgeschritten, so dass man davon ausgehen kann, dass jene Errata längst gefixed sind. Laut Intel sind eigentlich überhaupt keine Performanceänderungen durch die BIOS-Updates, die die Errata betreffen, zu beobachten, so dass man diese Unterschiede in unserem Test auch weiterhin auf die unterschiedlichen Platinen schieben kann. Von Intel wurde nach eigenen Angaben alles getan, damit vor dem Start der Core i7 im Handel die Probleme aus der Welt geschafft sind.