ISSCC: Wenig Neues zu AMDs „Bulldozer“

Auf der seit einigen Tagen laufenden International Solid-State Circuits Conference 2011 (ISSCC) hat AMD, wie im Vorfeld angekündigt, auch über die neue CPU-Architektur „Bulldozer“ gesprochen. Im eigenen Blog gibt das Unternehmen nun einige, wenige Details zu „Bulldozer“ preis, die größtenteils jedoch schon bekannt sind.

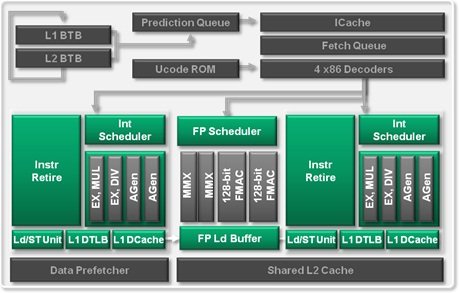

Bekanntlich wird die „Bulldozer“-Architektur radikale Änderungen zu vorherigen CPU-Designs mit sich bringen. Den Kern bildet dabei der Aufbau mit sogenannten Modulen, die zwei Integer-Kerne mit einer flexiblen Gleitkomma-Einheit (FPU) – von AMD „FlexFP“ getauft – beinhalten. Die Funktionsweise der Ausführungseinheiten eines solchen Moduls veranschaulicht AMD nun anhand einer neuen Grafik, die gegenüber bisher veröffentlichten Schemata etwas weiter ins Detail geht und zum Beispiel die einzelnen Aufgaben der je vier Integer-Pipelines beschreibt, allerdings keine wirklich neuen Erkenntnisse offenbart.

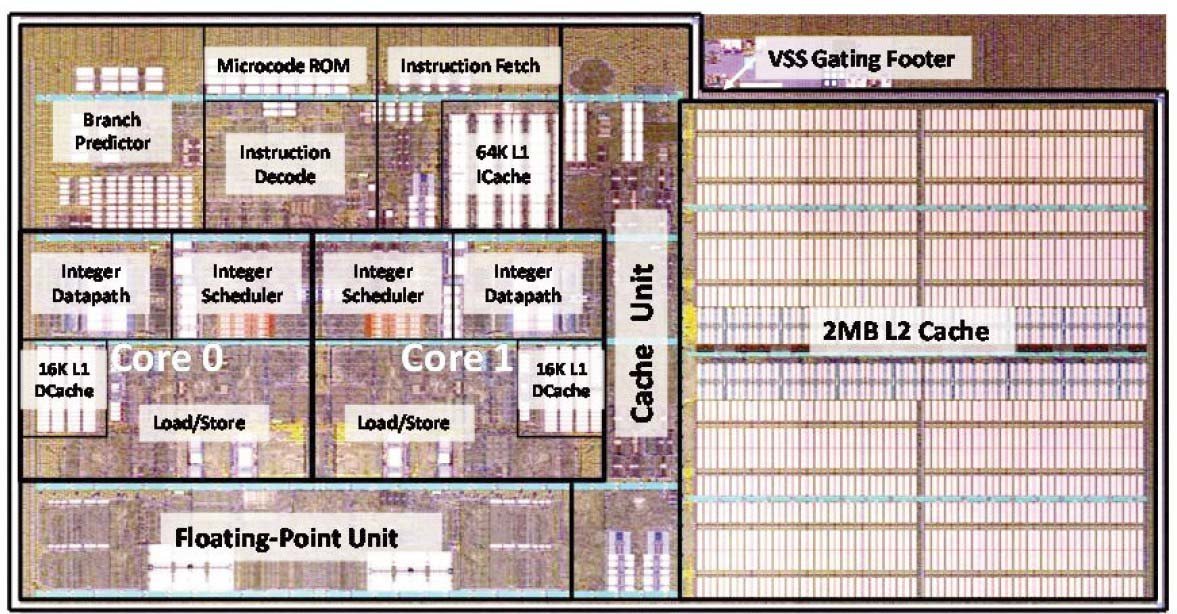

Eine Integer-Einheit verfügt nun im Vergleich zur Vorgängergeneration über vier statt drei Pipelines und kann somit mehr Befehle gleichzeitig abarbeiten. Während jeder dieser Integer-Kerne einen eigenen L1-Cache für Daten (16 KB) besitzt, müssen sie sich den L1-Cache für Befehle (64 KB) sowie den pro Modul 2 MB großen L2-Cache teilen. Bei AMDs aktuellen 45-nm-Prozessoren ist hingegen jedem Kern ein separater L2-Cache (512/1.024 KB) zugeteilt. Den bis zu 8 MB fassenden L3-Cache eines „Bulldozer“-Die müssen sich wiederum die Module (bis zu vier pro Die) und somit alle Kerne (bis zu acht pro Die) untereinander teilen.

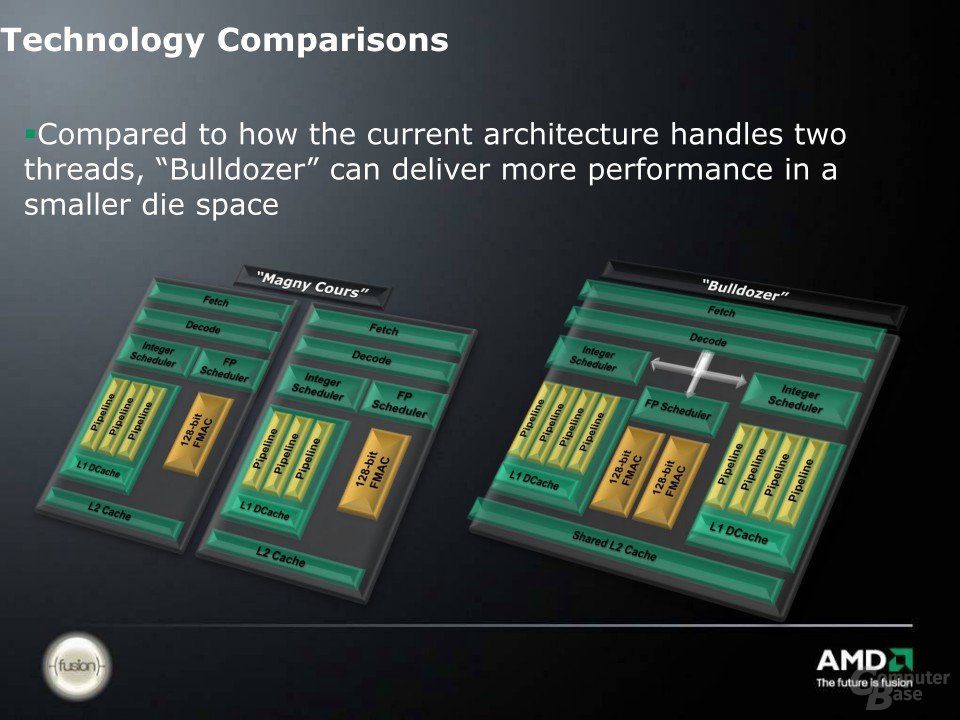

Die grundlegenden Unterschiede zwischen „Bulldozer“ und der noch aktuellen Architektur erklärt die folgende (bereits ältere) Abbildung. AMD hatte die Grundzüge der „Bulldozer“-Architektur allerdings bereits im vergangenen Herbst bekannt gegeben. Die neue 256-Bit-Gleitkomma-Einheit wird ebenfalls unter den Integer-Kernen eines Moduls aufgeteilt. Je nach Bedarf steht ihre komplette Bandbreite (256 Bit) einem Kern/Thread zur Verfügung oder aber jedem Kern/Thread die Hälfte der Bandbreite mit 128 Bit. Daraus ergibt sich die Flexibilität der „FlexFP“. Vorherige Architekturen verfügten über eine statische 128-Bit-Gleitkomma-Einheit (FPU) pro Kern. Die „FlexFP“ bringt außerdem neue Befehlssätze mit sich: Dazu zählen unter anderem SSS3, SSE 4.1/4.2, AVX, AES und FMA4.

In seinem Blogeintrag weist auch AMDs Chipdesigner Michael Golden immer wieder auf die ebenfalls im Vorfeld angekündigten hohen Taktfrequenzen von „Bulldozer“ hin, wobei Begriffe wie „high-speed operation“ oder „multi-gigahertz“ fallen. Konkrete Taktraten nennt er aber nicht. Das grobe Ziel von 3,5 GHz oder mehr, das AMD in Aussicht stellte, bleibt also zunächst die einzige Angabe zu den Frequenzen der Kerne.

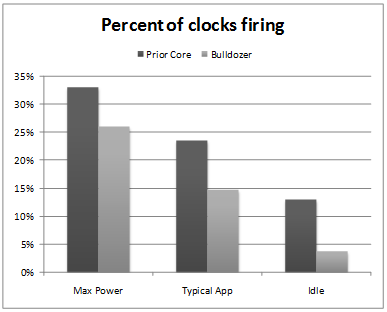

In einem weiteren Blogeintrag geht AMD noch auf die neuen Stromsparmechanismen von „Bulldozer“ ein, wobei nicht geforderte Kerne dank vollständigem „Power Gating“ nun auch komplett abgeschaltet werden können, sodass sie nahezu keinen Strom verbrauchen. Die zwischen Kernen geteilten Ressourcen der Modul-Struktur sollen ebenfalls ihren Teil zu einer höheren Energieeffizienz beitragen. Anhand einer Abbildung demonstriert AMD noch die Vorzüge des optimierten „Clock Gatings“, bei dem der Verschwendung von Energie durch nicht benutzte Transistoren entgegen gewirkt wird. Die Verbesserungen gegenüber den Vorgängern soll folgende Darstellung aufzeigen.

Alles in allem sind die neuen Details zu „Bulldozer“ doch sehr spärlich und der Rest durch die großen Events Hot Chips im letzten Sommer, den eigenen Financial Analyst Day und auch die Vorabankündigung zum ISSCC im letzten November größtenteils bereits bekannt. Aber auf der in wenigen Tagen beginnenden CeBIT könnte AMD eventuell etwas handfestere Informationen zu „Bulldozer“ präsentieren, zumindest deuten unbestätigte Gerüchte darauf hin.