AMD Brazos im Test: Der perfekte Wohnzimmer-PC

Einleitung

Letzen Endes hat es viel länger gedauert als eigentlich geplant. Aber wie auch immer, mittlerweile ist AMDs „Low Power“-Plattform Brazos im Handel erhältlich und es tauchen immer mehr Mainboards und komplette Systeme verschiedener Hersteller bei den gängigen Online-Shops auf.

Doch was versteckt sich genau hinter Brazos? Schlussendlich nichts anderes als eine Dual-Core-CPU, die mit einer Radeon HD 6310 gepaart wird, um Intels „Atom“ das Leben schwer zu machen. Und damit eignet sich solch eine Kombination nicht nur sehr gut für Netbooks, sondern auch für den Einsatz in HTPCs im eigenen Wohnzimmer, die für die Videowiedergabe zuständig sind. Denn genau für dieses Szenario bringt Brazos alles mit, was notwendig ist: Sämtliche Blu-rays können perfekt beschleunigt werden, HDMI 1.4a für eine 3D-Wiedergabe ist vorhanden, HD-Audio kann per Bitstream-Verfahren weitergegeben werden und das alles wird noch mit einer sehr niedrigen Leistungsaufnahme ermöglicht.

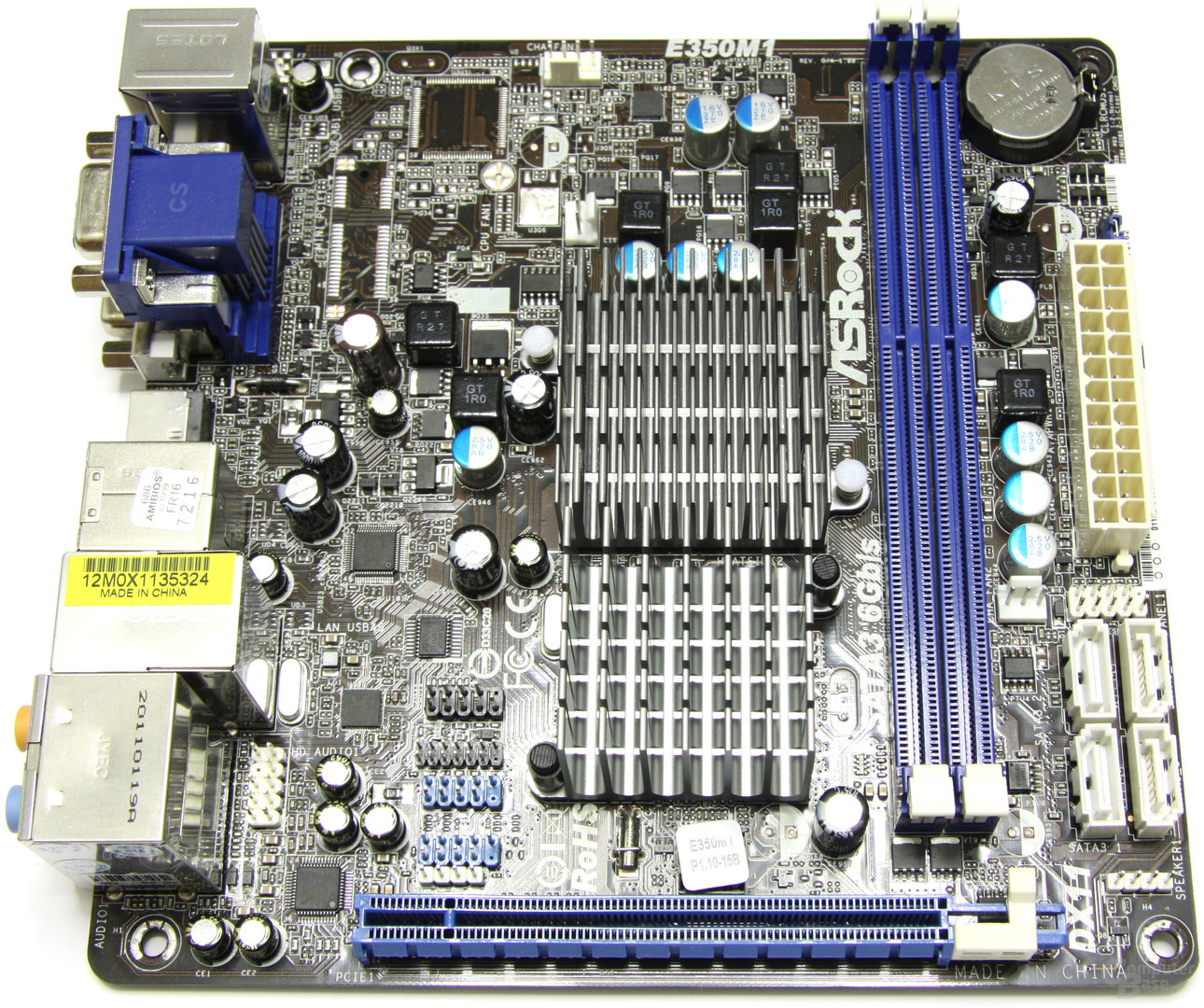

Wir haben uns für den Artikel unter anderem Mainboards von ASRock, von Asus sowie von MSI geschnappt, bei denen es von einer reichhaltigen Ausstattung inklusive passiver Kühlung bis hin zum rein auf Leistungsaufnahme optimierten Design alles gibt. Darüber hinaus werfen wir einen kleinen Blick auf ein Komplettsystem des Online-Shops memo.

Für die Testreihen setzen wir zudem einzig auf Komponenten, die für einen Low-Power-Rechner optimiert sind. Das fängt beim HTPC-Gehäuse an und hört beim Pico-ITX-Netzteil mit gerade 75 Watt Leistung auf.