Sparsames DDR3-SDRAM mit TSV-Stacking von Elpida

Elpida hat mit der Auslieferung erster Muster eines DDR3-SDRAM-Speicherchips auf Basis von TSV-Stackingtechnologie (Through Silicon Vias) begonnen. Bei der TSV-Technologie sind statt des üblichen Wire bondings vertikal durch das Silizium angeordnete, mit Kupfer gefüllte Löcher mit Durchmessern im Mikronbereich vorhanden.

Dadurch werden die Signalverbindungen beachtlich verkürzt, wodurch sich der aus mehreren übereinander gestapelten Chips RAM-Baustein wie ein einziger Siliziumchip verhalten soll. Dies soll unter anderem höhere Taktraten, eine geringere Leistungsaufnahme und eine kleinere Package-Größe ermöglichen.

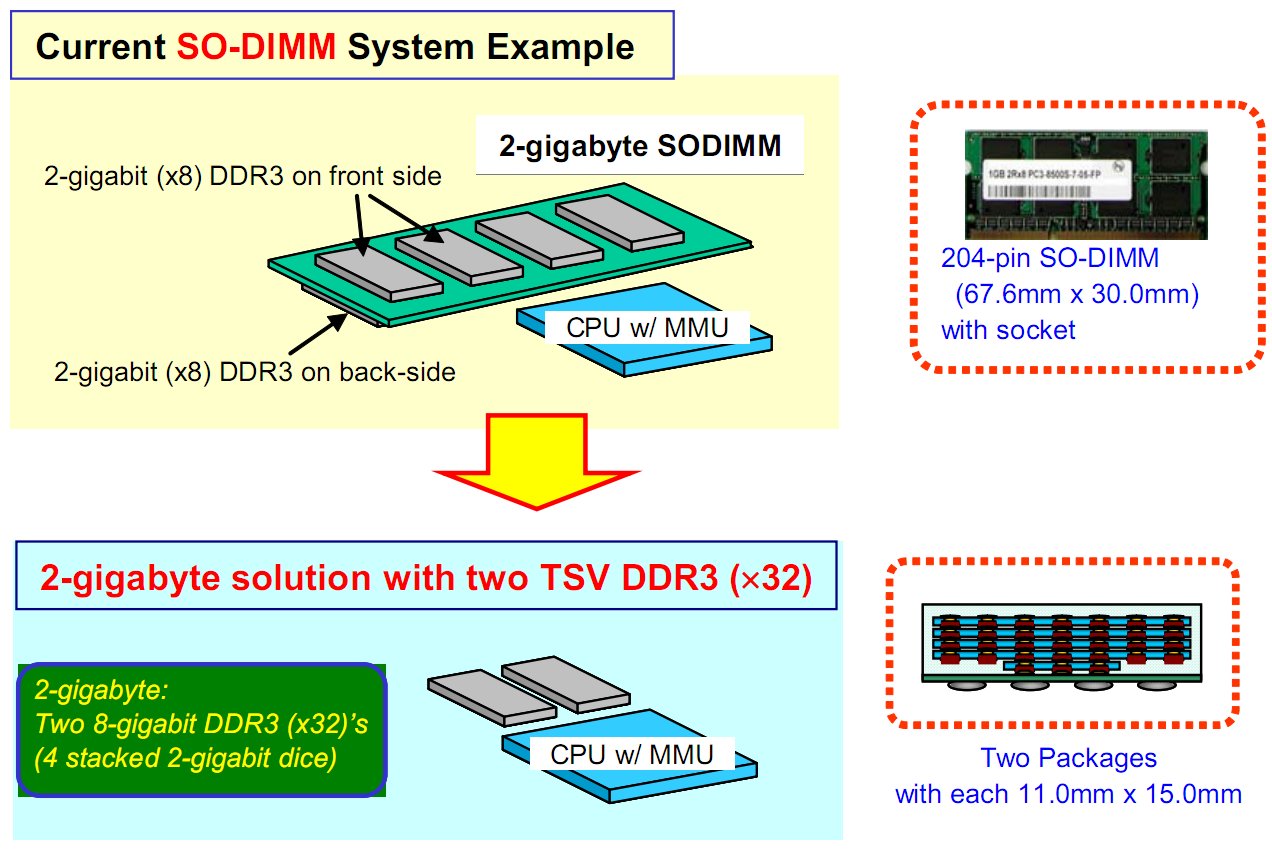

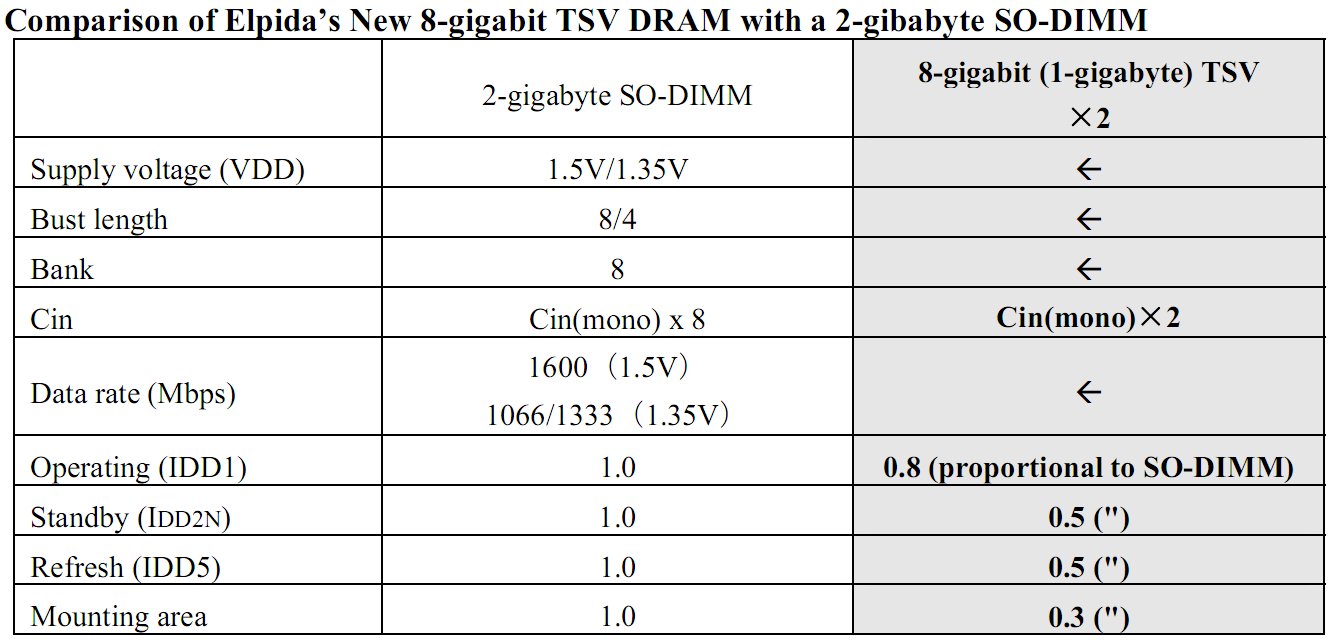

Der nun gefertigte Low-Power-DRAM-Baustein mit – ebenso wie der Speicher für Grafikkarten – 32 Datenpins besteht aus vier übereinander angeordneten 2-Gbit-Chips, hat also eine Gesamtkapazität von 8 Gigabit respektive einem Gigabyte. Der benötigte Platz könne um 70 Prozent verringert, die Chip-Höhe reduziert und der DIMM-Sockel ganz weggelassen werden, etwa bei Tablet-PCs. Als Anwendungsgebiete gibt Elpida daher neben Tablet-PCs auch sehr dünne PCs und andere mobile Systeme an. Hinsichtlich des Energieverbrauches schätzt das Unternehmen, dass Tests der TSV-DRAMs in Notebooks verglichen mit SO-DIMMs eine 20 Prozent geringere Leistungsaufnahme im Betrieb und sogar eine 50 Prozent geringere Leistungsaufnahme im Standby zeigen werden. Einen Termin für die Massenproduktion der DRAM-Chips nannte Elpida bislang nicht.

Die Entwicklung der TSV-Technologie bei Elpida begann im Jahre 2004. Einen ersten Meilenstein erreichte man dann 2009 mit der Entwicklung eines TSV-DRAMs das aus acht jeweils ein Gigabit großen DDR3-Chips bestand. Doch nicht nur Elpida beschäftigt sich mit TSV-Technologie, auch bei Samsung und Micron wird an Produkten auf Basis dieser Stackingtechnologie gearbeitet.