IBM zeigt Multi-Level Phase-Change Memory

Forscher von IBM Research ist ein entscheidender Schritt bei der breiten Nutzbarmachung von sogenanntem Phase-Change Memory (PCM) oder PRAM (Phase-Change Random Access Memory) gelungen. Sie konnten erstmals zeigen, dass das zuverlässige Speichern von mehreren Bit pro Zelle (Multi-Level) über einen längeren Zeitraum möglich ist.

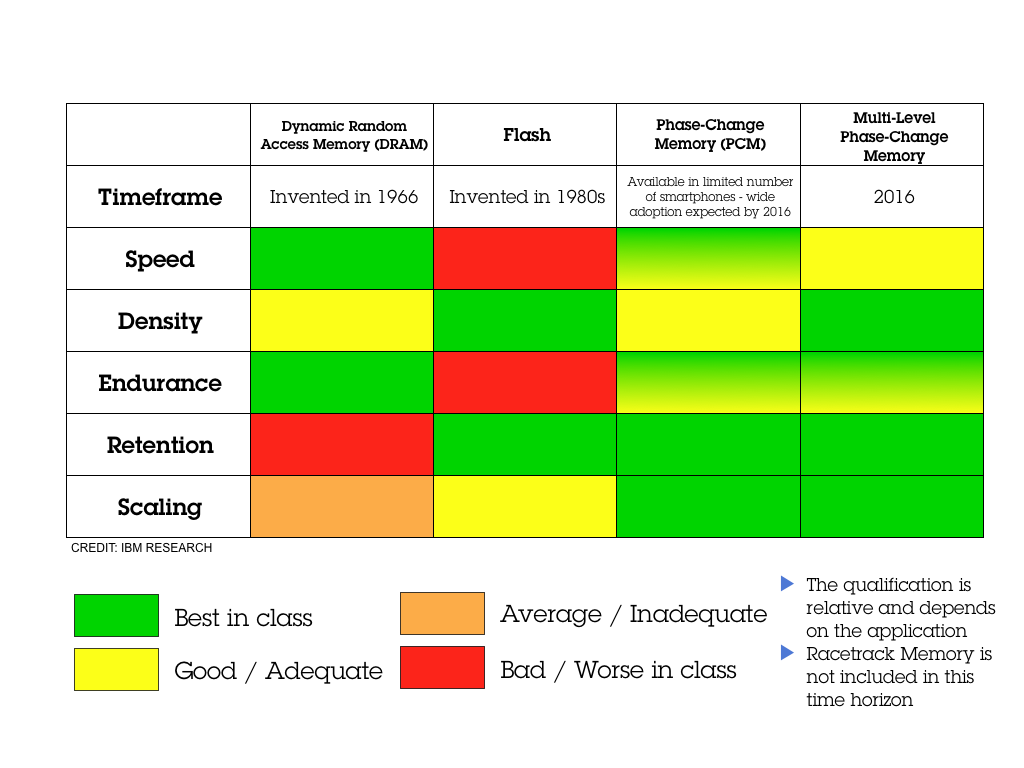

Interessant im Vergleich mit den anderen gängigen Halbleiter-Speichern DRAM und Flash macht PCM vor allem die Kombination seiner Eigenschaften: Eine – nunmehr – hohe Speicherdichte, aus der geringere Kosten resultieren, eine relativ hohe Geschwindigkeit, die zwischen Flash und DRAM liegt, eine im Vergleich zu Flash deutlich höhere Lebensdauer sowie der Erhalt der Daten beim Abschalten eröffnen bisher nicht gekannte Anwendungsmöglichkeiten.

Dass die grundsätzliche Technik bereits markttauglich ist, sieht man am Beispiel Samsungs. Das Unternehmen fertigt bereits seit bald zwei Jahren PRAM-Chips für den Einsatz in Mobilgeräten, die jedoch nur ein Bit pro Zelle speichern können. Den allgemeinen Durchbruch von PCM erwartet man zumindest bei IBM aber erst für 2016.

Beeindruckend sind die Daten, die IBM zur Leistung nennt. PCM soll Daten 100 mal schneller lesen und Schreiben können als Flash-Speicher und dabei mit mindestens zehn Millionen Write-Cycles auch noch deutlich langlebiger sein. Normale MLC-NAND-Speicherchips kommen derzeit auf lediglich 3.000 bis 5.000 P/E-Cycles, die Enterprise-Varianten auf 30.000. Während der normale Nutzer mit der Lebensdauer von MLC-Flash problemlos zurecht kommt, ist die deutlich längere Lebensdauer von (Multi-Bit-) PCM im Unternehmensmarkt ein entscheidender Vorteil.

Veränderliche Widerstände als größtes Problem

Um die Probleme von Multi-Bit-PCM-Zellen zu verstehen, ist zunächst ein kurzer Exkurs zur Funktionsweise einer PCM-Zelle nötig. In dieser wird zum Speichern von Informationen der unterschiedliche elektrische Widerstand ausgenutzt, den die genutzte Materiallegierung abhängig vom kristallinen (niedrig) oder amorphen (hoch) Aggregatzustand hat. In der Zelle befindet sich das Material zwischen einer oberen und einer unteren Elektrode, durch die sich mit unterschiedlich starken Strom- und Spannungsimpulsen der Phasenwechsel vom kristallinen in den amorphen Zustand und umgekehrt induzieren lässt. Die Impulse heizen das Material auf, bis bei einer bestimmten Schwellentemperatur der Phasenwechsel stattfindet.

Der Trick zum Speichern von mehr als einem Bit pro Zelle ist nun, dass abhängig von der Spannung nur ein Teil des Materials die Phase wechselt, was sich wiederum auf den Widerstand auswirkt. Die Forscher nutzen derzeit vier verschieden hohe Widerstände, um vier Bit-Paare – 00, 01, 10 und 11 – speichern zu können. Damit das Ganze auch zuverlässig funktioniert, waren jedoch technische Verbesserungen bei den Schreib- und Leseprozessen notwendig.

Beim Schreiben setzen sie auf einen schrittweisen Prozess, um Abweichungen vom gewünschten Widerstand auszugleichen, die durch Varianzen in Zellen und PCM-Material verursacht werden. Ausgehend von der Abweichung vom Sollwert wird ein entsprechend starker Spannungspuls angewendet. Stimmt der Widerstand noch immer nicht, folgen solange weitere, angepasste Pulse, bis der Sollwert erreicht ist. Trotz dieses vergleichsweise aufwendigen Schreibprozesses sei PCM mit einer maximalen Latenz von rund zehn Mikrosekunden noch immer 100 mal schneller als die schnellsten derzeit erhältlichen Flash-Chips.

Ein ähnliches, Resistance Drift genanntes Problem tritt beim Lesen der Daten auf. Da die Struktur der Atome im amorphen Zustand sich mit der Zeit entspannt, steigt der Widerstand kontinuierlich an, was schließlich zu Lesefehlern führt. Um das Problem zu überwinden, nutzen die Forscher ein fortgeschrittenes Modulations- und Kodierungsverfahren, das gegenüber der Verschiebung des Widerstandes tolerant ist. Das Verfahren basiert auf der Tatsache, dass die relative Anordnung programmierter Zellen mit verschiedenen Widerstandsgrößen sich im Schnitt trotz der Verschiebungen nicht ändert.

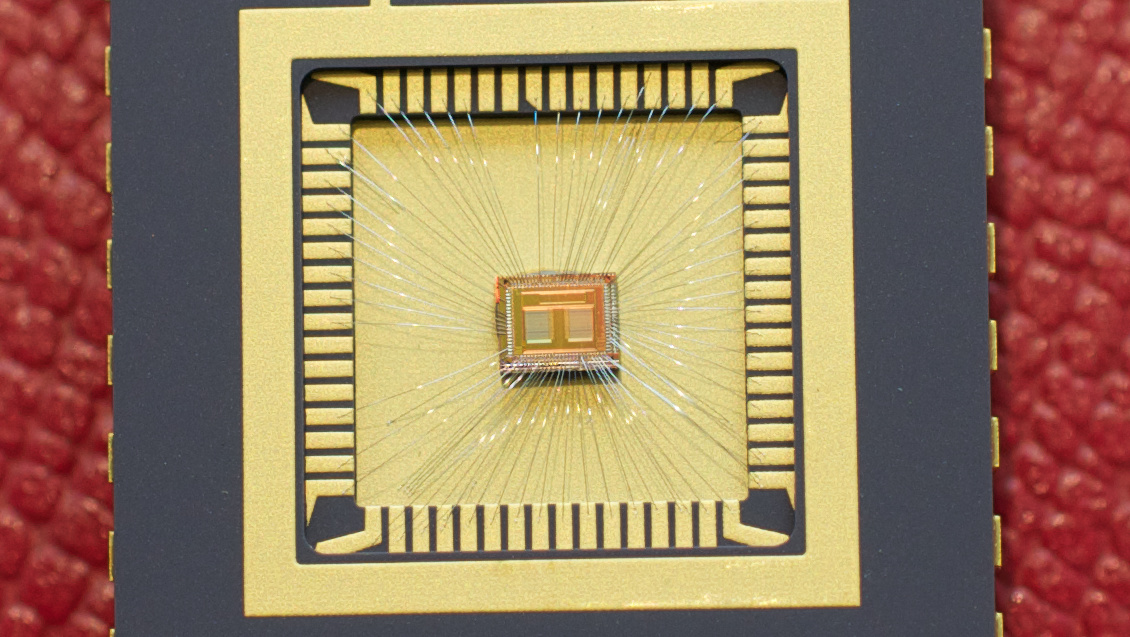

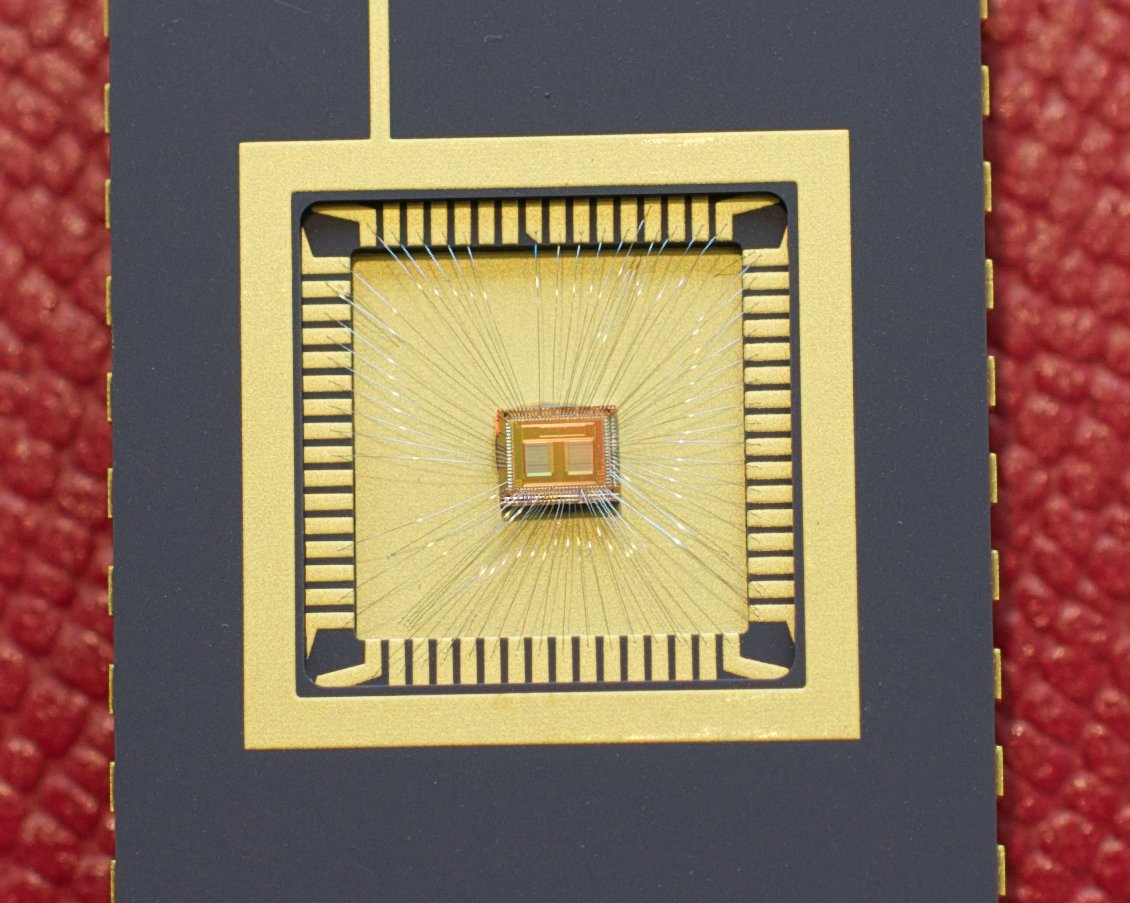

Als Demonstrationsobjekt für die Lösung der Verschiebungsprobleme und der Langzeitsicherung der Daten über bislang mehr als fünf Monate diente den Forschern aus Burlington, Yorktown Heights und Zürich ein 200.000 Zellen großer Unterabschnitt ihres in einem 90-Nanometer-CMOS-Prozess gefertigten PCM-Test-Chips.