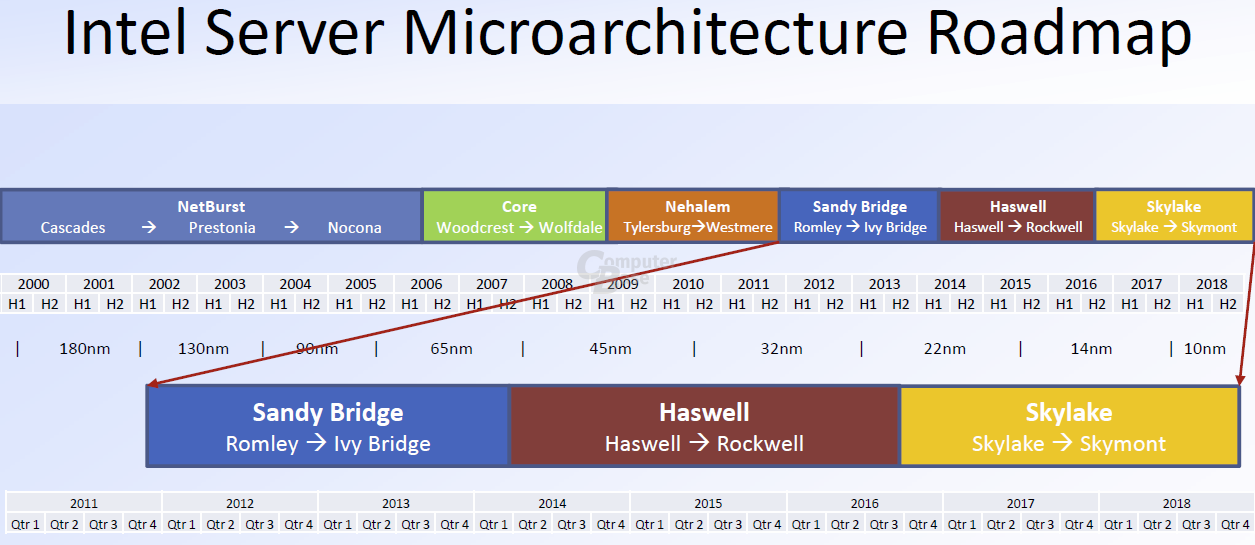

Intel-Roadmap für CPU-Architekturen bis 2018

Intels Tick-Tock-Strategie ist seit einigen Jahren im Einsatz und soll auch in Zukunft noch fortgeführt werden. Aufgrund verschiedener Voraussetzungen, insbesondere der immer anspruchsvoller werdenden Fertigung, könnte der Plan zunehmend schwieriger werden. Eine aktuelle Roadmap offenbart die Pläne.

Diese aktualisierte Roadmap für den Überblick der Architekturen im Server-Segment bringt einige Codenamen ins Spiel, die bereits zur CeBIT in diesem Jahr das erste Mal gefallen sind. Die Roadmap ist dabei fixiert auf die Architekturen und Produkte, die mindestens für 2-Sockel-Systeme eingesetzt werden können, weshalb „Sandy Bridge-E“ mit der „Romley“-Plattform auch das erste Modell dieser Architektur in dem Plan ist. Erwartungsgemäß wird auch von „Ivy Bridge“, dem Shrink der Sandy-Bridge-Architektur in die 22-nm-Fertigung, ein Produkt erwartet, das im High-End-Server-Segment angesiedelt ist.

Auf einen Shrink folgt wie üblich eine neue Architektur. Bereits in den letzten Veranstaltungen in diesem Jahr hat Intel mitgeteilt, dass „Haswell“ in 22 nm eine neue Architektur bieten wird. Ab Anfang 2014 sollen diese CPUs in großen Servern zum Einsatz kommen, in Desktops und Notebooks soll man es schon 2013 schaffen – der typische Abstand zwischen den ersten Modellen und High-End-Servern von einem halben bis zu einem Jahr soll auch in Zukunft bestehen. Natürlich gibt es bei „Haswell“ dann ebenfalls einen folgenden Shrink in der Fertigung, der die Architektur in den „Rockwell“-Prozessoren aufgehen lässt, die dann in 14 nm gefertigt werden sollen.

Dann erfolgt der nächste Schritt in der Tick-Tock-Strategie: die „Skylake“-Architektur. Jene wird in der ersten Phase wie immer die bereits eingesetzte Fertigungsweise übernehmen, eh sie dann nach der Hälfte ihrer Lebenszeit mit der Verkleinerung in die 10-nm-Herstellung in „Skymont“ mündet. Damit sollen die Server-Systeme bis Ende 2018 gerüstet sein, eh dann ein jetzt noch nicht bekannter Nachfolger ansteht.

Die Langzeitroadmaps aus dem Server-Bereich sind für unterschiedliche Planungen ausgelegt. Unter anderem geht es um die Steigerung der Netzwerkbandbreite in den kommenden Jahren. Mit PCI Express 3.0 wird der erste Schritt mit „Romley“ vollbracht, der beim Einsatz von zwei Prozessoren und dementsprechend vielen Lanes duale LAN-Verbindungen mit 40 Gbit/s ermöglichen soll. Als nächstes soll PCI Express 4.0 diesen Wert auf Dual-LAN mit 100 GBit/s steigern, der erstmals bei „Skylake“ ab dem Jahr 2016 genutzt werden könnte. Die Grundlagen für den neuen PCI-Express-Standard sollen bereits Ende 2011 gelegt werden. Eh sie jedoch verabschiedet werden, sind noch viele Forschungen und Maßnahmen nötig, weshalb noch gut fünf Jahre ins Land gehen dürften.