Extrem sparsame Prozessoren und viele Kerne

Zum Abschluss des IDF hat Intels Chief Technology Officer Justin Rattner einen Ausblick gegeben, welche technischen Entwicklungen wir in den nächsten Jahren erwarten können. Wie lassen sich Multi- und Many-Core-Prozessoren sinnvoll einsetzen, welche Möglichkeiten bieten sie und wie lässt sich die Energieeffizienz steigern?

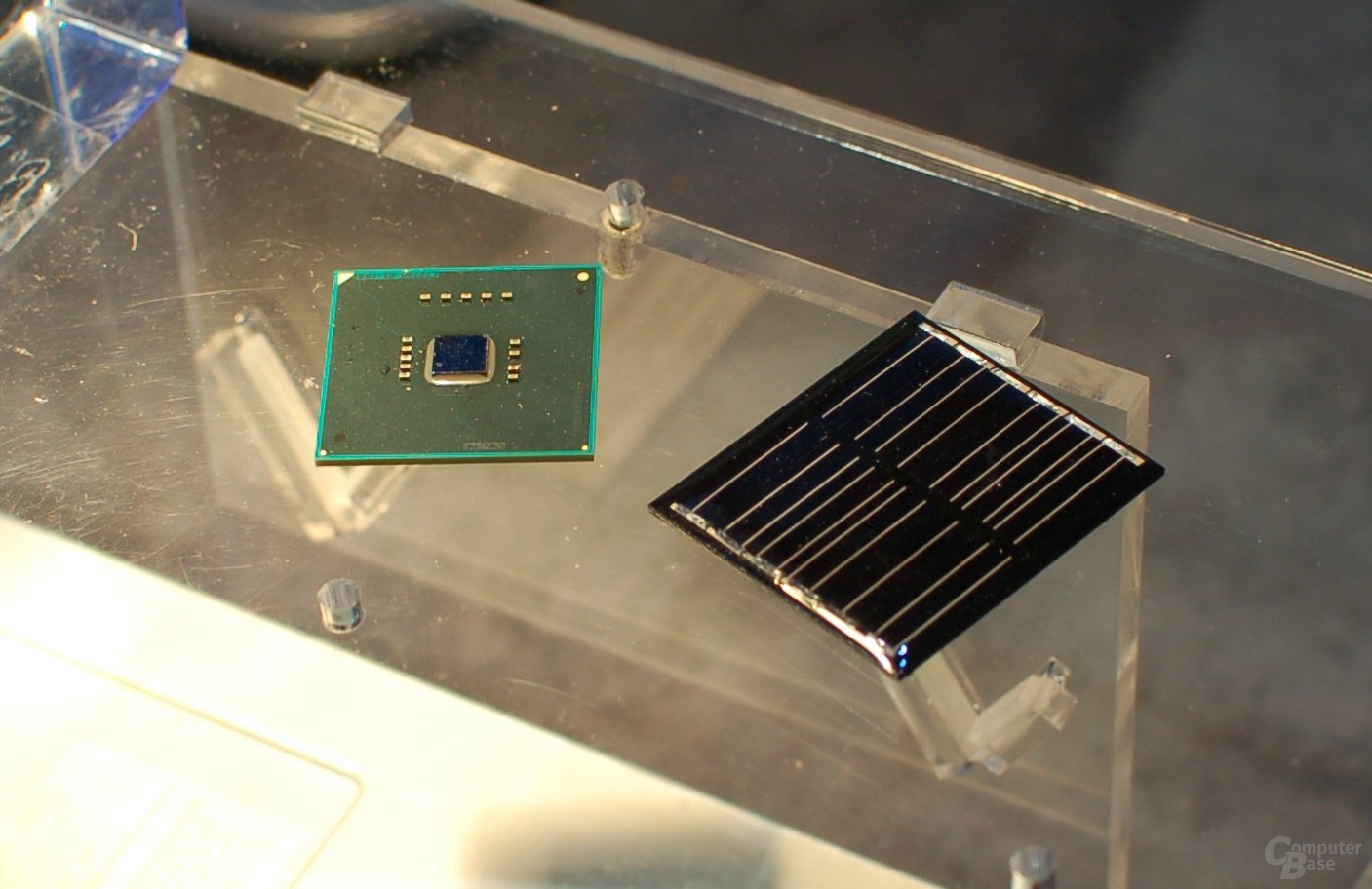

Bereits vor zwei Tagen zeigte CEO Paul Otellini in seiner Keynote einen experimentellen Prozessor, der mit einer kleinen Solarzelle angetrieben wird. Justin Rattner ging nun noch einmal ausführlicher auf den „Claremont“ genannten Prozessor ein. Dieser basiert auf einem Pentium-Kern mit 12 Millionen Transistoren, ist durch fortschrittliche Transistortechnik mit 22-Nanometer-Prozess und Tri-Gate-Transistoren aber sehr viel sparsamer. Dies wird möglich, da der Prozessor nahe der Schwellenspannung betrieben wird, bei der der Transistor sich einschaltet. Theoretisch lässt sich die Energieeffizienz so um das Acht- bis Zehnfache auf bis zu 89 Prozent steigern. Im Falle Claremonts ist es aufgrund des alten Pentium-Designs zwar nicht ganz so viel, aber die fünfmal höhere Energieeffizienz im Vergleich zu aktuellen Prozessoren ist dennoch beeindruckend. Auf dem Linux-Demosystem wurde Claremont mit unter 10 Milliwatt betrieben.

Ein Vorteil der Möglichkeit, den Prozessor nahe der Schwellenspannung zu betreiben, ist jedoch die Option bei Bedarf auch deutlich mehr Leistung abzurufen. Auf der Bühne wurde dies an einem zweiten System mit mehreren Hundert Megahertz Taktfrequenz gezeigt, auf dem Windows XP und Quake – das Original von 1996 – liefen. Dieses wurde mit der normalen Spannung betrieben und arbeitete mit einer mehr als zehnmal so hohen Taktrate. Eine dynamische Anpassung der Spannung ist derzeit nicht möglich, da die alten – übrigens extra auf Ebay gekauften – Pentium-Mainboards dafür nicht ausgelegt sind. Potenziell bietet der Betrieb nahe der Schwellenspannung die Möglichkeit Systeme 24 Stunden am Tag laufen zu lassen, aber den Prozessor in Ruhephasen so weit herunterzufahren, dass der Energiebedarf minimal ist.

Entscheidend sind solche Fortschritte bei der Energieeffizienz vor allem auch im Bereich Hochleistungsrechnen (High Performance Computing). Würde man die in den nächsten zehn Jahren angestrebten Exascale-Supercomputer auf Basis aktueller Technik bauen, würde der Energiebedarf in den Gigawatt-Bereich steigen. Ziel ist daher eine signifikante Senkung um den Faktor 100 bis 2018 und eine 300 mal höhere Energieeffizienz innerhalb der nächsten zehn Jahre. Während ein System mit 100 GigaFLOPS Rechenleistung heute noch rund 200 Watt benötige, soll dies 2018 mit 2 Watt oder weniger möglich sein.

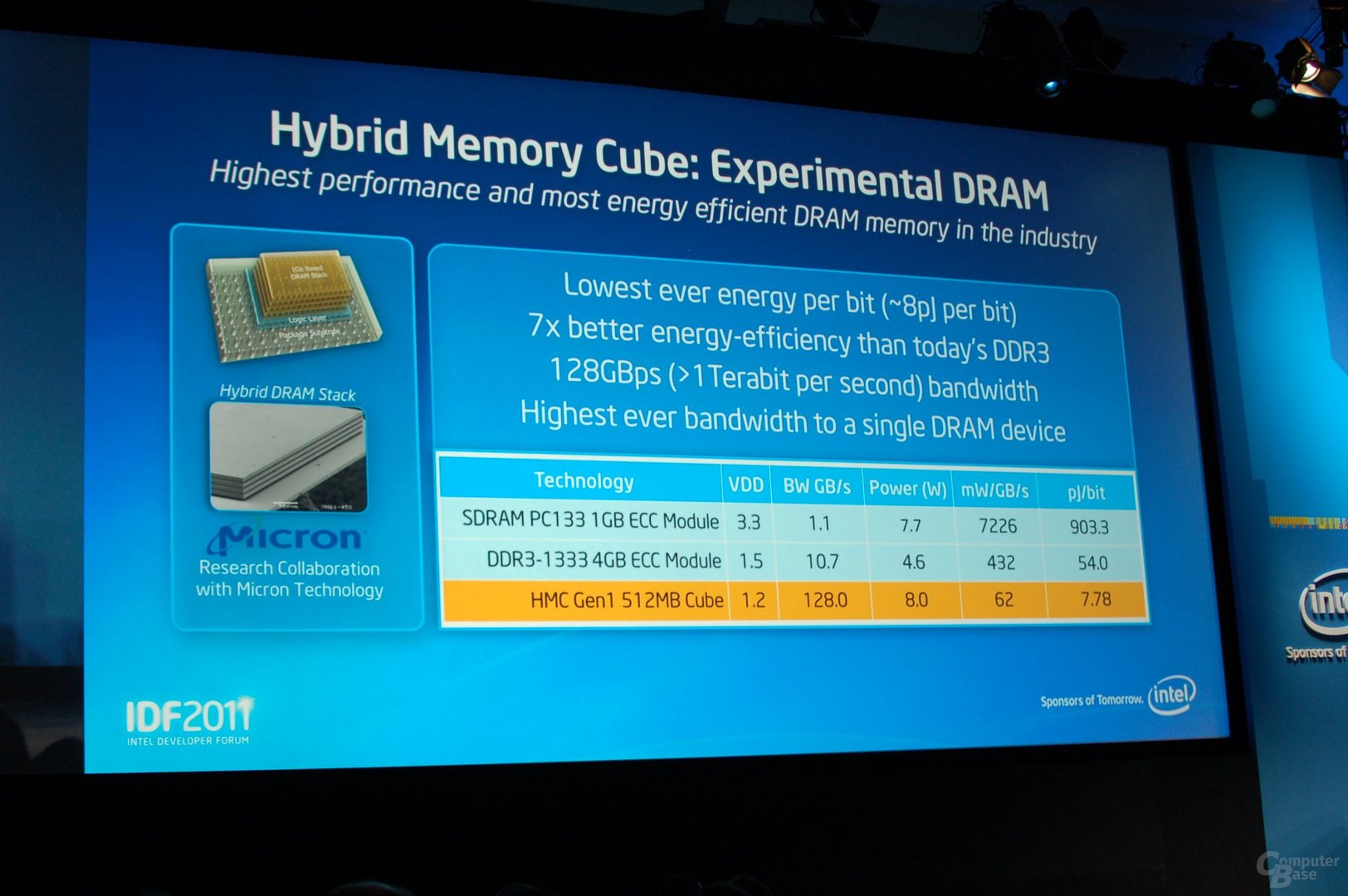

Ein weiterer Baustein in diesem Bestreben ist der Hybrid Memory Cube (wir berichteten), der die Leistung und Energieeffizienz im Vergleich zu traditionellen DRAM-Modulen um ein Vielfaches steigert.

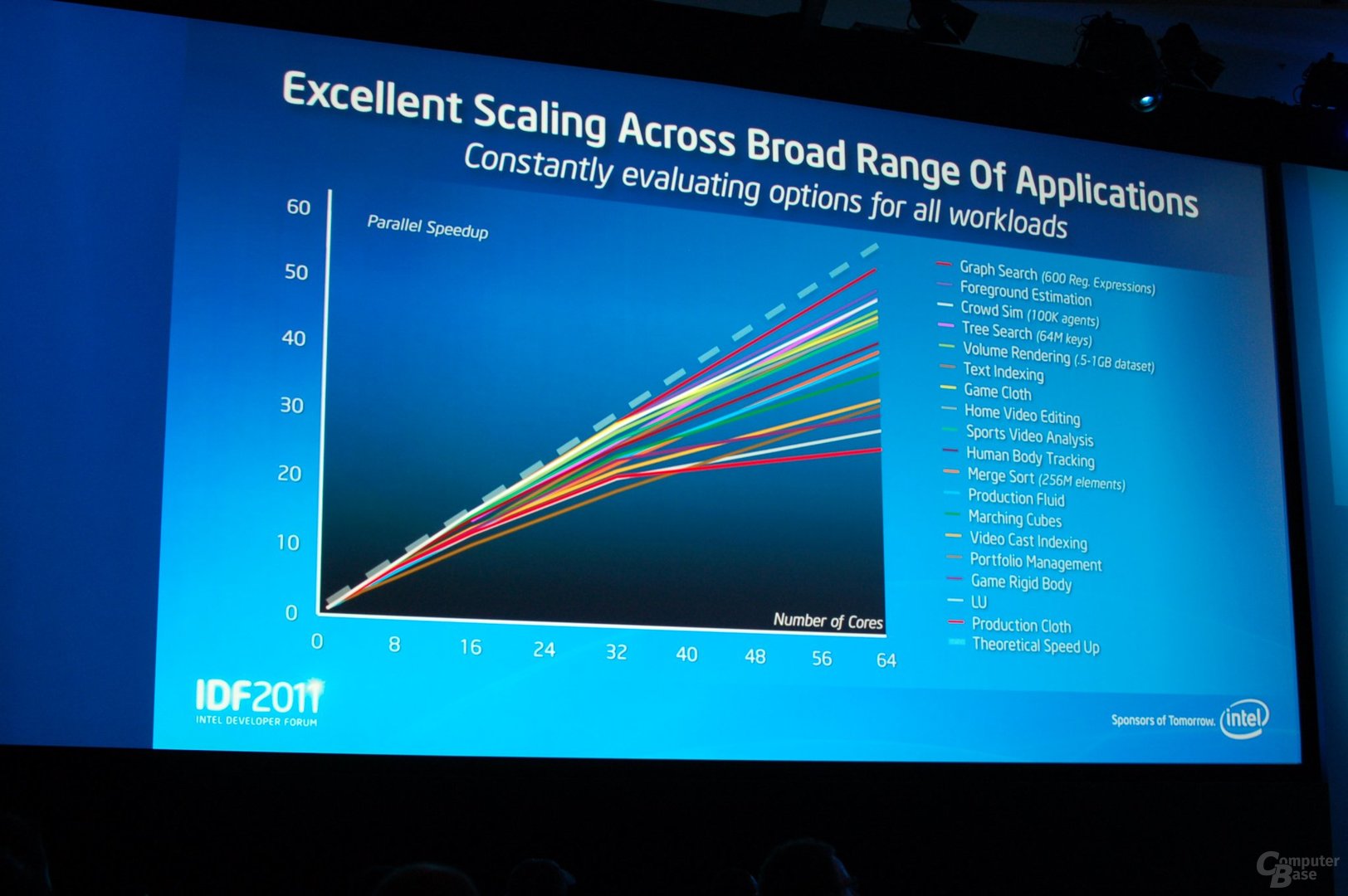

Das zweite große Thema von Rattners Keynote waren Multi- und Many-Core-Prozessoren sowie Intels Many-Integrated-Core-Architektur (MIC) und Möglichkeiten zur Nutzung der zur Verfügung stehenden Rechenleistung. Speziell hoch parallelisierbare Rechenlasten können von vielen Prozessorkernen profitieren. Ein Beispiel ist etwa die Auswertung von Daten des Teilchenbeschleunigers Large Hadron Colider (LHC) im europäischen Kernforschungszentrum CERN. Weitere Anwendungsbeispiele, die Rattner vorstellte, waren LTE-Basisstationen auf Basis eines Sandy-Bridge-Rechners, die Parallelisierung von JavaScript-Anwendungen auf Client-Seite mittels River Trail und das Ausnutzen der zahlreichen Kerne zur Echtzeit-Verschlüsselung von Multimediadaten im Internet.