Exakte Details zu Intels „Xeon-Phi“-MIC

Erinnert sich noch jemand an „Larrabee“? Intel hatte ursprünglich geplant, damit in den Grafikkartenmarkt einzusteigen und dort AMD sowie Nvidia anzugreifen. Das Unterfangen wurde aber schon lange aufgegeben und stattdessen will man mit dem MIC-Projekt (Many Integrated Core) nun in das HPC-Segment (High Performance Computing).

Unter dem Codenamen „Knights Corner“ und der finalen Bezeichnung „Xeon Phi“ soll dies in Kürze geschehen. Wirklich viele Details hat Intel zu Xeon Phi bis jetzt aber noch nicht bekannt gegeben, nur das die Hardware auf über 50 Rechenkerne zurückgreifen können soll, die mindestens 1 TFLOPS bei doppelter Genauigkeit (Linpack) erreichen soll.

VR-Zone möchte nun weitere Details zum aktuellen Stand von Xeon Phi in Erfahrung gebracht haben, wobei es sich teilweise um bereits bekannte Informationen handelt, die mit einigen Gerüchten vermischt werden. Demnach ist der ASIC nun in der B0-Version angekommen und soll in drei verschiedenen Varianten existieren: Mit 57, 60 und mit 61 Kernen, womit man die gewünschten 62 Kerne, die seit Monaten im Gespräch sind, fast erreicht hat. Je nach Variante soll der L1-Cache eine Größe von 1,8 bis 1,9 MB und der L2-Cache von 28 bis 30,5 MB aufweisen. Die Speicherausstattung beträgt drei, sechs oder acht Gigabyte nach dem GDDR5-Standard – der Maximalausbau war zuvor aber schon seitens Intel offiziell genannt worden.

Die „minimale“ Taktrate der Xeon Phi soll 600 MHz (mit 57 Kernen und drei oder sechs Gigabyte Speicher) beziehungsweise mindestens 630 MHz (60 und 61 Kernen mit acht Gigabyte) betragen. Die „normale“ Taktrate der Prozessorkerne beträgt laut VR-Zone 1,1 GHz (57 Kerne mit drei oder sechs GB), die anderen Karten sollen mit 1,05 bis 1,09 GHz arbeiten. Jedoch sollen die Xeon Phi neuerdings auch noch über eine Turbo-Funktion verfügen – dazu gibt es aber noch keine Informationen. Der Speichertakt liegt bei 2.500 MHz bis 2.740 MHz, womit die Speicherbandbreite aufgrund eines 512-Bit-Interfaces bei mehr als 300 Gigabyte pro Sekunde liegen würde.

Neben der Leistung wird angeblich auch die TDP variieren. So soll es zwei Boards mit 245 Watt (57 Kerne mit drei GB und 60 Kerne mit sechs GB) und drei Designs mit 300 Watt (57 Kerne mit sechs GB und zwei Platinen mit 61 Kernen und acht GB). Xeon Phi mit 57 Kernen, sechs GB und 300 Watt soll mit einem aktiven Kühlkörper daher kommen, während die restlichen Varianten mit einem passiven Konstrukt oder völlig ohne Kühlung (für Server-Racks) ausgestattet sind.

Als Leistungsvorgabe soll Intel ein Teraflop Double-Precision- und zwei Teraflop Single-Precision-Performance für Xeon Phi ansetzen. Passend dazu gibt Nvidia für die noch nicht erschienene GK110-GPU eine DP-Leistung von ebenso mindestens einem Teraflop an, wobei die SP-Geschwindigkeit bei deutlich über zwei TFLOPS liegen wird.

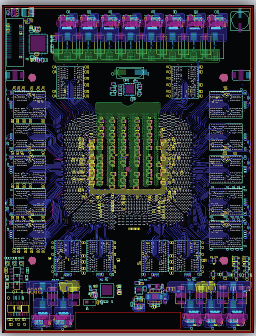

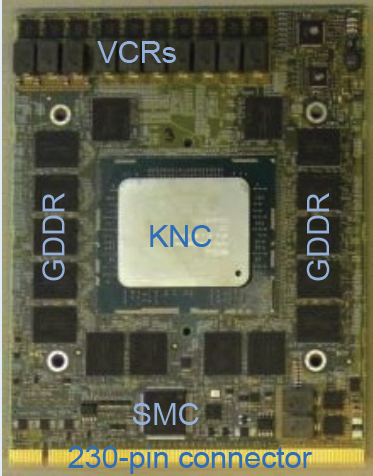

Passend zu diesen Spekulationen sind nun auch die ersten Bilder zu einer Knights-Corner-Platine im PCIe-Format sowie im „Dense Form Factor“ aufgetaucht, die in einer Präsentation auf der International Supercomputing Conference (ISC) verwendet worden sind. Weitere Details zu den Xeon Phi dürften in den kommenden Wochen bekannt werden, denn ausgeliefert werden sollen die ersten Systeme zum Ende des Jahres.