IBM nennt Details zum High-End-Prozessor Power8

Auf der diesjährigen Ausgabe des Hot-Chips-Symposiums hat IBM den neuen Vertreter der Power-Mikroprozessoren im Detail vorgestellt. Der Power8 stellt dabei nicht nur den Vorgänger, sondern auch aktuelle CPUs der Konkurrenz bei den technischen Daten in den Schatten.

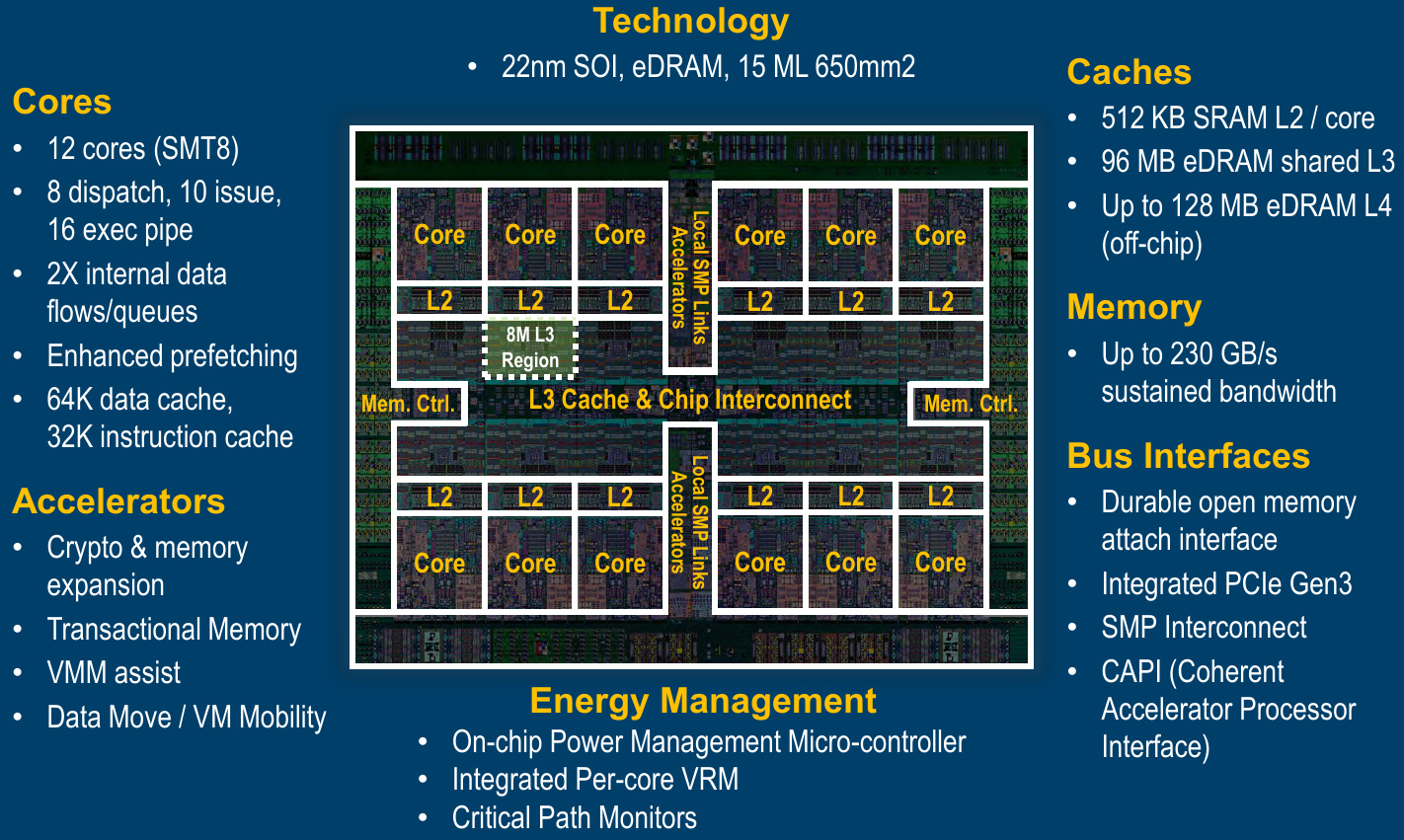

Der mit 650 mm² Fläche trotz feinem 22-nm-Herstellungsprozess vergleichsweise riesig ausfallende Chip beherbergt zwölf Rechenkerne, die jeweils über 512 Kilobyte SRAM als L2-Cache verfügen. Hinzu kommen insgesamt 96 Megabyte eDRAM als L3-Cache, den sich die Kerne allerdings teilen. Eine vierte Cache-Stufe wird über einen externen eDRAM-Speicher mit bis zu 128 Megabyte realisiert. Hier werden acht „Memory-Buffer-Chips“ mit jeweils 16 Megabyte eDRAM genannt, die folglich außerhalb des Chips Platz finden mussten. Diese sollen als Puffer für Zugriffe auf bis zu vier SDRAM-Speicherriegel dienen. Dadurch soll eine kontinuierliche Datentransferrate von bis zu 230 Gigabyte pro Sekunde vom Speicher hin zum Prozessor ermöglicht werden, berichtet heise online. Noch höhere Transferraten von bis zu 256 Gigabyte pro Sekunde sollen beim Datenaustausch zwischen CPU-Kern und L2-Cache erzielt werden.

Mit welchen Taktraten der Power8 genau arbeitet, hat IBM offenbar noch nicht angegeben. Laut Heise deuteten jedoch einige Folien auf einen Kerntakt von 4 GHz hin. Der 2012 an gleicher Stelle vorgestellte Vorgänger Power7+ arbeitet mit 2,4 bis 4,25 GHz. Gegenüber dem noch älteren Power7 soll die Single-Thread-Leistung der Kerne um den Faktor 1,6 ansteigen. Dadurch, aber vor allem durch 50 Prozent mehr Kerne (zwölf statt acht) sowie die Verdoppelung von vier auf acht Threads pro Kern (96 Threads pro CPU) soll die maximale Leistung beim Simultaneous Multithreading (SMT) verdoppelt werden. Mit welcher Leistungsaufnahme respektive Wärmeentwicklung die enorme Ausstattung des großen Chips einhergeht, hat IBM offenbar noch nicht verraten. Der Power7 brachte es auf rund 200 Watt TDP.

Eine weitere Neuerung betrifft die Kommunikation mit Peripherie: Diese erfolgt nun direkt über PCI Express der Generation 3.0, wobei keine Angaben zur Anzahl der verbauten Lanes gemacht werden. Zudem ist angeblich jeder Kern mit einem eigenen Spannungswandler versehen.

Ab 2014 soll der im SOI-Verfahren mit 22 nm Strukturbreite gefertigte IBM Power8 in IBM-Servern eingesetzt werden.