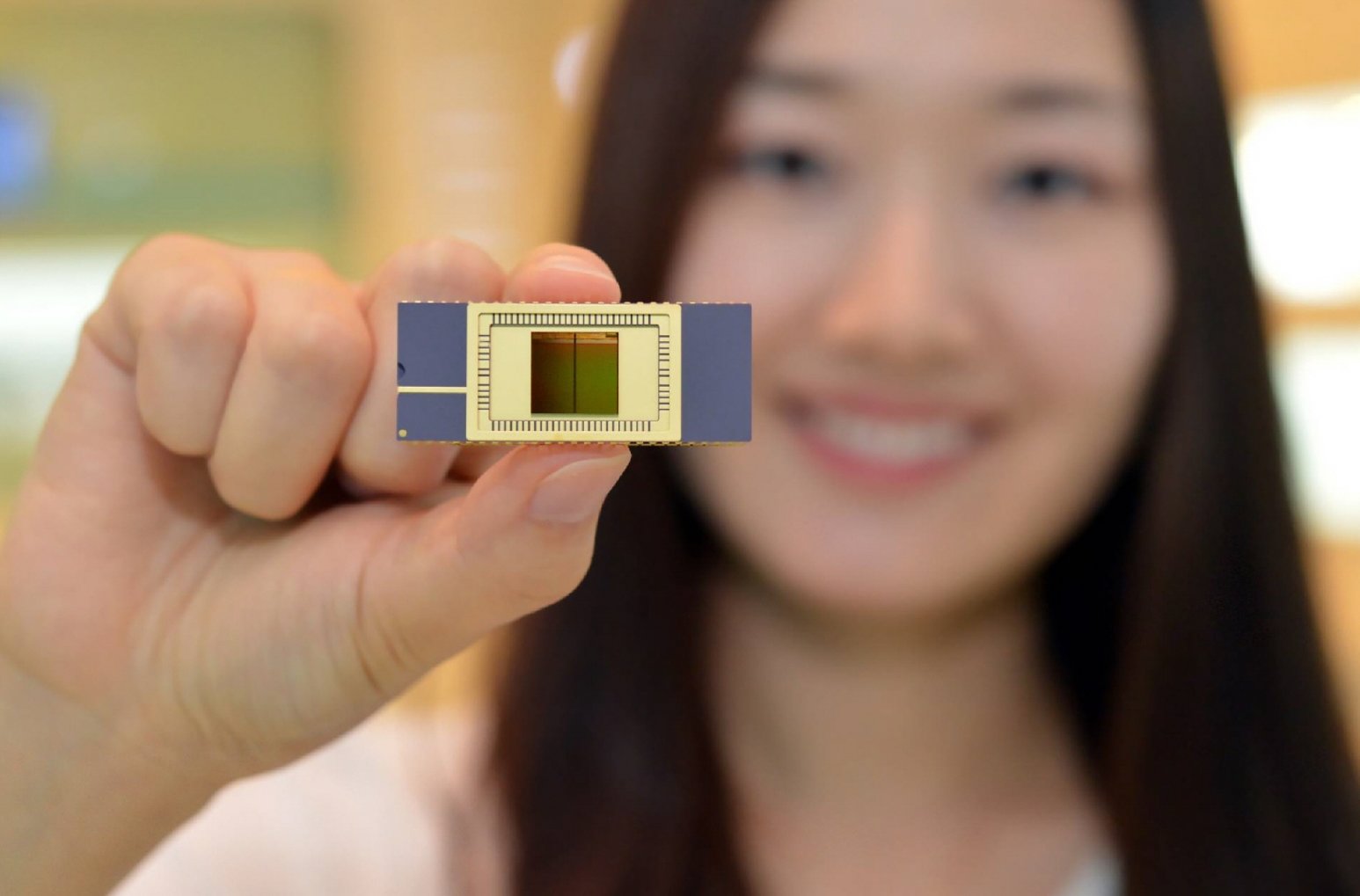

Samsung beginnt Massenproduktion von 3D-NAND-Flash

Seit etlichen Jahren forscht die Speicherbranche am sogenannten „Vertical 3D NAND“. Die Prognosen, dass dieser ab 2013 in Produktion gehen wird, wurden bestätigt. Samsung fertigt den neuen Speicher sogar bereits in hohen Stückzahlen und übertrifft damit manche Erwartung.

Per Pressemitteilung ließ Samsung am Dienstag verlauten, dass die eigene Halbleitersparte „mit der Massenproduktion des industrieweit ersten dreidimensionalen (3D) Vertical NAND (V-NAND) Flash Memory“ begonnen habe. Die Speicherchips besitzen eine Kapazität von 128 Gigabit und weisen erstmals eine vertikale Zellenstruktur auf, während Flash-Speicher bisher auf planaren Strukturen basierte. Dieses Verfahren soll Vorteile bezüglich Kapazität pro Chip und Geschwindigkeit des NAND-Flash bieten sowie die Zuverlässigkeit steigern, indem problematische Interferenzen zwischen Zellen vermieden werden.

Nach eigenen Angaben nutzt Samsung eine „proprietäre vertikale Zellenstruktur“, die auf „3D Charge Trap Flash (CTF) Technologie und vertikaler Interconnect-Prozesstechnologie zur Verbindung des 3D Zellenarrays“ basiert. Planare Zellenschichten (Layer) werden dabei übereinander gestapelt, was auch als „Stacking“ bekannt ist.

Samsungs neues V-NAND meistert technische Herausforderungen wie diese, indem es neue Maßstäbe hinsichtlich Innovation bei Schaltkreisen, Struktur und Fertigungsprozess setzt. Auf dieser Basis konnte ein vertikales Stapeln (Stacking) planarer Zellenlayer für eine neue 3D-Struktur erfolgreich entwickelt werden. Um dies zu tun, überarbeitete Samsung seine CTF-Architektur, die erstmals 2006 entwickelt wurde. Bei Samsungs CTF-basierter NAND Flash Architektur wird eine elektrische Ladung temporär in eine Haltekammer des nicht leitenden Flash Layers platziert, der statt ein Floating Gate zur Verhinderung von Interferenzen zwischen benachbarten Zellen aus SiN (Silizium-Nitrid) besteht.

Indem dieser CTF-Layer dreidimensional gemacht wurde, haben sich die Zuverlässigkeit und die Geschwindigkeit von NAND Memory deutlich erhöht. Das neue 3D V-NAND zeigt nicht nur eine minimal um das Zweifache und maximal um das Zehnfache höhere Zuverlässigkeit, sondern erreicht gegenüber 10nm-Class Floating Gate NAND Flash Memory auch die doppelte Schreibgeschwindigkeit.

Eine der wichtigsten technologischen Leistungen des neuen Samsung V-NAND ist, dass man die proprietäre vertikale Interconnect Prozesstechnologie des Unternehmens bis zu 24 Zellenlayer vertikal übereinander stapeln kann. Dazu wird eine spezielle Ätztechnologie verwendet, die die Layer elektronisch verbindet, indem Löcher vom obersten zum untersten Layer gestanzt werden. Mit der neuen vertikalen Struktur kann Samsung NAND Flash Memory Produkte mit höherer Speicherkapazität realisieren. Dazu wird die Zahl der 3D Zellenlayer ohne planare Skalierung erhöht. Dies war bisher nur schwer erreichbar.

Wie auch in anderen Halbleitersegmenten, wie beispielsweise Stacked DRAM oder Tri-Gate-Transistoren (FinFETs) bei Prozessoren, suchen die Hersteller ihr Heil in der Höhe, um mehr Kapazität oder Funktionen auf gleicher Fläche unterzubringen, während eine Verkleinerung der Strukturen immer schwieriger und aufwändiger wird.

Nach Angaben von Samsung sind bis zum Start der Massenfertigung von 3D Vertical NAND zehn Jahre Forschungsarbeit ins Land gezogen. Der Konzern bezeichnet den Meilenstein als „Grundlage für noch innovativere Produkte wie 1 Terabit (Tb) NAND Flash“, hier wird deutlich, was das Stapeln von Speicherzellen möglich machen soll, während die Skalierbarkeit bei herkömmlicher NAND-Flash-Struktur allmählich an ihre Grenzen stößt.

Auch Toshiba, SK Hynix und Micron forschen seit Jahren an NAND-Flash mit dreidimensionaler Struktur. Ihnen ist Samsung nun offenbar zuvorgekommen, was die Vollendung eines für die Massenproduktion tauglichen Chips angeht.