Intel „Broadwell“ im Detail: Loch im Mainboard für Core M

4/5Geringe Ausbeute und hohe Kosten

Erstaunlich offen gab sich Intel in exklusiver Runde in Bezug auf die Probleme mit der 14-nm-Fertigung. Während in den vergangenen Monaten lediglich viele Gerüchte die Runde machten, ließ Intel in der letzten Woche deutlich mehr Details durchblicken.

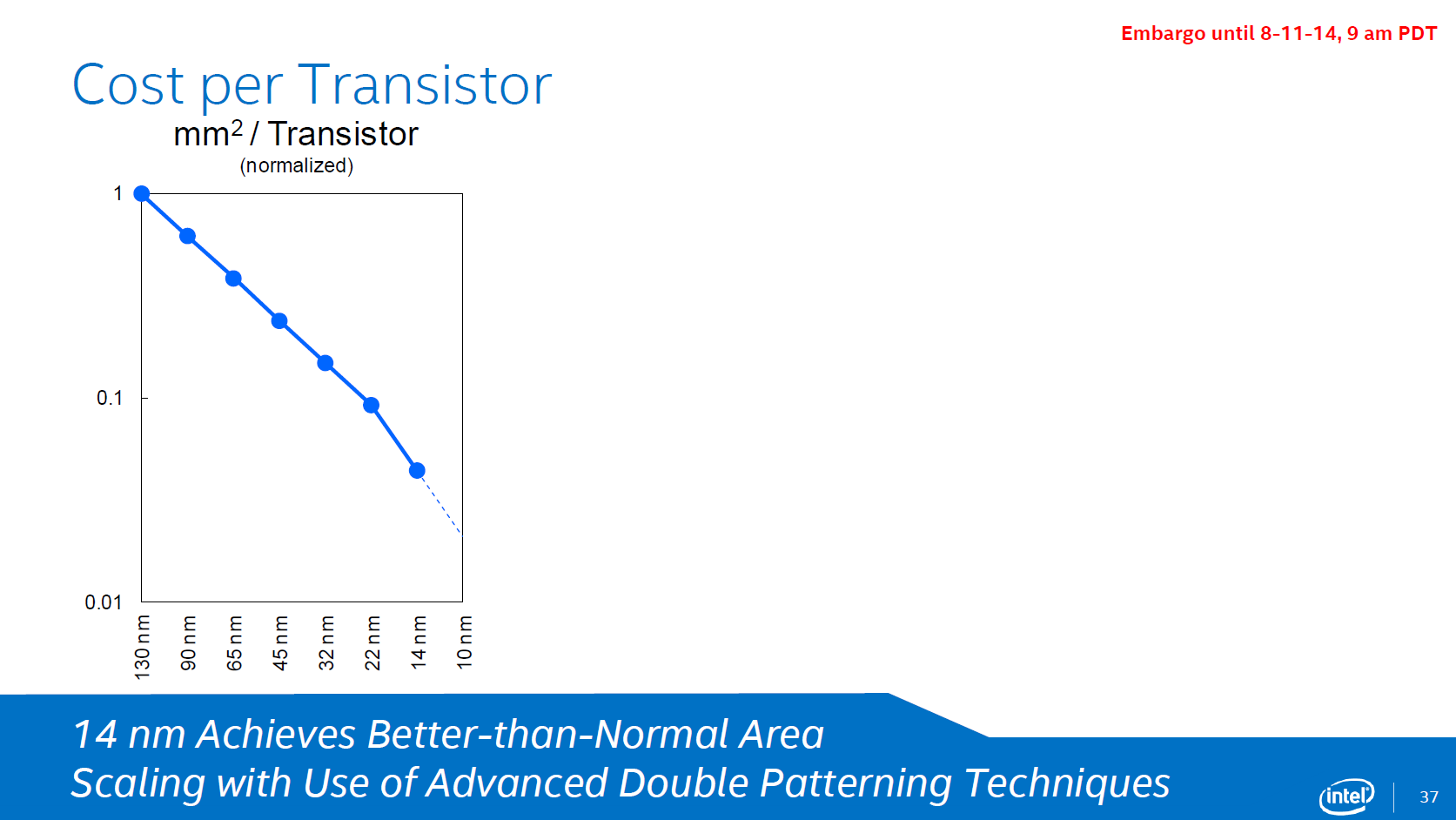

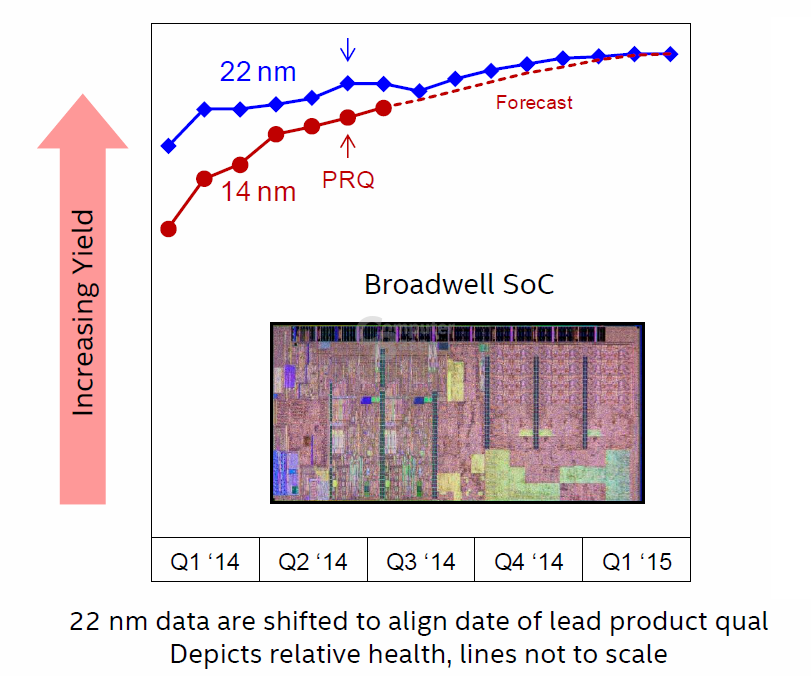

Demzufolge war gemäß des Tick-Tock-Modells ursprünglich geplant, die 14-nm-Fertigung bereits zum Ende des letzten Jahres zur Marktreife zu führen. Auf dem Weg dahin stieß Intel jedoch auf diverse Probleme, die zusätzliche Zeit und insbesondere auch Investitionen erforderlich machten. Noch im ersten Quartal lag die Yield-Rate, also die Ausbeute an funktionstüchtigen Chips pro Wafer, deutlich unterhalb dem, was sich der Hersteller selbst vorgestellt hatte. Erst zum Ende des vergangenen Quartals und damit erst vor wenigen Wochen sei eine Yield-Rate erreicht worden, die wirtschaftlich sinnvoll ist, sodass die Massenproduktion nach den entsprechenden Qualifizierungen begonnen werden konnte.

In den kommenden Wochen wird weiteres Feintuning an der 14-nm-Fertigung betrieben, sodass bis zum Ende des Jahres eine Ausbeute auf dem Niveau der 22-nm-Fertigung erreicht werden kann. Laut Marc Bohr habe auch die 22-nm-Fertigung einen schwachen Start gehabt, 14 nm hätte das allerdings nochmals deutlich unterboten. Für das erste Halbjahr des neuen Jahres verspricht Intel „multiple 14 nm product ramps“, dann soll die Technologie für eine breite Anwendung bereit sein.

Der Stand bei den Fabriken

Auch beim Thema der Fabriken war es in letzter Zeit still geworden, nachdem Intel im Jahr 2012 bereits groß die drei 14-nm-Fabs angekündigt hatte. Denn die Probleme bei der Fertigungstechnik hatten auch deutlich Auswirkungen auf die Zeitpläne für die Fabriken.

Derzeit sind lediglich die Fabs D1D als Entwickler-Fab für die 14-nm-Fertigung sowie der Neubau D1X auf dem Ronler Acres in Hillsboro, Oregon, in der Lage, die neuen 14-nm-Chips zu fertigen. Der zweite größere Fabrikkomplex in Arizona inklusive Fab 12 und 32 hängt laut Intel jedoch nur wenige Wochen hinterher, sodass dort in Kürze die Massenproduktion hochgefahren werden kann. Die zu Beginn des Jahres in Arizona fertiggestellte Fab 42 wird jedoch auch jetzt noch nicht zu Ende ausgerüstet und verbleibt als Komplex für die Zukunft – Stichwort 10-nm-Fertigung.

Die einzige nicht auf amerikanischem Boden stehende Fabrik für 14-nm-CPUs steht in Leixlip in der Nähe von Dublin, Irland. In der Fab 24 sollen jedoch erst ab dem kommenden Jahr die entsprechenden Chips vom Band laufen. 2015 werden neben „Broadwell“-Chips für Klassen auch die neuen „Skylake“-Prozessoren inklusive neuer Architektur in 14 nm erwartet, sodass entsprechend größere Kapazitäten benötigt werden.

Die Zukunft mit 10 nm und EUV

Als nächster Schritt in der Verkleinerung der Strukturen steht die 10-nm-Generation an. Marc Bohr betonte in den Pausengesprächen während der „Broadwell“-Präsentationen, dass der dort angepeilte Produktionsbeginn „on track“ sei. Denn zum Einsatz kommen die gleichen Werkzeuge wie bei 14 nm: Die Immersionslithografie inklusive ihrer 193 nm Lichtquelle, die nach aktuellen Stand zu ihrem letzten Einsatz starten wird. Danach werden die Strukturen zu klein, es muss eine neue Lösung her – die EUV-Lithografie.

An der Thematik rund um die neuen Belichtungsmaschinen auf Basis von ultraviolettem Licht (EUV) sind viele Unternehmen interessiert, werden doch alle Halbleiterhersteller über kurz oder lang nicht daran vorbeikommen. Da Intel eine Vorreiterrolle bei der Fertigung behalten will, kann es der Chipriese „kaum erwarten“, mit der Technik loszulegen, betonte Bohr mit einem freudig aufgeregten Lächeln im Gesicht. Sein Optimismus liegt unter anderem darin begründet, dass die entsprechenden Systeme in den vergangenen Monaten große Fortschritte erzielt haben, so der Manager.

Der Fab-Ausrüster ASML hat zusammen mit einer IBM-Forschungseinrichtung kürzlich das angepeilte Jahresziel in der Produktion von EUV-Wafern an einem Tag deutlich überschritten. Da Intel Anteile an ASML hält, werden diese Fortschritte, neben den eigenen Anstrengungen in diesem Bereich, am Ende früher oder später auch bei Intel von Nutzen sein.

Die dritte Baustelle, der 450-mm-Wafer, wird noch weiter ruhen. Aktuell stehen die Kosten in keinem Verhältnis zum Nutzen, sodass die Thematik erst nach der aktuellen Dekade wieder in Angriff genommen wird. Zwar heißt es, dass neben Intel, wo der Zeitrahmen für 450 mm große Wafer bis 2025 verlängert wurde, auch TSMC an einer frühen Einführung interessiert sei, doch auch dort wird es kaum vor Ende des Jahrzehnts zu schaffen sein. Denn die klassische Lithografie mit 193 nm kleiner Lichtquelle will kein Unternehmen mit den größeren Wafern kombinieren, stattdessen soll auf EUV gewartet werden.

Angesichts deren kommerzieller Nutzung frühestens bei 7-nm-Chips ab 2017/2018 ist die Kombination mit 450-mm-Wafern in den nächsten fünf Jahren faktisch vom Tisch. Diese Entwicklung können sich sowohl die Fabrik-Ausrüster wie Nikon und ASML trotz Finanzspritzen von Branchenriesen wie IBM, Intel, Samsung und TSMC als auch alle andere Hersteller von benötigten Werkzeugen nicht leisten. Denn nach aktuellem Stand müsste die Forschung und Entwicklung von den wenigen Schultern getragen werden, in der DRAM- und NAND-Speichersparte rund um die diversen anderen Halbleiterkonzerne sind die Ambitionen auf größere Wafer umzustellen nochmals weitaus geringer.